- •Усилители. Параметры и характеристики усилителей.

- •Основные характеристики усилительных устройств.

- •2. Линейные и нелинейные искажения в усилителях.

- •Шумы в электронных схемах.

- •4. Задание рабочей точки биполярного транзистора (бт) в схеме с фиксированным током базы. Основные расчетные соотношения.

- •5. Усилительные каскады на пт с общим истоком.

- •6. Обратные связи в усилителях.

- •7. Влияние обратной связи на параметры и характеристики усилителей.

- •8. Термостабилизация в усилительных каскадах.

- •12. Усилители постоянного тока (упт) на бт: способы устранения дрейфа нуля, согласование уровней постоянного напряжения между каскадами.

- •14. Методы борьбы с дрейфом нуля. Балансные (мостовые) схемы

- •15. Методы борьбы с дрейфом нуля. Дифференциальный каскад.

- •18.Операционные усилители.

- •19.Инвертирующий усилитель

- •20.Неинвертирующий усилитель

- •21. Применение оу для выполнения нелинейных операций.

- •24. Ключ на биполярном транзисторе.

- •25. Ключ на переключателе тока.

- •27. Комплементарный ключ

- •28. Семейства логических элементов.

- •32. Кмоп-логика.

- •33. Триггерная ячейка

- •41. Преобразователи кодов.

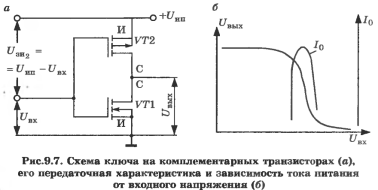

27. Комплементарный ключ

Ключ состоит из двух последовательно включенных МДП-транзисторов с каналами n- и p-типа. Транзистор VT1 является ключевым, его исток соединён с заземлённой шиной питания, а сток подсоединяется к стоку нагрузочного транзистора VT2.Подложка n-канального транзистора VT1 заземлена, а p-канального – подключена к положительному выводу источника Uип. Затворы обоих транзисторов объединены и являются входом ключа. При этом:

1. входное напряжение управляет не только ключевым, но и нагрузочным транзистором;2. управление является противофазным, напряжения на затворах транзисторов равны: Uзи1=Uвх, Uзи2=Uип-Uвх.

При нулевом потенциале затворов транзистор VT1 закрыт, а транзистор VT2 открыт и работает в линейной области, так как напряжение между затвором и истоком равно Uип. При этом ток в общей цепи определяется запертым транзистором VT1 и составляет величину Iост. Напряжение на выходе ключа практически равно Uип. При подаче на затворы напряжения, близкого к величине Uип, транзистор VT2 закрывается, а транзистор VT1 открывается. Ток в общей цепи по прежнему остаётся на уровне Iост, хотя состояния транзисторов изменились. На выходе формируется уровень напряжения, близкий к потенциалу земли. Уровни выходных напряжений имеют почти экстремальные значения близкие к нулю, близкое к напряжению источника питания, а перепад напряжений близок к Uип.

Ключи на КМДП-транзисторах имеют такие достоинства:

1. малая статическая мощность, потребляемая от источника питания;

2. высокая помехоустойчивость, обусловленная большим перепадом выходных напряжений;

3. широкий диапазон рабочих напряжений (3…15В);

4. широкий диапазон рабочих температур (-55…+125С);

5. высокое входное сопротивление (порядка 1012Ом);

6. простота сопряжения со слабочастотными источниками входного напряжения.Важнейшей особенностью комплементарных ключей является то, что они практически не потребляют энергию в обоих состояниях. Эти состояния можно назвать «открытым» или «закрытым» только условно – по отношению к одному из транзисторов. Такие схемы расходуют энергию только при переключении из одного логического состояния в другое (рис. 9.7, б).

28. Семейства логических элементов.

Наиболее широкое применение цифровые ключи нашли в логических элементах.

Логические элементы предназначены для реализации логических функций и являются одним из наиболее распространённых типов цифровых устройств, которые могут иметь самостоятельное применение либо входить в состав более сложных схем, выполненных на их основе, например триггеров, регистров, счётчиков, распределителей, сумматоров, дешифраторов. Как и все импульсные элементы, логические элементы делятся на потенциальные, импульсные и импульсно-потенциальные. Наиболее широкое распространение, особенно в интегральной микросхемотехнике, получили потенциальные логические элементы, отличительным признаком которых является:

1. наличие связи по постоянному току между входами и выходами микросхемы;

2. возможность быть управляемыми и управлять другими схемами с помощью сигналов как ограниченной, так и неограниченной длительности (импульсные и потенциальные сигналы).

Интегральные схемы потенциального типа являются самыми распространёнными микроэлектронными логическими схемами. Сложность выполняемых ими функций непрерывно возрастает. Сигналы на входах и выходах потенциальных логических элементов представляют собой высокий или низкий уровень напряжения, которым ставят в соответствие логические 1 и 0. В зависимости от кодирования сигналов различают положительную и отрицательную логику.

При положительной логике высокому уровню напряжения соответствует логическая единица U1вых, при отрицательной логике – наоборот: U0вых.

Логические интегральные микросхемы (ИМС) выпускаются в виде серии логических элементов. Логические ИМС, выполненные по биполярной технологии и схемотехнической реализации, делятся на следующие группы:

1. транзисторная логика с непосредственной связью между логическими элементами (ТЛНС);

2. транзисторная логика с резистивными связями между логическими элементами (ТРЛ);

3. резистивно-ёмкостная транзисторная логика (РЕТЛ);

4. диодно-транзисторная логика (ДТЛ);

5. транзисторно-транзисторная логика (ТТЛ);

5. эмиттерно-связанная логика (ЭСЛ);

6. интегрально-инжекционная логика (И2Л);

7.логика на полевых транзисторах.

С применением полевых транзисторов наибольшее развитие получили микросхемы КНДП-логики (КМОП-логики)

29. ТТЛ-, ТТЛШ-логика.

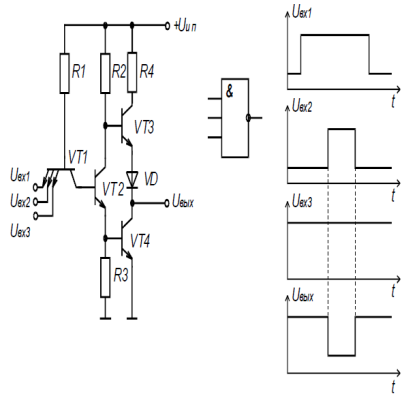

рис.1

Принципиальная электрическая схема, условное обозначение и временные диаграммы базового логического элемента ТТЛ, выполняющего операцию И-НЕ (элемент Шеффера), приведены на рис.1.

Схема базового элемента ТТЛ состоит из двух частей. Входная часть

реализует логическую функцию И с помощью VT1 и резистора R1. Выходная цепь реализует функцию НЕ и содержит сложный инвертор на транзисторах VT2…VT4. Сложный инвертор включает в свой состав простой инвертор (VT2, R2) и эмиттерный повторитель (VT3) с динамической нагрузкой (VT4), которая управляется эмиттерным током транзистора VT2. Простой инвертор в этой схеме (VT2) является фазоинверсным каскадом. Если транзистор VT2 открыт, то через него протекает большой эмиттерный ток, который является базовым током транзистора VT4. Транзистор VT4 открывается и переходит в режим насыщения, а транзистор VT3 закрывается

низким коллекторным потенциалом транзистора VT2. Выходное напряжение близко к нулю. Если транзистор VT2 закрыт, то транзистор VT3 открыт, поскольку потенциал базы транзистора VT3 близок к Uип, а транзистор VT4 закрыт. Выходное напряжение имеет высокий уровень и соответствует логической единице. При запирании транзистора VT4 ток рассасывания избыточных носителей из базы транзистора VT4 протекает через резистор R3 на землю. Резистор R4 ограничивает ток выходного каскада во время перехода схемы из открытого состояния в закрытое, когда транзистор VT3 уже открылся, а транзистор VT4 находится в режиме насыщения. Диод VD обеспечивает надежное запирание транзистора VT3 при напряжении на входе схемы равном нулю.

Рассмотрим

принцип работы схемы. Если хотя бы на

один из входов подано напряжение

логического нуля, то соответствующий

эмиттерный переход многоэмиттерного

транзистора VT1 открывается. Ток базы

транзистора

VT1 потечет во входную цепь, при этом ток

коллектора VT1 уменьшается, коллекторный

переход открывается и транзистор VT1

насыщается по коллекторной цепи.

Напряжение на базе транзистора VT2 равно

сумме входного напряжения и остаточного

напряжения на насыщенном транзисторе

VT1:

транзистора

VT1 потечет во входную цепь, при этом ток

коллектора VT1 уменьшается, коллекторный

переход открывается и транзистор VT1

насыщается по коллекторной цепи.

Напряжение на базе транзистора VT2 равно

сумме входного напряжения и остаточного

напряжения на насыщенном транзисторе

VT1:

.

.

Поэтому транзистор VT2 запирается, а транзистор VT3 и диод VD открываются высоким потенциалом коллектора транзистора VT2. Транзистор VT4 закрыт. Напряжение на выходе имеет высокий уровень и соответствует логический единице ("1").

Если на всех логических входах действуют высокие уровни напряжения, то эмиттерные переходы транзистора VT1 закрываются, VT1 работает в инверсном активном режиме. Ток от источника Uип через R1 и открытый коллекторный переход транзистора VT1 поступает в базу транзистора VT2.

Транзисторы VT2, VT4 открываются, и на выходе схемы имеется уровень напряжения, соответствующий логическому нулю ("0"). Транзистор VT3 и диод VD закрыты.

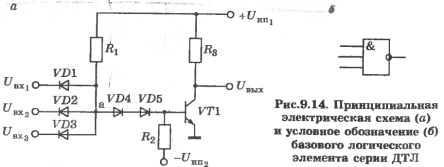

30. ДТЛ-логика.

Группа ДТЛ представляет собой сочетание диодных логических ячеек с транзисторным инвентором. Базовым логическим элементом всех серий ДТЛ является элемент Шеффера (элемент И-НЕ), реализующий операцию логического умножения с отрицанием.

Схема логического элемента ДТЛ представлена на рис. 9.14, а. Входные диоды VD1…VD3 и резистор R1 образуют входную логическую схему, выполняющую в положительной логике операцию И. Инвентор на транзисторе VT1 выполняет логическую операцию НЕ, усиливает и формирует сигналы на выходе до стандартного уровня. Смещающиеся диоды VD4 и VD5 предназначены для увеличения порога запирания и помехоустойчивости системы в закрытом состоянии, а резистор R2 и Uип2 обеспечивают оптимальную величину тока этих диодов.

Рассмотрим

принцип работы ДТЛ. Пусть на один (или

на все входы) подаётся низкий входной

сигнал логического нуля U0вх.

Входной диод (или все диоды) открывается

или оказывается замкнутым на общую

шину. От источника питания Uип1

через резистор R1,

открытый диод и входную цепь протекает

ток, при этом потенциал точки а уменьшается

до уровня прямого падения напряжения

на диоде

,

,

где Uпр - падение напряжения на открытом входном диоде.

При отсутствии VD4, VD5 потенциал базы транзистора VT1 был бы положительным, а транзистор – открыт. За счёт падения напряжения Uд.см на диодах VD4, VD5 потенциал базы транзистора отрицателен: -Uб=Ua-2Uд.см,

транзистор закрыт и на выходе схемы формируется высокий уровень напряжения логической единицы. Диоды смещения должны обладать большим сопротивлением, чтобы при относительно малом токе получить большое падение напряжения.

При одновременной подаче на все входы высокого уровня напряжение логической единицы диоды VD1…VD3 запираются. Транзистор VT1 переходит в область насыщения за счёт тока, протекающего от источника питания Uип1 через R1, смещающиеся диоды VD4, VD5 в базу транзистора. На выходе схемы появляется низкий уровень напряжения, близкий к нулю U0вых.

С целью уменьшения входного тока инвертора при действии на выходе системы напряжения логического нуля входную цепь усложняют, включая транзистор VT1 (рис. 9.15), который работает как эмиттерный повторитель и увеличивает усиление по току. А для улучшения выходных хар-к логического элемента выходной каскад строится по более сложной схеме.

За счёт падения напряжения на эмиттерном переходе транзистора VT1, работающего в активном (ненасыщенном) режиме, повторяется общая помехоустойчивость и уменьшается время переходных процессов при выключении и включении схемы. Сложный инвертор позволяет повысить нагрузочную способность. Схема обладает малым выходным сопротивлением в обоих состояниях, благодаря чему заряд и разряд паразитных ёмкостей в нагрузках следующего каскада протекают быстрей.

31. ЭСЛ-логика.

рис. 10.26, ж, принципиальная электрическая схема ЭСЛ

Цифровые схемы ЭСЛ составляют схемы на переключателях тока с объединёнными эмиттерами, обладающие по сравнению с другими типами цифровых схем наибольшим быстродействием и большой потребляемой мощностью.

Большое быстродействие ЭСЛ обеспечивается:

1. за счёт работы транзисторов в насыщенном (линейном) режиме;

2. за счёт применения на выходах схемы эмиттерных повторителей, ускоряющих процесс заряда и разряда нагрузочных ёмкостей;

3. за счёт ограничения перепада выходного напряжения, что приводит к снижению статической помехоустойчивости.

В зависимости от способа кодирования входной информации (1 и 0) одна и та же схема (рис.10.26 ж) может реализовать либо функции ИЛИ-НЕ, ИЛИ для положительной логики, либо функции И-НЕ, И для отрицательной логики.

Интегральные схемы на ЭСЛ используются в качестве элементной базы быстродействующих систем связи, вычислительной техники и радиоэлектронной аппаратуры. Их достоинства:

1. высокая помехоустойчивость;

2. высокое быстродействие при средней потребляемой мощности и сверхвысокое быстродействие при большой потребляемой мощности;

3. высокая стабильность динамических параметров при изменении рабочей температуры и напряжения питания;

4. высокий коэффициент разветвления (высокая нагрузочная способность);

5. возможность работы на низкоомные согласованные линии связи и нагрузки;

6. малая мощность переключения и независимость тока потребления от частоты переключения;

7. использование биполярной технологии изготовления.