Государственный комитет связи и информатизации Украины

____________________________________________________________

Украинская государственная академия связи им. А.С. Попова

Кафедра вычислительной техники и микропроцессоров

ИЗУЧЕНИЕ СТРУКТУРЫ,

ПРОЦЕССОРНОГО МОДУЛЯ

И ТЕХНОЛОГИЧЕСКИХ ОСОБЕННОСТЕЙ

МИКРОКОНТРОЛЛЕРА М68НС05J

ФИРМЫ MOTOROLA

Методическое руководство к лабораторной работе

по дисциплине

“Вычислительная техника и микропроцессоры”

для специальностей: 8. 092402, 7. 092402, 7. 092407, 09. 01

УТВЕРЖДЕНО

советом факультета

многоканальной

электросвязи

Протокол № 5

от 23.02.2001 г.

Одесса 2001

УДК 681.335.5(075)

План НМИ 2000/2001 уч. г.

Составитель – И.Е. Байдан

Рецензенты – Б.С. Владишевский

И.А. Киреев

Рассмотрены для изучения студентами в лаборатории особенности структуры, процессорного модуля и технологические атрибуты микроконтроллера М68НС05J фирмы MOTOROLA.

Приведены структурные схемы процессорного модуля и программнодоступных элементов микроконтроллера. Представлено домашнее задание и форма отчетности о лабораторной работе.

ОДОБРЕНО

на заседании кафедры

вычислительной техники

и микропроцессоров

и рекомендовано к печати.

Протокол № 5

от 22.01.2001 г.

1 Цель работы

Целью работы является изучение архитектуры, технологических особенностей, основных характеристик, некоторых отладочных средств, а также предварительное знакомство с системой команд 8-разрядных микроконтроллеров фирмы MOTOROLA.

2 Основные положения

Фирма MOTOROLA выпускает обширную номенклатуру 8-разрядных микроконтроллеров, которые входят в состав трех семейств М68НС705, М68НС708, М68НС711.

Микроконтроллеры семейства М68НС705, имеющие наиболее низкую стоимость и менее широкие функциональные возможности по сравнению с другими семействами, ориентированы на использование в относительно несложных и дешевых устройствах массового применения. Микроконтроллеры семейства М68НС708, выпуск которых начался в 1995 году, программно совместимы с семейством М68Н7С05, но имеют значительно более высокую производительность, увеличенный объем адресуемой памяти и расширенные функциональные возможности. Это семейство предназначено для замены микроконтроллеров М68НС705 в современных разработках. Наиболее широкую область применения имеют микроконтроллеры семейства М68НС711, которые сочетают достаточно высокое быстродействие и значительные функциональные возможности с большой номенклатурой реализованных на кристалле периферийных устройств. Таким образом, для каждого семейства существует своя сфера приложения, а в целом их состав обеспечивает потребности многих отраслей промышленности в надежных, высокоэффективных и недорогих устройствах управления и контроля.

Все модели микроконтроллеров семейства М68НС705 имеют одинаковое процессорное ядро, но отличаются объемом и типом используемой памяти, составом размещенных на кристалле периферийных устройств и рядом других характеристик (тактовая частота, температурный диапазон, тип корпуса и др.).

Рассмотрим функционирование одной из моделей семейства, а именно МС68НС705J, имеющей типовой состав периферийных устройств, а также основные особенности микроконтроллеров этого семейства.

Микроконтроллер МС68НС705J (рис. 2.1) содержит: 8-разрядное процессорное ядро, внутреннюю память общим объемом 2 Кбайта, которая включает программируемое ПЗУ (ППЗУ с однократной записью или с ультрафиолетовым стиранием) емкостью от 1836 до 1980 байтов и ОЗУ емкостью от 176 до 304 байтов, три параллельных 8-разрядных порта, синхронный и асинхронный последовательные порты, 16-разрядный таймер и ряд обслуживающих блоков.

Процессор выполняет обработку 8-разрядных операндов и реализует набор из 65 команд. Он содержит пять программно-доступных регистров: 8-разрядные аккумулятор А, индексный регистр X, регистр условий CCR и 13-разрядные регистр стека SP и программный счетчик PC. Регистры А, Х служат для хранения промежуточных данных. Кроме того, содержимое регистра Х используется в качестве индекса при индексной адресации.

Рисунок 2.1 – Программная модель микроконтроллера

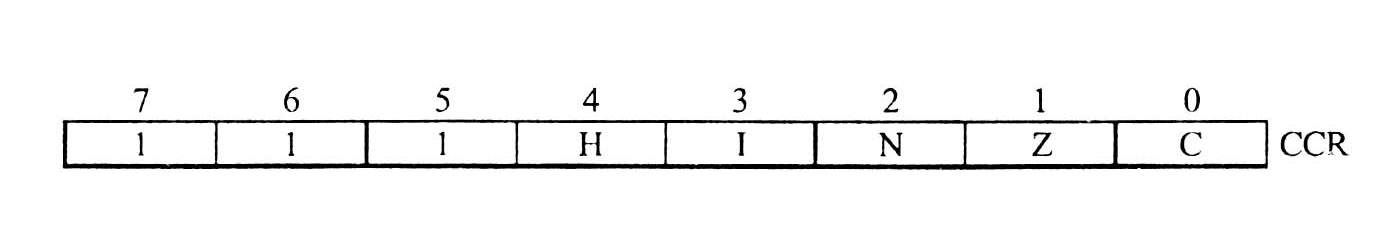

Регистр CCR (рис. 2.2) содержит значения пяти признаков:

С – признак переноса;

Z – признак нулевого результата;

N – признак знака;

I – признак разрешения прерывания;

Н – признак переноса между тетрадами, используемый при операциях над двоично-десятичными числами.

Рисунок 2.2 – Регистр флагов микроконтроллера

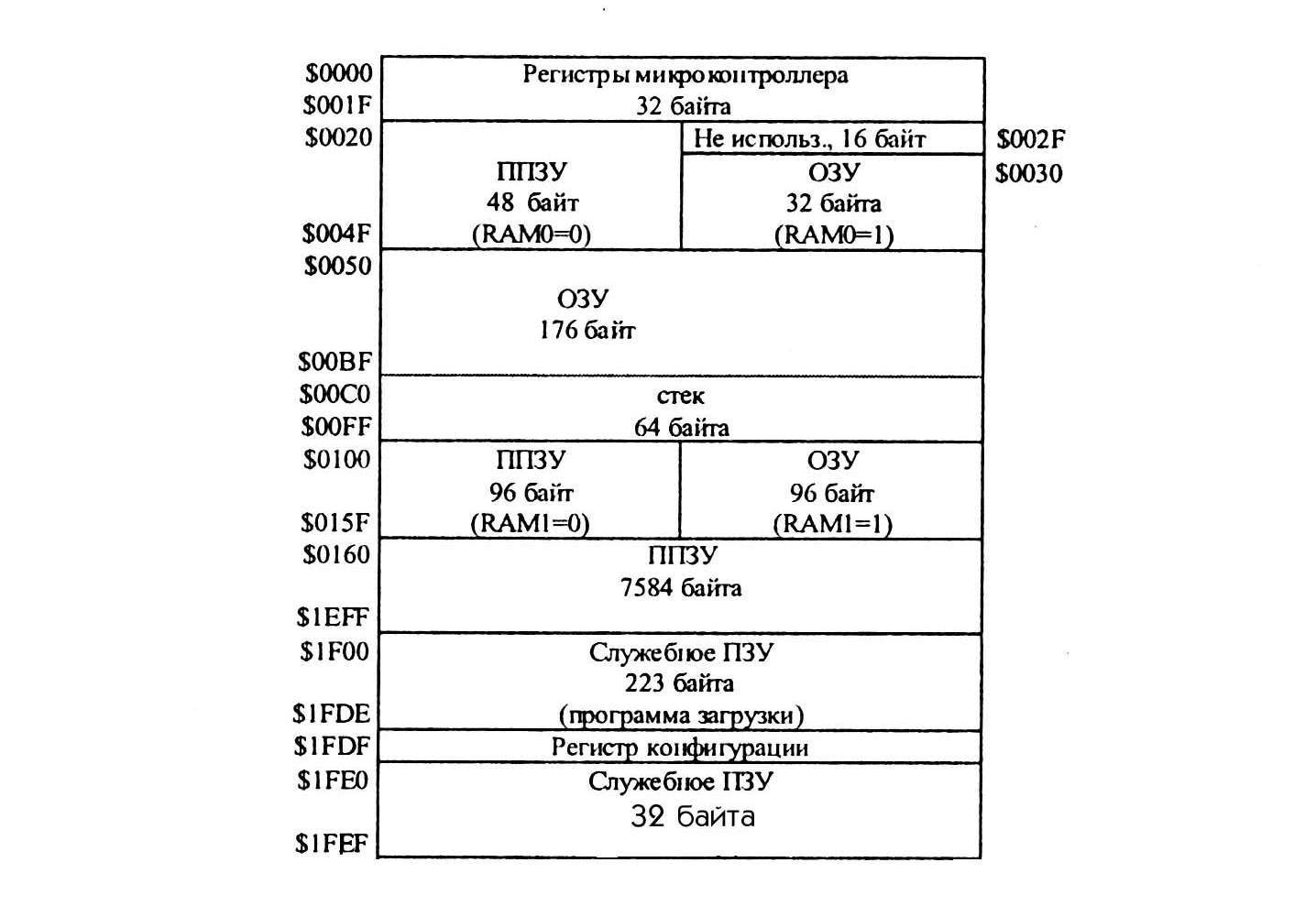

Регистры PC, SP могут адресовать до 8 Кбайтов внутренней памяти (адреса $0000-$1FFF). Распределение адресного пространства определяется картой памяти, приведенной на рис. 2.3.

Рисунок 2.3 – Карта памяти адресного пространства микроконтроллера

Младшие 32 адреса используются для обращения к внутренним регистрам микроконтроллера: регистрам параллельных портов PADR, PADDR, PBDR, PBDDR, PCDR, PCDDR, PDIR, регистрам синхронного последовательного порта (СПП) SPCR, SPSR, SPDR и асинхронного последовательного порта (АПП) SCCR1, 2, SCSR, SCDR, генератора синхросигналов (ГСС) BRR, регистрам таймера TCR, TSR, TCNTR, ICR, OCR и блоков обслуживания PROGR, COPCR, COPRST. При этом 16-разрядные регистры TCNTR, ICR, OCR занимают две позиции адресного пространства. Четыре адреса в этом разделе карты памяти остаются неиспользуемыми. Обращение к регистрам микроконтроллера осуществляется, как и к ячейкам памяти, путем формирования адреса соответствующей позиции в адресном пространстве.

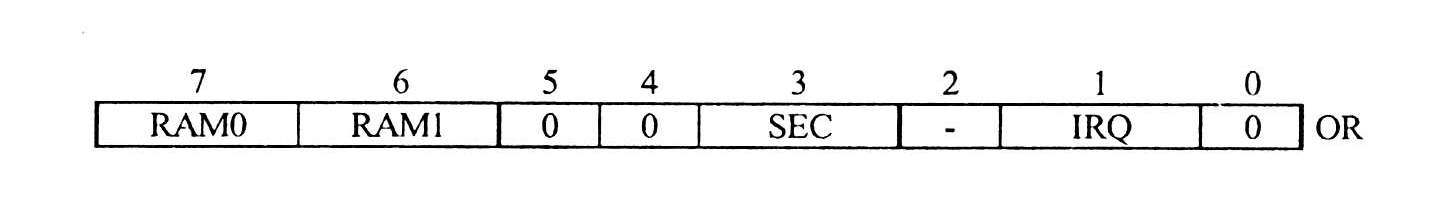

Адресация и объем внутренних ППЗУ и ОЗУ микроконтроллера определяются значениями битов RAMO-1 в регистре конфигурации OR (рис. 2.4). При значении RAMO=0 в адресном пространстве $0020-$004F располагаются 48 байтов ППЗУ, при RAMO=1 – 32 байта ОЗУ. При значении RAM1=0 адресное пространство $0100-015F занимают 96 байтов ППЗУ, а при RAM1=1 – 96 байт ОЗУ. Так обеспечивается возможность использования ОЗУ емкостью 176, 208, 272 или 304 байта за счет соответствующего сокращения емкости ППЗУ. Регистр конфигурации OR содержит также бит SEC, устанавливающий защиту содержимого ППЗУ от считывания, и бит IRQ, определяющий вид сигнала запроса прерывания на входе IRQ#.

Рисунок 2.4 – Регистр конфигурации микроконтроллера

В адресном пространстве ОЗУ располагаются ячейки стека, которые имеют адреса в диапазоне $00C0-$00FF. Эти ячейки адресуются с помощью 13-разрядного указателя стека SP, в котором семь старших разрядов имеют постоянное значение 0000011 (см. рис. 2.1). Шесть младших разрядов SP при установке микроконтроллера в начальное состояние принимают значение 111111, поэтому в исходном состоянии SP адресует ячейку ОЗУ с адресом $00FF. После записи байта в эту ячейку содержимое SP уменьшается на 1, адресуя следующую незаполненную ячейку стека. Таким образом, стек заполняется в направлении уменьшения адресов. При работе стека изменяются значения только шести младших разрядов SP, поэтому объем стека ограничен 64 байтами. В случае переполнения стека содержимое SP возвращается в исходное состояние $00FF, после чего цикл изменения его содержимого повторяется.

Адресное пространство $07FO…$07EF занято ячейками служебного ПЗУ, программируемого в процессе изготовления микроконтроллера. Это ПЗУ содержит программу, обеспечивающую загрузку содержимого ППЗУ при его программировании. Старшие 12 адресов $07F4…$07FF обеспечивают обращение к ячейкам ППЗУ, в которые заносятся адреса подпрограмм обслуживания прерываний в соответствии с поступающими внешними (IRQ#) или внутренними запросами.

Программирование ППЗУ осуществляется с помощью программаторов, например, серийно выпускаемого фирмой MOTOROLA программатора типа MC68HC05PGMR. Предварительно содержимое ППЗУ записывается в ячейки памяти микросхем РППЗУ емкостью 8 Кбайтов в соответствии с заданной адресацией (см. рис. 3). В процессе программирования производится перезапись содержимого микросхемы памяти во внутреннее ППЗУ микроконтроллера через асинхронный последовательный порт под управлением программы загрузки, расположенной в служебном ПЗУ. При этом осуществляется контроль правильности записи каждого байта путем его считывания и сравнения с введенным значением (верификация). Реализуется также режим перезаписи всего содержимого внутреннего ППЗУ во внешнюю память для последующего анализа или верификации. Бит SEC в регистре OR разрешает (при значении SEC=0) или запрещает (при SEC=1) процедуры верификации и перезаписи, выполняя защиту содержимого ППЗУ от несанкционированного доступа. При SEC=1 в модификации микроконтроллера, использующей внутреннее РППЗУ, запрещается его последующая перезагрузка новым содержимым. Значение бита SEC в регистре OR устанавливается в процессе загрузки ППЗУ и не изменяется при записи-считывании этого регистра в процессе работы микроконтроллера.

П еред

началом программирования микроконтроллера

на вывод Vп

подается напряжение +15 В, а в регистре

PROGR

(рис. 2.5) устанавливаются значения битов

LAT=1

(разрешение ввода адресов и данных для

программирования ППЗУ), PGM=1

(подключение к ППЗУ поданного напряжения

программирования Vnp). После окончания

программирования в регистр PROGR записывается

содержимое, в котором значения LAT=PGM=0.

еред

началом программирования микроконтроллера

на вывод Vп

подается напряжение +15 В, а в регистре

PROGR

(рис. 2.5) устанавливаются значения битов

LAT=1

(разрешение ввода адресов и данных для

программирования ППЗУ), PGM=1

(подключение к ППЗУ поданного напряжения

программирования Vnp). После окончания

программирования в регистр PROGR записывается

содержимое, в котором значения LAT=PGM=0.

Рисунок 2.5 – Регистр программирования микроконтроллера

Длительность такта машинного времени Тe=I/Ft определяется генератором тактовых импульсов (ГТИ), частота следования которых Ft задается подключаемым к выводам XTAL1-2 кварцевым или керамическим резонатором, RC-цепью или внешним импульсным генератором. При этом частота Ft вдвое меньше частоты внешнего резонатора или генератора Fg=2Ft=2/Тc. Максимальное значение Ft для данной модели составляет 4,2 МГц при напряжении питания Vп=5 В или 2 МГц при Vп=3,3 В. Ток источника питания в рабочем режиме при Vп=5 В, Ft=4,2 МГц не превышает 7 мА (типовое значение 4,7 мА), а при Vп=3,3 В, Ft=2,0 МГц не превышает 3 мА (типовое значение 1,9 мА).

Микроконтроллер имеет два режима функционирования с пониженным энергопотреблением. В режиме ожидания, который реализуется после поступления команды WAIT, прекращает работу процессор, но продолжают функционировать последовательные порты и таймер. При этом максимальный потребляемый ток снижается до 3 мА при Vп=5 В, Ft=4,2 МГц (типовое значение 1,7 мА) и до 1 мА при Vп=3,3 В, Ft=2,0 МГц (типовое значение 0,43 мА). Выход из режима ожидания происходит при поступлении запроса прерывания от таймера, СПП или АПП. В режиме останова, который реализуется после поступления команды STOP, прекращается работа процессора, таймера, СПП и АПП. При этом максимальный потребляемый ток уменьшается до 50 мкА при Vп=5 В (типовое значение 2 мкА) и до 20 мкА при Vп=3,3 В (типовое значение 0,84 мкА). Выход из этого режима происходит при поступлении внешнего запроса прерывания на вход IRQ# или внешнего сигнала сброса RESET#. При поступлении команд WAIT и STOP в регистре CCR устанавливается значение признака I=0, чтобы разрешить последующий выход из этих режимов по запросам прерывания.

Установка начального состояния всех регистров (процедура сброса RESET) производится в следующих случаях:

– включение напряжения питания Vп;

– поступление внешнего сигнала сброса RESET#=0;

– поступление сигнала сброса от блока контроля функционирования.

В процессе начальной установки в программный счетчик PC загружаются два байта, записанные в ячейки ППЗУ с адресами S1FFE – старший байт PCh, $1FFF – младший байт РС1. Эти байты являются адресом первой команды, выполняемой микроконтроллером после начальной установки. При включении питания требуется время 4064Тc для запуска ГТИ и установки начального состояния регистров, после чего начинается нормальная работа микроконтроллера. Для начальной установки по сигналу RESET# его длительность должна быть не меньше 8Тc.

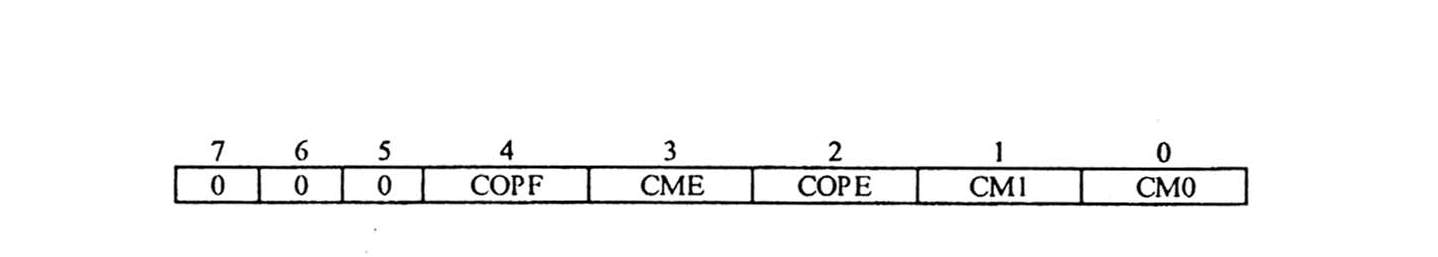

Блок контроля функционирования осуществляет контроль выполнения программы и частоты тактовых импульсов. Управление блоком производится с помощью регистра COPCR (рис. 2.6), отдельные биты которого имеют следующее назначение:

COPF – разрешает (при COPF=1) или запрещает (при COPF=0) работу блока контроля функционирования;

СМЕ – разрешает (при СМЕ=1) или запрещает (при СМЕ=0) контроль частоты тактовых импульсов;

СОРЕ – разрешает (при СОРЕ=1) или запрещает (при СОРЕ=0) контроль выполнения программы;

СМ 1–0 – определяют длительность интервалов времени Тt при контроле выполнения программы в соответствии с табл. 2.1. Чтение содержимого регистра COPCR вызывает установку значения бита COPF=0. Значения битов СМЕ, СОРЕ могут быть установлены только один раз, затем они могут только считываться. Биты СМ 1–0 принимают значение 0 только при сбросе микроконтроллера, затем они могут быть только считаны или установлены в 1.

Р исунок

2.6 – Регистр контроля функционирования

микроконтроллера

исунок

2.6 – Регистр контроля функционирования

микроконтроллера

Схема контроля частоты тактовых импульсов формирует выходной сигнал RESET и производит сброс микроконтроллера в начальное состояние (процедура RESET), если в течение времени Тx от ГТИ не поступил тактовый импульс. Длительность Тx составляет от 5 до 100 мкс, таким образом, сброс производится при частоте тактовых импульсов Ft < 200 кГц. Поэтому данную схему следует отключать установкой значения бита СМЕ=0, если предполагается работа микроконтроллера на низких частотах.

К

Таблица

2.1

– Длительность

интервалов времени

Тt

при контроле выполнения

программы

СМ1

СМ0

Интервал

времени Tt

0

0

1

1

0 1 0 1

32768Tc

(32768Tc)

x 4

(32768Tc)

x 16

(32768Tc)

x 64