- •Исходные данные:

- •Перечень вопросов, подлежащих разработке, и обязательного графического материала:

- •5. Мониторинг процесса выполнения курсовой работы

- •Содержание

- •Введение

- •Сложение/Вычитание целых чисел в дополнительном коде.

- •Минимальное число в группе чисел, представленных в формате с плавающей запятой.

- •Тестовые примеры

- •Сложение/Вычитание целых чисел в дополнительном коде.

- •Минимальное число в группе чисел, представленных в формате с плавающей запятой.

- •Функциональные схемы

Минимальное число в группе чисел, представленных в формате с плавающей запятой.

Вводим размер группы чисел.

Если размер = нулю, вернуться к пункту 1, иначе перейти к пункту 3.

Вводим первое число.

Проверяем число на нормализованность. если число не нормализвано, то вернуться к пункту 3, иначе перейти к пункту 5.

Пока Размер группы > 1:

Вводим следующее число.

Проверяем число на нормализованность. если число не нормализвано, то вернуться к пункту 5.1, иначе перейти к пункту 5.3.

Сравниваем знаковые разряды чисел. То число, чей знаковый разряд больше, меньше.

Если знаковые разряды равны, надо идентифицировать знак числа.

Если числа отрицательные:

Сравниваем порядки, то число, чей порядок больше, меньше.

Иначе, если порядки равны, сравниваем мантиссы. То число, чья мантисса больше, меньше.

Иначе, если мантиссы равны, минимальное остаётся прежним.

Если числа положительные:

Сравниваем порядки, то число, чей порядок меньше, меньше.

Иначе, если порядки равны, сравниваем мантиссы. То число, чья мантисса меньше, меньше.

Иначе, если мантиссы равны, минимальное остаётся прежним.

Размер группы := прежний размер -1, перейти к пункту 5.

Тестовые примеры

Сложение/Вычитание целых чисел в дополнительном коде.

0011 |

+3 |

0101 |

+5 |

1000 |

–8 |

Переполнение по модулю

0010 |

+2 |

0101 |

+5 |

0111 |

+7 |

1101 |

–3 |

1010 |

–6 |

10111 |

+7 |

0110 |

+6 |

1001 |

–7 |

1111 |

–1 |

Минимальное число в группе чисел, представленных в формате с плавающей запятой.

A:=1.101.11001

B:=1.110.11100

A(8) == B(8)

A(8) == 1

A(7…5) < B(7…5)

B < A

Min := B

A:=0.100.10001

B:=0.100.10010

A(8) == B(8)

A(8) == 0

A(7…5) == B(7…5)

A(4…0) < B(4…0)

A<B

Min:=A

Функциональные схемы

Функциональная схема. Операционный автомат.

Функциональная схема. Управляющий автомат с адресным ПЗУ, конвейерный вариант.

Таблица управляющих сигналов

m |

y1 |

y2 |

y3 |

y4 |

y5 |

y6 |

y7 |

y8 |

y9 |

y10 |

y11 |

y12 |

y13 |

y14 |

T1 |

T2 |

Ro |

Err0 |

Err1 |

Err2 |

0 |

|

0 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

|

|

1 |

1 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

2 |

1 |

1 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

3 |

1 |

1 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

4 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

5 |

|

0 |

1 |

0 |

|

0 |

1 |

1 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

6 |

|

0 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

1 |

0 |

1 |

0 |

0 |

0 |

7 |

|

0 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

1 |

0 |

0 |

1 |

8 |

|

0 |

|

|

|

0 |

|

0 |

1 |

1 |

1 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

9 |

|

0 |

|

|

|

0 |

|

0 |

0 |

1 |

1 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

10 |

|

0 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

11 |

|

0 |

|

|

1 |

1 |

|

0 |

|

|

0 |

|

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

12 |

|

0 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

1 |

0 |

13 |

1 |

1 |

|

|

|

0 |

|

0 |

|

|

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

14 |

|

0 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

1 |

0 |

15 |

|

0 |

|

|

0 |

1 |

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

16 |

|

0 |

|

|

|

0 |

|

0 |

|

|

0 |

|

|

|

0 |

1 |

1 |

0 |

0 |

0 |

17 |

|

0 |

|

|

|

0 |

|

0 |

|

0 |

1 |

1 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

Таблица заполнения управляющей памяти

|

|

ROM_1 |

ROM_2 |

||||

|

|

S |

Y |

H |

S |

q |

S’ |

d1 |

{m0} |

0 |

m0 |

2 |

0 |

0 |

0 |

|

g1(g1: d1, m1) |

|

|

|

0 |

1 |

1 |

n1 |

{m1} |

1 |

m1 |

0 |

1 |

0 |

11 |

|

g2(a: n8, d2) |

|

|

|

1 |

1 |

2 |

d2 |

{m0} |

2 |

m0 |

1 |

2 |

0 |

3 |

|

g2(b: d3, d4) |

|

|

|

2 |

1 |

5 |

d3 |

{m0} |

3 |

m0 |

3 |

3 |

0 |

3 |

|

g3(g3: d3, n2) |

|

|

|

3 |

1 |

4 |

n2 |

{m2} |

4 |

m2 |

X |

4 |

0 |

8 |

|

|

|

|

|

4 |

1 |

8 |

d4 |

{m0} |

5 |

m0 |

4 |

5 |

0 |

5 |

|

g4(g4: d4, n3) |

|

|

|

5 |

1 |

6 |

n3 |

{m3} |

6 |

m3 |

X |

6 |

0 |

7 |

|

|

|

|

|

6 |

1 |

7 |

n4 |

{m4} |

7 |

m4 |

X |

7 |

0 |

8 |

|

|

|

|

|

7 |

1 |

8 |

n5 |

{m5} |

8 |

m5 |

5 |

8 |

0 |

9 |

|

g5(OFL: n6, n7) |

|

|

|

8 |

1 |

10 |

n6 |

{m6} |

9 |

m6 |

X |

9 |

0 |

0 |

|

|

|

|

|

9 |

1 |

0 |

n7 |

{m7} |

10 |

m7 |

X |

10 |

0 |

0 |

|

|

|

|

|

10 |

1 |

0 |

n8 |

{m8} |

11 |

m8 |

7 |

11 |

0 |

15 |

|

g8(g8: d9, n10) |

|

|

|

11 |

1 |

12 |

n10 |

{m10} |

12 |

m10 |

6 |

12 |

0 |

13 |

|

g7(g7:d7, n9) |

|

|

|

12 |

1 |

14 |

d7 |

{m0} |

13 |

m0 |

6 |

13 |

0 |

13 |

|

g7(g7: d7, n9) |

|

|

|

13 |

1 |

14 |

n9 |

{m9} |

14 |

m9 |

7 |

14 |

0 |

15 |

|

g8(g8: d9, n10) |

|

|

|

14 |

1 |

12 |

d9 |

{m0} |

15 |

m0 |

8 |

15 |

0 |

15 |

|

g9(g9: d9, n11) |

|

|

|

15 |

1 |

16 |

n11 |

{m11} |

16 |

m11 |

9 |

16 |

0 |

17 |

|

g10(g10: d11, n12) |

|

|

|

16 |

1 |

18 |

n12 |

{m12} |

17 |

m12 |

8 |

17 |

0 |

15 |

|

g9(g9: d9, n11) |

|

|

|

17 |

1 |

16 |

d11 |

{m0} |

18 |

m0 |

10 |

18 |

0 |

0 |

|

g11(g11: d12, d1) |

|

|

|

18 |

1 |

19 |

d12 |

{m0} |

19 |

m0 |

11 |

19 |

0 |

19 |

|

g12(g12:d12, n13) |

|

|

|

19 |

1 |

20 |

n13 |

{m13} |

20 |

m13 |

12 |

20 |

0 |

22 |

|

g13(g13: n14, d14a) |

|

|

|

20 |

1 |

21 |

n14 |

{m14} |

21 |

m14 |

11 |

21 |

0 |

19 |

|

g12(g12: d12, n13) |

|

|

|

21 |

1 |

20 |

d14a |

{m0} |

22 |

m0 |

13 |

22 |

0 |

23 |

|

g14(g14a: d14b, n16) |

|

|

|

22 |

1 |

32 |

d14b |

{m0} |

23 |

m0 |

14 |

23 |

0 |

24 |

|

g14(g14b: d15, n15) |

|

|

|

23 |

1 |

31 |

d15 |

{m0} |

24 |

m0 |

15 |

24 |

0 |

25 |

|

g15(g15: d16a, d18a) |

|

|

|

24 |

1 |

28 |

d16a |

{m0} |

25 |

m0 |

16 |

25 |

0 |

26 |

|

g16(g16a: d16b, n16) |

|

|

|

25 |

1 |

32 |

d16b |

{m0} |

26 |

m0 |

17 |

26 |

0 |

27 |

|

g16(g16b: d17, n15) |

|

|

|

26 |

1 |

31 |

d17 |

{m0} |

27 |

m0 |

18 |

27 |

0 |

32 |

|

g17(g17: n16, n15) |

|

|

|

27 |

1 |

31 |

d18a |

{m0} |

28 |

m0 |

19 |

28 |

0 |

29 |

|

g18(g18a: d18b, n15) |

|

|

|

28 |

1 |

31 |

d18b |

{m0} |

29 |

m0 |

20 |

29 |

0 |

30 |

|

g17(g17b: d19, n16) |

|

|

|

29 |

1 |

32 |

d19 |

{m0} |

30 |

m0 |

21 |

30 |

0 |

32 |

|

g19(g19: n16, n15) |

|

|

|

30 |

1 |

31 |

n15 |

{m15} |

31 |

m15 |

X |

31 |

0 |

32 |

|

|

|

|

|

31 |

1 |

32 |

n16 |

{m16} |

32 |

m16 |

X |

32 |

0 |

33 |

|

|

|

|

|

32 |

1 |

33 |

n17 |

{m17} |

33 |

m17 |

X |

33 |

0 |

0 |

|

|

|

|

|

33 |

1 |

0 |

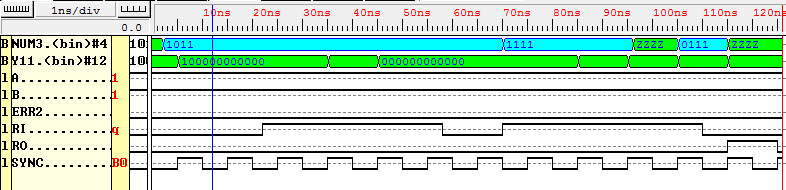

Моделирование схемы в Xilinx

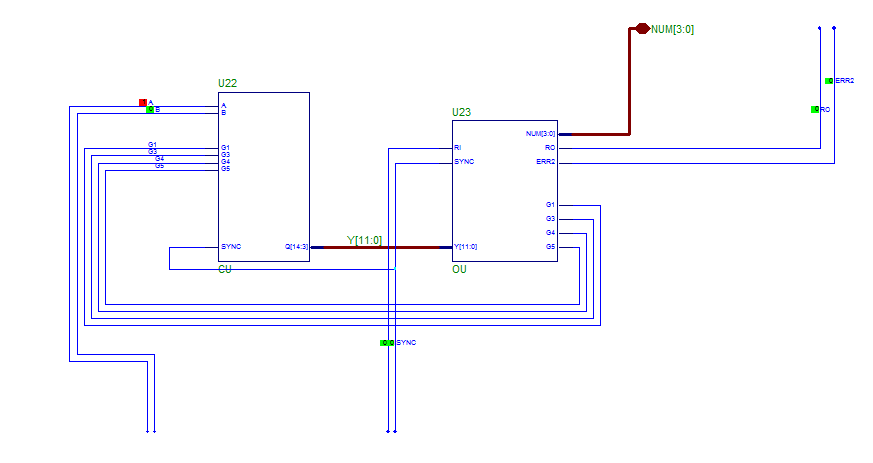

Общая схема

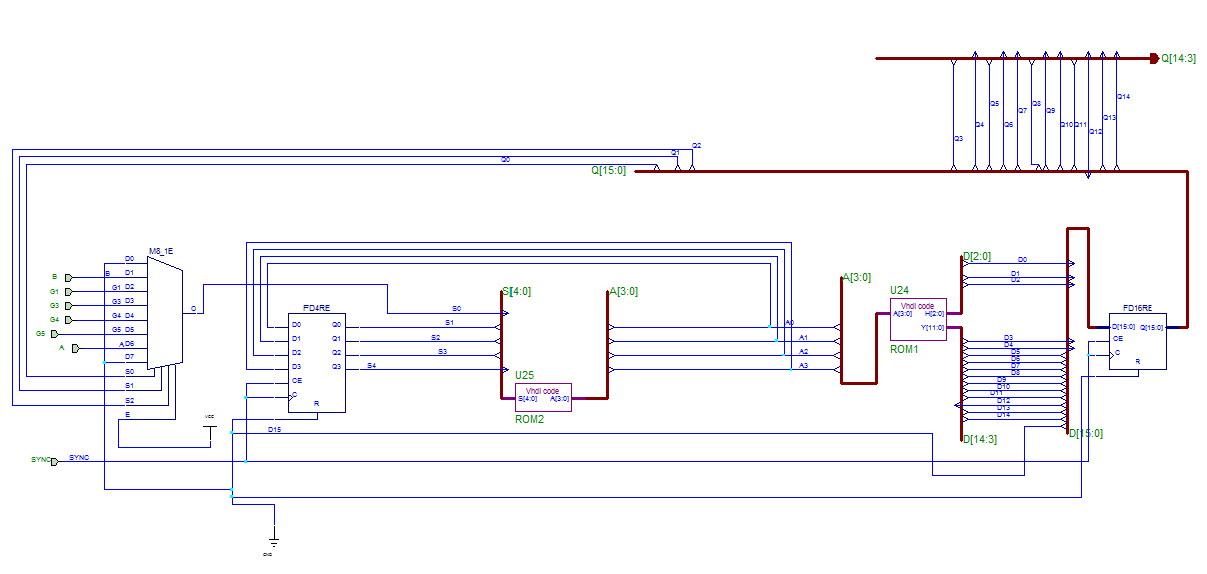

Управляющий автомат

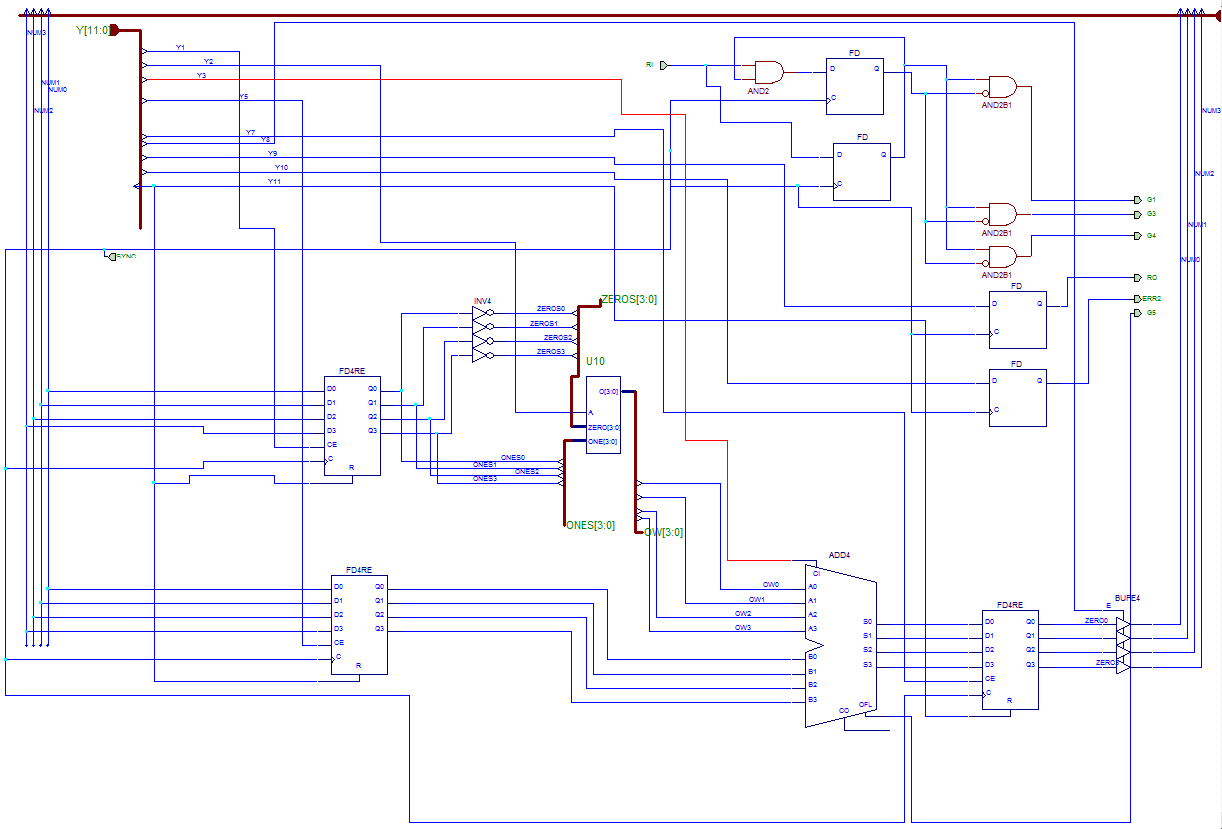

Операционный автомат |

Литература

Арифметика Антик М. И.

«Синхронные цифровые автоматы» Антик М. И. –М: МИРЭА, 2006-99 стр.

«Разработка цифровых устройств на основе ПЛИС Xilinx с применением языка VHDL» Тарасов И.Е М: Горячая линия-Телеком, 2005- 253 стр.