- •Понятие архитектуры эвм. Эволюция универсальных эвм. Поколения эвм. Элементная база эвм.

- •Основы классификации эвм. Классификационные признаки. Принципы устройства последовательной эвм (архитектура фон Неймана). Технические показатели эвм.

- •Архитектура универсальной эвм с последовательным выполнением команд. Функциональное назначение, физические принципы действия и организация основных блоков.

- •Серия ibm-совместимых пэвм (ibm pc). Основные современные конфигурации. Технические показатели и характеристики. Другие типы аппаратных платформ пэвм.

- •Блочно-функциональное устройство персонального компьютера с магистральной организацией ( общей системной шиной ). Понятие открытой архитектуры.

- •Внутренние интерфейсы эвм. Системные и локальные шины. Контроллер шины. Иерархическая организация шин.

- •Контроллер шины

- •Основы систем счисления. Методы представления чисел и операции в позиционных системах счисления с различным основанием. Системы счисления в эвм.

- •Внутренняя организация числовых и символьных данных в эвм. Машинные форматы числовых данных пэвм. Стандарты кодировок символьной информации (ascii, unicode) и десятичных чисел (код bcd).

- •Кодировка ascii

- •Кодировка (encoding) Юникод - Unicode

- •Машинный формат с фиксированной точкой (Fixed Point Representation). Специальные коды для представления знаковых целых двоичных чисел и операций с ними(прямой, обратный, дополнительный).

- •11. Машинный формат с плавающей точкой (Float Point Representation). Параметры форматов сопроцессора intel (fpu 80x87).

- •Функционально-логическая организация микропроцессоров серии intel 80x86. Основные блоки и устройства: - назначение, функции, принципы действия. Режимы работы мп и способы адресации операндов.

- •Программная модель мп Intel (ia-32). Система регистров мп. Назначение, типы регистров. Регистры прикладного программиста. Флаги.

- •Специальные типы регистров защищенного режима мп (ia-32): управляющие, отладки, системные адресные регистры. Селекторы сегментов: - организация в разных режимах.

- •Регистровая (локальная) память мп. Сверхбыстрая буферная память. Внешний и внутренний кэш: - алгоритмы обслуживания. Стековая (магазинная) память. Fifo - буфера.

- •Специализированные процессоры. Числовой арифметический сопроцессор intel 80x87(fpu). Программная (регистровая) модель. Форматы данных. Система команд.

- •Оперативная (основная) память эвм (озу). Назначение, программная модель. Элементная база озу.

- •Системы памяти в эвм. Иерархия запоминающих устройств. Оперативная и долговременная внешняя память.

- •Типы запоминающих устройств внешней памяти эвм. Методы моделирования цифровых (двоичных) данных. Общая организация носителей данных, технические характеристики.

- •Программная модель памяти эвм. Иерархическая структура памяти. Концепция виртуальной памяти. Страничное распределение памяти.

- •21. Сегментная и страничная модели оперативной памяти (на платформе Intel). Системные адресные регистры цп, таблицы дескрипторов сегментов.

- •22.Специальные типы организации памяти: - стековая (магазинная) память, fifo-буфера. Сегмент стека, команды цп для работы со стеком

- •23. Физическая организация внешней долговременной памяти эвм (дзу). Дисковая магнитная память.

- •24. Постоянные запоминающие устройства (пзу). Базовая система ввода-вывода (bios) и ее функции. Конфигурационная память (cmos), ее свойства и назначение. Часы реального времени (rtc).

- •25. Интерфейсы пэвм. Системные и локальные шины. Интерфейсы дисковых накопителей и периферийных устройств. Стандарты и технические характеристики.

- •Интерфейс scsi

- •26. Организация взаимодействия элементов эвм под управлением цп. Цикл выполнения команд. Циклы шины. Система прерываний. Типы прерываний

- •27. Система прерываний эвм. Назначение, роль и место в общей организации управления и взаимодействия в эвм. Типы прерываний.

- •28. Обслуживание запросов внешних устройств. Аппаратные (асинхронные) прерывания. Контроллер прерываний pic. Линии запросов на прерывание - irq. Исключительные ситуации цп.

- •29. Программные (синхронные) прерывания, команды прерывания мп. Сервисы bios, как программные прерывания.

- •30. Процедуры обработчиков прерывания Таблицы дескрипторов (векторов) прерываний в защищенном и реальном режимах работы процессора intel.

- •31. Организация ввода-вывода. Принципы обмена информацией цп с внешними устройствами. Порты ввода-вывода. Устройства ввода: - клавиатура, мышь. Динамик pc.

- •32. Видеоподсистема пэвм. Принципы формирования изображений. Элементы видеоподсистемы: - монитор, видеоконтроллер, видеопамять. Видеорежимы.

- •33. Периферийное оборудование пэвм. Обзор основных устройств: - принципы действия, функциональное назначение, интерфейс с компьютером.

- •34. Системный (ассемблерный) отладчик ос ms-dos - debug. Интерактивные типы отладчиков.

- •35. Ассемблер для микропроцессоров с архитектурой intel 80x86. Общая характеристика языка, основные особенности и возможности. Инструментальные системы для разработки программ на языке Ассемблера.

- •36. Алфавит языка Ассемблер. Базовые синтаксические элементы (лексемы) языка. Предложения: - команды, директивы, комментарии. Синтаксис команд и директив. Резервированные идентификаторы.

- •37. Структура программ на языке Ассемблер. Программные сегменты. Типы, описание, назначение. Макроопределения. Специальные директивы компилятора. Определение именованных констант.

- •Include - Вложить другой файл

- •38. Форматы загрузочных (исполняемых) модулей типа *.Exe и *.Com. Загрузка программ, инициализация сегментных регистров. Префикс программного сегмента. (psp).

- •39. Типы данных Ассемблера. Константы. Директивы описания и инициализации данных, директивы эквивалентности (описания констант). Формат директив.

- •40. Директивы описания сегментов. Процедуры в Ассемблере. Вызовы и возвраты (дальние и ближние).

- •Система команд Ассемблера. Основные типы команд и их классификация. Синтаксис (формат записи) команд. Способы адресации операндов.

- •Методы адресации

- •Команды пересылки данных. Операции со стековой памятью. Арифметические команды Ассемблера. Команды пересылки данных

- •Арифметические команды

- •Логические команды. Команды сдвига. Команды прямой манипуляции с битами. Логические команды

- •44. Команды программной передачи управления. Команды переходов

- •Команды обработки строк. Префиксы повторения.

- •Организация циклов в Ассемблере. Команды управления циклами. Организация циклов

- •Режимы адресации операндов в командах Ассемблера. Косвенная адресация. Модификация адресов, и индексирование.

- •48. Команды управления состоянием микропроцессора.

- •Моделирование структурных типов данных в Ассемблере (строки, векторы, матрицы, записи, структуры). Организация обработки структурных данных.

- •Двухмерные массивы

- •Структуры

- •Описание шаблона структуры

- •Определение данных с типом структуры

- •Объединения

- •Описание записи

- •Определение экземпляра записи

- •Функциональное обслуживание устройств на уровне ос ms-dos. Прерывания dos. Программный интерфейс ms-dos - прерывание int 21h. Основные группы функций. Прерывания dos

- •Получение системной информации.

- •Символьный ввод/вывод.

- •Работа с файловой системой.

- •Управление программами.

- •Управление памятью.

- •Связь с драйверами устройств.

21. Сегментная и страничная модели оперативной памяти (на платформе Intel). Системные адресные регистры цп, таблицы дескрипторов сегментов.

Сегментная:

Память для программы делится на непрерывные области памяти, называемые сегментами.

Сегменты - это логические элементы программы.

Сама программа может обращаться только к данным, которые находятся в этих сегментах.

Сегмент представляет собой независимый, поддерживаемый на аппаратном уровне блок памяти.

Сегментация - механизм адресации, обеспечивающий существование нескольких независимых адресных пространств как в пределах одной задачи, так и в системе в целом для защиты задач от взаимного влияния.

Для микропроцессоров Intel принят особый подход к управлению памятью. Каждая программа в общем случае может состоять из любого количества сегментов, но непосредственный доступ она имеет только к 3 основным сегментам: кода, данных и стека и к дополнительным сегментам данных (всего 3).

Операционная система (! а не сама программа) размещает сегменты программы в ОП по определенным физическим адресам, а значения этих адресов записывает в определенные места, в зависимости от режима работы микропроцессора:

· в реальном режиме адреса помещаются непосредственно в сегментные регистры (cs, ds, ss, es, gs, fs);

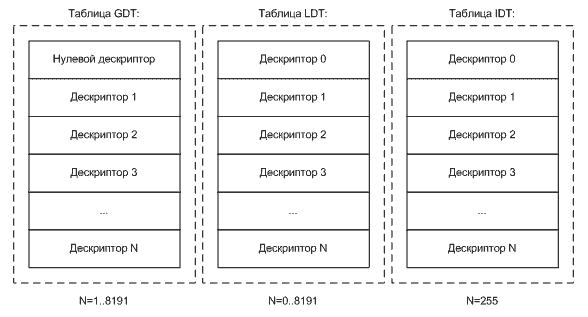

· в защищенном режиме - в специальную системную дескрипторную таблицу (Элементом дескрипторной таблицы является дескриптор сегмента. Каждый сегмент имеет дескриптор сегмента -8 байт. Существует три дескрипторные таблицы. Адрес каждой таблицы записывается в специальный системный регистр).

Для доступа к данным внутри сегмента обращение производится относительно начала сегмента линейно, т.е. начиная с 0 и заканчивая адресом, равным размеру сегмента. Этот адрес называется смещением (offset).

Таким образом, для обращения к конкретному физическому адресу ОП необходимо определить адрес начала сегмента и смещение внутри сегмента.

Физический адрес принято записывать парой этих значений, разделенных двоеточием

segment : offset

Например, 0040:001Ch; 0000:041Ch; 0020:021Ch; 0041:000Ch.

Каждый сегмент описывается дескриптором сегмента.

ОС строит для каждого исполняемого процесса соответствующую таблицу дескрипторов сегментов и при размещении каждого из сегментов в ОП или внешней памяти в дескрипторе отмечает его текущее местоположение (бит присутствия).

Дескриптор содержит поле адреса, с которого сегмент начинается и поле длины сегмента. Благодаря этому можно осуществлять контроль

1) размещения сегментов без наложения друг на друга

2) обращается ли код исполняющейся задачи за пределы текущего сегмента.

В дескрипторе содержатся также данные о правах доступа к сегменту (запрет на модификацию, можно ли его предоставлять другой задаче) Þ защита.

Достоинства:

1) общий объем виртуальной памяти превосходит объем физической памяти

2) возможность размещать в памяти как можно больше задач (до определенного предела) Þ увеличивает загрузку системы и более эффективно используются ресурсы системы

Недостатки:

1) увеличивается время на доступ к искомой ячейке памяти, т.к. должны вначале прочитать дескриптор сегмента, а потом уже, используя его данные, можно вычислить физический адрес (для уменьшения этих потерь используется кэширование - дескрипторы, с которыми работа идет в данный момент размещаются в сверхоперативной памяти - в специальных регистрах процессора);

2) фрагментация;

3) потери памяти на размещение дескрипторных таблиц

4) потери процессорного времени на обработку дескрипторных таблиц.

Страничная модель:

Это надстройка над сегментной моделью.

ОП делится на блоки фиксированного размера 4 Кб (должно быть число, кратное степени двойки, чтобы операции сложения можно было бы заменить на операции конкатенации).

Каждый такой блок называется страницей.

Их число 1.048.576 Þ 4 Гб адресуемой памяти.

Основное применение этой модели связано с организацией виртуальной памяти.

Для того, чтобы использовать для работы программ пространство памяти большее, чем объем физической памяти используется механизм виртуальной памяти.

Суть его заключается в том, что у микропроцессора существует возможность по обмену страницами памяти с жестким диском. В случае, если программа требует памяти больше, чем объем физической памяти, редко используемые страницы памяти записываются на жесткий диск в специальный файл виртуальной памяти (файл обмена, или страничный файл, или файл подкачки, чаще swap-файлом, подчеркивая, что страницы этого файла замещают друг друга в ОП).

Замечание. В некоторых ОС выгруженные страницы располагаются не в файле, а в специальном разделе диска, например, в ОС UNIX есть специальный раздел, но могут использоваться и файлы, если не достаточно объема раздела.

В настоящее время файл подкачки может динамически изменять свой размер в зависимости от потребностей системы.

Для i486 и Pentium размер возможной виртуальной памяти может достигать 4 Тб (терабайт).

Обратим внимание на то, что программа также разбивается на фрагменты - страницы. Все фрагменты программы одинаковой длины, кроме последней страницы.

Говорят, что память разбивается на физические страницы, а программа - на виртуальные страницы.

Трансляция (отображение) виртуального адресного пространства задачи на физическую память осуществляется с помощью таблицы страниц.

Для каждой текущей задачи создается таблица страниц.

Диспетчер памяти для каждой страницы формирует соответствующий дескриптор. Дескриптор содержит так называемый бит присутствия.

Если он = 1, это означает, что данная страница сейчас размещена в ОП.

Если он = 0, то страница расположена во внешней памяти.

Защита страничной памяти основана на контроле уровня доступа к каждой странице.

Каждая страница снабжается кодом уровня доступа (только чтение; чтение и запись; только выполнение). При работе со страницей сравнивается значение кода разрешенного уровня доступа с фактически требуемым. При несовпадении работа программы прерывается.

Страничная модель памяти поддерживается только в защищенном режиме работы микропроцессора.

Основное достоинство страничного способа распределения памяти -

минимально возможная фрагментация (эффективное распределение памяти).

Недостатки:

1) потери памяти на размещение таблиц страниц

2) потери процессорного времени на обработку таблиц страниц (диспетчер памяти).

3) Программы разбиваются на страницы случайно, без учета логических взаимосвязей, имеющихся в коде Þ межстраничные переходы осуществляются чаще, чем межсегментные + трудности в организации разделения программных модулей между выполняющими процессами

Адресные регистры (Address register) применяются для хранения адреса (или его части) ячейки в оперативной памяти. Этот адрес может участвовать в арифметических и логических операциях процессора. Во многих современных процессорах разделение регистров на адресные и регистры данных весьма условно: и в тех, и в других могут находиться как адрес, так и данные, а АЛУ не делает различий между адресом и данными.

Существуют следующие адресные регистры:

Базовый регистр (Base) – служит для указания начального адреса объекта в памяти при операциях с массивами и неявной адресации.

Указатель стека (Stack Pointer) – неявно используется в некоторых процессорах (в частности, Intel и Motorola) для организации работы со стеком.

Указатель базы (Base Pointer) – используется для удобства доступа к данным в стеке, которые не находятся в его вершине (например, параметры подпрограмм, переменные с модификатором auto в программах на Си и т.д.)

К адресным регистрам можно отнести регистры сегментного и страничного разделения памяти, а также селекторы сегментов.

Системные регистры центрального процессора Системные регистры (System registers) предназначены для временного хранения операндов (смотри п. D.1.) и результатов вычислений. но не смотря на свое "единое" предназначение, эти устройства различаются по своим функциям. По ним регистры можно разделить на регистры данных, аккумуляторы, адресные и сегментные регистры, регистры стеков, указателями и счетчики команд, регистры флагов (или, как их раньше называли, слово состояния программы, Program Status Word) и прочие. Регистры данных (Data Register) применяется для хранения промежуточных данных, участвуют в арифметических и логических операциях процессора. Аккумулятор, базовые и индексные регистры также можно использовать в качестве регистров данных.

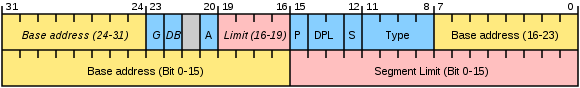

Дескриптор сегмента — служебная структура в памяти, которая определяет сегмент. Длина дескриптора равна восьми байтам.

Структура сегментного дескриптора

База (жёлтые поля, 32 бита) — начало сегмента в линейной памяти

Лимит (красные поля, 20 бит) — (размер сегмента в байтах)-1 (База+Лимит = линейный адрес последнего байта)

Права доступа (синие поля, 12 бит) — флаги, определяющие наличие сегмента в памяти, уровень защиты, тип, разрядность + один пользовательский флаг