- •Базовая структура компьютера

- •Процессор, оперативная память, устройства ввода-вывода, внешняя память, шины.

- •Представление информации. Целые, вещественные, символьные данные.

- •Структуры машинных команд. Трех-, двух-, одноадресные системы команд процессоров.

- •Стек. Его использование и аппаратная поддержка.

- •Risc-процессоры.

- •Cisc-процессоры. Микрокомандный уровень архитектуры.

- •Пример базовой архитектуры - pdp-11

- •Структура процессора. Регистры и их назначение.

- •2.2. Архитектура с общей шиной. Адресное пространство.

- •2.3. Форматы команд.

- •2.3.1. Двух-, одно- и безадресные команды. Примеры

- •2.3.2. Организация ветвлений и циклов. Регистр состояния процессора.

- •2.4. Методы адресации.

- •2.4.1 Прямые методы адресации.

- •2.4.2. Косвенные методы адресации.

- •2.4.3. Использование счетчика команд и указателя стека в методах адресации.

- •2.4.4. Позиционно-независимые программы и методы адресации.

- •2.5. Организация ввода-вывода.

- •2.5.1. Контроллеры устройств. Регистры устройств и их адресация.

- •2.5.2. Ввод-вывод по опросу флага готовности.

- •2.5.3. Прерывания устройств и их обработка.

- •2.5.4. Система приоритетов в обработке прерываний.

- •2.5.5. Ввод-вывод с использованием механизма прерываний.

- •2.5.6. Устройства с блочной передачей данных.

- •2.5.7. Прямой доступ к памяти и его использование для ввода-вывода.

- •2.6. Синхронные прерывания (исключительные ситуации) и их обработка.

- •3. Шинная архитектура

- •3.1 Структура шин. Подшины адреса, данных, управления. Ширина шины.

- •3.2. Синхронизация шины. Синхронные и асинхронные шины.

- •3.3. Временные диаграммы операций обмена по шинам.

- •3.4 Арбитраж шины.

3.2. Синхронизация шины. Синхронные и асинхронные шины.

Шины можно разделить на две категории в зависимости от их синхронизации. Синхронная шина содержит линию, которая запускается кварцевым генератором. Сигнал на этой линии представляет собой меандр с частотой обычно от 5 до 100 МГц. Любое действие шины занимает целое число так называемых циклов шины. Асинхронная шина не содержит задающего генератора. Циклы шины могут быть любой требуемой длины и необязательно одинаковы по отношению ко всем парам устройств.

Если шина синхронная, то она включает сигналы синхронизации, которые передаются по линиям управления шины, и фиксированный протокол, определяющий расположение сигналов адреса и данных относительно сигналов синхронизации. Все на шине должно происходить с одной и той же частотой синхронизации, поэтому из-за проблемы перекоса синхросигналов, синхронные шины не могут быть длинными. Обычно шины процессор-память синхронные.

Асинхронная шина, с другой стороны, не тактируется. Вместо этого обычно используется старт-стопный режим между источником и приемником данных на шине. Эта схема позволяет гораздо проще приспособить широкое разнообразие устройств и удлинить шину без беспокойства о перекосе сигналов синхронизации и о системе синхронизации. Если может использоваться синхронная шина, то она обычно быстрее, чем асинхронная, из-за отсутствия накладных расходов на синхронизацию шины для каждой транзакции. Выбор типа шины (синхронной или асинхронной) определяет не только пропускную способность, но также непосредственно влияет на емкость системы ввода/вывода в терминах физического расстояния и количества устройств, которые могут быть подсоединены к шине. Шины ввода/вывода обычно асинхронные.

3.3. Временные диаграммы операций обмена по шинам.

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных;

Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который будет прочитан процессором.

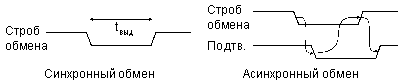

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения (рис.):

При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

Какой тип обмена быстрее, синхронный или асинхронный? Ответ на этот вопрос неоднозначен. С одной стороны, при асинхронном обмене требуется какое-то время на выработку, передачу дополнительного сигнала и на его обработку процессором. С другой стороны, при синхронном обмене приходится искусственно увеличивать длительность строба обмена для соответствия требованиям большего числа исполнителей, чтобы они успевали обмениваться информацией в темпе процессора. Поэтому иногда в магистрали предусматривают возможность как синхронного, так и асинхронного обмена, причем синхронный обмен является основным и довольно быстрым, а асинхронный применяется только для медленных исполнителей.