Повышение быстродействия параллельных сумматоров.

Для обеспечения высокого быстродействия параллельные сумматоры должны строиться на элементах, обладающих высоким быстродействием.

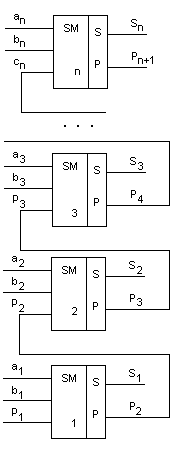

Трудности

в достижении высокого быстродействия

сумматора, построенного по схеме на

рис. 9.64, связаны с тем, что процесс

распространения переносов в нем имеет

последовательный характер. Импульс

переноса в каждом разряде формируется

после того, как будет сформирован и

передан импульс переноса из предыдущего

разряда. В наиболее неблагоприятном

случае возникший в младшем разряде

перенос может последовательно вызывать

переносы во всех остальных разрядах.

При этом время передачи переносов![]() ,где

,где

![]() -

задержка распространения переноса в

одном разряде.

-

задержка распространения переноса в

одном разряде.

рис 9.64

Уменьшение

![]() достигается

следующими приемами.

достигается

следующими приемами.

1. При построении схем одноразрядных сумматоров стремятся к уменьшению числа элементов в цепи между входом, на который поступает импульс переноса , и выходом, на котором формируется передаваемый в следующий разряд импульс переноса . Этот принцип реализован в схеме сумматора на рис. 9.62, в которой цепь от к содержит один логический элемент И-ИЛИ-НЕ.

2. В цепях от к применяют элементы с повышенным быстродействием.

3. Схемы сумматоров следует строить таким образом, чтобы сигналы с выхода каждого логического элемента в цепи от pi к pi+i поступали на возможно меньшее число других логических элементов, так как присоединение каждого дополнительного элемента к той или иной точке цепи переносов, как правило, приводит к увеличению паразитной емкости, удлинению фронтов сигналов и, следовательно, к увеличению задержки распространения сигнала и снижению быстродействия сумматора.

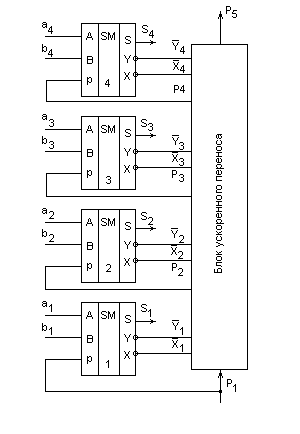

4.

Применяют устройства формирования

переносов в параллельной форме. В

показанном на рис. 9.65 сумматоре с помощью

устройства, называемого блоком

ускоренного переноса,

производится формирование переносов

в параллельной форме, т. е. одновременно

для всех разрядов. Переносы из этого

блока поступают во все разрядные

сумматоры одновременно. При этом

разрядные сумматоры не содержат цепей

формирования переносов, они формируют

только сумму s, и величины

![]() и

и

![]() ,

для .получения которых переносы не

требуются. Эти величины

и

необходимы

для формирования переносов в блоке

ускоренного переноса, они определяют

следующие ситуации:

,

для .получения которых переносы не

требуются. Эти величины

и

необходимы

для формирования переносов в блоке

ускоренного переноса, они определяют

следующие ситуации:

![]() означает,

что в i-м

разряде перенос

в

следующий (i+1)-й

разряд необходимо формировать независимо

от поступления в данный разряд переноса

из предыдущего разряда;

означает,

что в i-м

разряде перенос

в

следующий (i+1)-й

разряд необходимо формировать независимо

от поступления в данный разряд переноса

из предыдущего разряда;

![]() означает,

что в i-м

разряде перенос

должен

формироваться только при условии

поступления переноса

из

предыдущего разряда.

означает,

что в i-м

разряде перенос

должен

формироваться только при условии

поступления переноса

из

предыдущего разряда.

рис 9.65

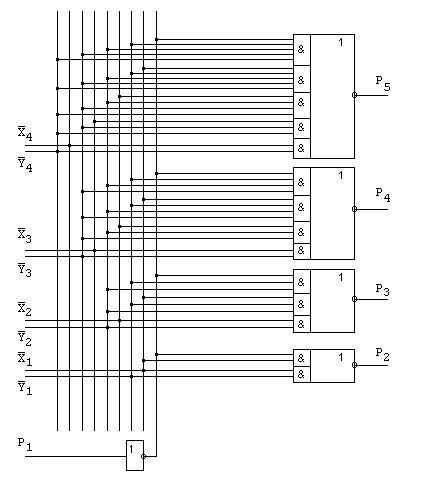

Рассмотрим

принцип построения блока ускоренного

переноса. Перенос

во

второй разряд должен формироваться при

условии

или

при условии

и

наличии переноса на входе

![]() ,

т.е.

,

т.е.

![]() .

После преобразований получим

.

После преобразований получим

![]()

Аналогичные выражения можно построить для переносов в другие разряды:

![]() ;

;

![]()

На рис. 9.66,а и б показаны схема блока ускоренного переноса и его условное обозначение.

Входящие

в выражения

![]() величины

,

формируются

одновременно во всех разрядных сумматорах,

одновременно поступают на входы блока

ускоренного переноса и, следовательно,

в этом блоке одновременно формируются

переносы, подаваемые в разрядные

сумматоры. После поступления переносов

из блока ускоренного переноса в разрядных

сумматорах формируются суммы

величины

,

формируются

одновременно во всех разрядных сумматорах,

одновременно поступают на входы блока

ускоренного переноса и, следовательно,

в этом блоке одновременно формируются

переносы, подаваемые в разрядные

сумматоры. После поступления переносов

из блока ускоренного переноса в разрядных

сумматорах формируются суммы

![]() .

.

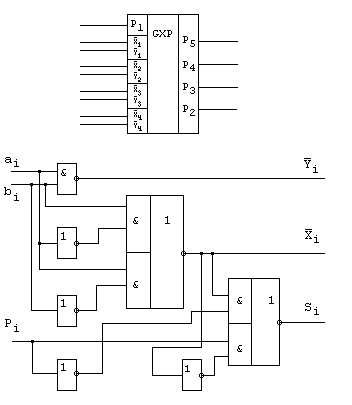

Формирование

инверсных значений

![]() и

и

![]() и

суммы

в

разом сумматоре может быть выполнено

с использованием следующих логических

выражений:

и

суммы

в

разом сумматоре может быть выполнено

с использованием следующих логических

выражений:

![]() ;

;

![]() ;

;

![]()

рис 9.66

рис 9.66

Схема разрядного сумматора, построенного в соответствии с этими выражениями, показана на рис. 9.66,в.