- •Семейство микроконтроллеров aDuC70xxс прецизионной подсистемой аналогоцифрового преобразования.

- •Общее описание

- •Терминология и сокращения

- •Дифференциальная нелинейность

- •Погрешность смещения

- •Погрешность усиления

- •Режим 16-битных команд Thumb (t)

- •Умножение 32-разрядных чисел (m)

- •Встроенный отладчик EmbeddedIce (I)

- •Исключения

- •Регистры arm

- •Время обработки прерывания

- •Организация памятив aDuC70xx

- •Память Flash/ее

- •Память sram

- •Регистры внутрикристальных периферийных устройств.

- •Функция преобразования ацп

- •Тактирование

- •Особенности ацп в микросхеме aDuC7019

- •Интерфейс ацп с регистрами mmrs

- •Дифференциальный режим

- •Псевдодифференциальный режим

- •Однополярный режим

- •Структура аналогового входа

- •Подача сигнала на аналоговые входы

- •Калибровка ацп

- •Датчик температуры

- •Источник опорного напряжения

- •Энергонезависимая память flash/ee

- •Надежность Flash/ee памяти

- •Программирование флэш-памяти через последовательные интерфейсы.

- •Программирование флэш-памяти через интерфейс jtag

- •Интерфейс управления памятью Flash /ee

- •Защита памяти flash/ee

- •Существует два уровня защиты:

- •Последовательность записи ключа такова:

- •Интерфейс управления памятью Flash /ee

- •Подробное описание регистров интерфейса управления памятью Flash/ee

- •Время выполнения программы из памяти sram и из флэш-памяти

- •Отображение блоков памяти в адресное пространство

- •Причины формирования сигнала начального сброса reseTи действие этого сигнала

- •Прочая аналоговая периферия

- •Использование цап

- •Монитор источника питания

- •Компаратор

- •Генератор и схема фапч Система тактирования микроконтроллера

- •Использование внешнего кварцевого резонатора

- •Переход в режим тактирования от внешнего генератора

- •Система управления питанием

- •Интерфейс системы управления питанием и тактированием

- •Цифровая периферия Трехфазный широтно-импульсный модулятор (шим)

- •Модели в 40-выводных корпусах (aDuC7020, 21, 22)

- •Описание блока шим

- •Отключение блока шим

- •Портыдискретного параллельного ввода/вывода

- •Последовательные интерфейсы в микросистемах aDuC70xx

- •Мультиплексирование выводовпоследовательныхинтерфейсов

- •Последовательный интерфейс uart

- •Структурная схема передатчика и приёмника

- •Набор линий интерфейса и протокол канального уровня

- •Контрольный бит и спобобы его использования

- •Задание скорости передачи (частоты следования битовых интерваловBaudrate) в aDuC70xx

- •Дробный делитель (FractionalDivider)

- •Основные регистры сф, ассоциированные с подсистемой uart

- •Сетевой режим с аппаратной поддержкой адресации.

- •Последовательный синхронный периферийный интерфейс spi.

- •Последовательные интерфейсы i2c Блок программируемой логики

- •Подсистема прерываний микрокомпьютера aDuC70xx

- •Источники запросов прерываний

- •Интерфейс внешней параллельной адресуемой магистрали

- •Таймерная подсистема

Генератор и схема фапч Система тактирования микроконтроллера

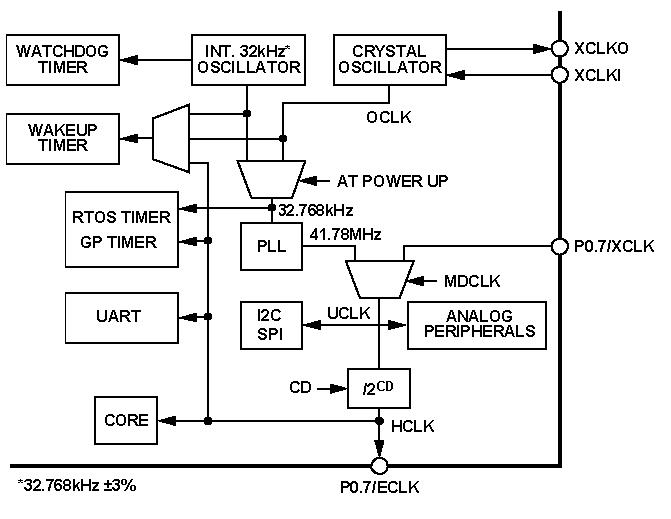

В качестве источника опорной частоты в системе тактирования микросхем ИС ADuC7019/…/28 может использоваться один из трех источников: а) встроенный генератор, стабилизируемый внешним кварцевым резонатором 32768 Гц, либо б) внешний генератор, частота которого должна лежать в диапазоне 0.05…44 МГц, либов) внутрикристальныйгенератор на 32768 Гц ±3%. Варианты а) и б) обеспечивают точное задание частоты тактирования.

Вариант в) позволяет строить систему, не использующую ни внешнего генератора, ни внешнего кварцевого резонатора. При этом точность задания тактовой частоты достаточна для получения стандартных битовых частот в асинхронном последовательном порте, через который может быть произведена загрузка программы в память микросистемы.

При использовании в качестве источника тактирования частоты 32768 Гц, она поступает на вход умножителя с Фазовой Автоподстройкой ЧастотыФАПЧ (PLLPhase-LockLoop). Схема ФАПЧ умножает частоту внутреннего генератора на 1275, чтобы получить частотуUCLK=41.78 МГц для тактирования системы.Ядро может работать на этой частоте, либо на частотах в 2, 4, … 128 раз меньших, обеспечивая энергосбережение. Фактическая частота тактирования процессорного ядра в дальнейшем изложении будет обозначаться как HCLK.

Следует заметить, что в опциях проекта среды разработки Vision3 ver.3.23 и ver 3.53 ошибочно указанозначение частоты UCLK = 40.96 МГц, но в симуляторе микроконтроллеров ADuC70xx, меню «Peripherals, диалоговое окно «PLL&OscillatorandPowerControl указано верное значение 41,7792 МГц.

По умолчанию частота ядра равна частоте PLL, деленной на 8, т.е. 5.22 МГц (5.12 МГц). Сигнал тактирования ядра можно вывести на внешний контакт (выход обозначен как ECLK) как изображено на рис.???.Это возможно при использовании любого из трех источников тактирования.

Следует учитывать, что, выход ECLK маломощный,не имеет внутреннего буферного усилителя и поэтому требует для тактирования внешних цифровых узлов внешней буферизации.

По сигналу начального сбросавключается режим тактирования от внутрикристального генератора. Управление режимом работы системы тактирования ядра производитсячерез периферийный регистр PLLCON. Для записи в этот регистр следует использовать специальную последовательность команд, которая описана ??? далее. Это сделано с целью защиты от случайной модификации этого регистра, для повышения надежности системы.

Использование внешнего кварцевого резонатора

Чтобы переключиться в режим работы тактового генератора с синхронизацией от внешнегоаварцевого резонатора, надо придерживаться следующей процедуры:

1) сконфигурировать Timer2в режим генерации запроса прерывания через интервал времени> 120 мкс 2) в регистр PLLCONзаписать значение 01 (установить биты 1:0(MDCLK) в состояние 01 и очистить бит OSEL), для чего следует использовать упомянутую специальную последовательность команд.

3) принудительно перевести микросхему в режим NAP, записав необходимую последовательность в регистр POWCON

4) по истечении тайм-аута, отсчитанного Таймером2 произойдет прерывание, выход микросхемы из состояния NAP, и одновременно ‑ переключение внутрикристального генератора в режим работы с внешним кварцевым резонатором.

Пример кода на Си, который осуществляет описанную последовательность действий:

T2LD = 5; //константа для задания тайм-аута таймера2 ≈ 150 мкс.

TCON = 0x480; // таймер2 – частота тактирования 32768 Гц и пуск

while(T2VAL >3); //убедиться, что значение времени загружено

IRQEN = 0x10; //разрешить прерывание от Таймера2

PLLKEY1 = 0xAA; //используя специальную последовательность команд,

PLLCON = 0x01; // выбрать частоту тактирования ядра 20 МГц

PLLKEY2 = 0x55;

POWKEY1 = 0x01; //используя специальную последовательность команд,

POWCON = 0x27; // перевести ядро в режим Nap

POWKEY2 = 0xF4;

В условия высокого уровня помех, их влияние может привести к потере «захвата» фазы в контуре ФАПЧ.На этот случай предусмотрено формирование запроса прерывания по потере захвата фазы (как же оно обрабатывается??? действительно ли при потере захвата немедленно останавливается ядро??? тогда причем здесь обработчик прерывания???). Если это происходит, немедленно останавливается тактирование ядра, а продолжение обработки прерывания по потере захвата произойдет только когда будет возобновлено правильное функционирование ФАПЧ. На захват фазы может потребоваться некоторое время. Для возобновления правильной работы следует использовать сторожевой таймер, который всегда тактируется от внутреннего тактового генератора 32768 Гц ±3%, даже если тактирование ядра приостановлено. Сигнал сброса от сторожевого таймера перезапустит программу со стартового адреса. В коде инициализации системы после сигнала сброса следует проанализировать содержимое регистра RSTSTA, чтобы выяснить, произошел ли перезапуск по переполнению сторожевого таймера.