- •1. Загальна структура і функції комп’ютера

- •2. Продуктивність комп’ютера

- •3. Швидкодія мікропроцесорів

- •4. Система магістралі

- •5.Зв’язок між компонентами комп’ютера через магістраль

- •6.Магістраль рсі

- •7. Внутрішня пам’ять

- •8.Функції і характеристики підсистеми пам’яті

- •Размещение

- •10. Сучасні тенденції в організації модулів пам’яті

- •11. Стек

- •12.Зовнішня память

- •13.Збереження інформації на магнітних дисках

- •15.Оптична пам'ять

- •16. Збереження інформації на магнітних стрічках

- •17. Введення – виведення

- •18.Програмне введення –виведення

- •19. Введення-виведення по прериванню

- •20.Прямий доступ до пам’яті

- •Зовнішні інтерфейси….. Типы интерфейсов

- •Концепція організації операційних систем

- •Планування завдань

- •Керування розподілом пам’яті

- •Вектори обчислень

- •Арифметико-логічний пристрій

- •Система команд комп’ютера

- •Характеристики та функції команд

- •Структура і функції центрального процесора

- •30.Структура центрального процесора

- •31.Організація набору регістрів

- •32. Конвеєрна обробка команд

- •33. Комп’ютери зі скороченим набором команд

- •34. Організація конвеєру в risc-процесорах

- •35. Порівняльні характеристики risc і сisc комп’ютерів

- •36. Суперскалярні процесори

- •37. Паралелізм на рівні машинних команд

- •38. Функції пристрою керування

- •39. Мікрооперації

- •40. Управління роботою процесора

- •41. Пристрої управління із жорсткою логікою

- •42. Мікропрограмне керування

- •43. Управління послідовністю виконання мікрокоманд

- •44. Використання мікропрограмування

- •45. Параллельна обробка

- •46. Організація мікропроцесорних систем

- •47. Симетричні мультипроцесорні системи

- •48. Інформаційна цілісність кешів та протокол mesi

- •49. Кластери

- •50. Системи зі змінним часом звернення до пам’яті

34. Організація конвеєру в risc-процесорах

Для большинства машинных команд, которые имеют дело только с операндами в регистрах, цикл выполнения команды состоит из двух фаз:

I — фаза извлечения команды;

Е — фаза выполнения команды; при этом АЛУ выполняет преобразование опе рандов, поступающих из регистров, и записывает результат в один из них.

При выполнении команд загрузки данных из памяти и сохранения их в памяти цикл состоит из трех фаз:

I — фаза извлечения команды;

Е — фаза вычисления адреса;

D — фаза пересылки данных из регистра в память или из памяти в регистр.

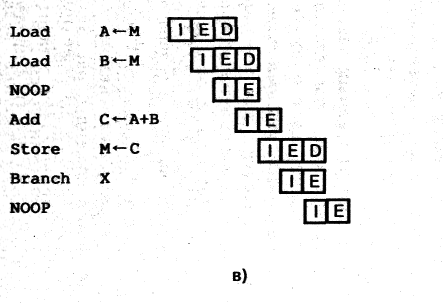

На рис. 12.6,а показана последовательность выполнения операций при отсутствии конвейера в процессоре. Совершенно очевидно, что при этом много времени тратится неэффективно. Даже простейшее совмещение выполнения отдельных фаз может существенно увеличить производительность. На рис. 12.6,6 показана последовательность операций при использовании двухпозиционного конвейера, в котором совмещено выполнение фаз I и Е двух разных команд. При этом достигается почти двукратное повышение производительности. Достичь теоретически максимально возможного повышения скорости мешает наличие двух проблем. Во-первых, предполагается, что используется однопортовая память, т.е. на каждом такте работы конвейера возможно только одно обращение к памяти. В результате при выполнении некоторых команд в последовательность операций приходится включать холостую фазу. Во-вторых, последовательный поток выполнения команд прерывается командами переходов. Для преодоления указанных затруднений компилятор включает в формируемую машинную программу холостые команды NOOP.

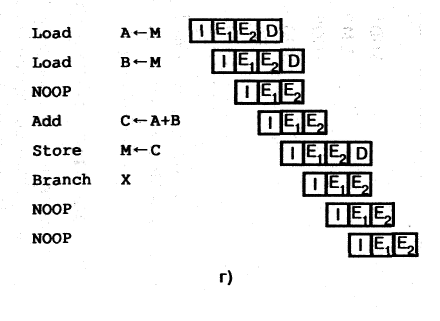

Повысить скорость работы конвейера также можно, используя память, позволяющую обрабатывать два обращения за один такт работы конвейера. Последовательность операций при такой организации показана на рис. 12.6,в. Появляется возможность параллельного выполнения трех машинных команд и, теоретически, трехкратного повышения производительности. Но наличие команд передачи управления в программе не позволяет достичь максимального теоретического предела. Кроме того, существует и зависимость между данными, обрабатываемыми последовательно выполняемыми командами. Если в одной команде используется операнд, изменяемый в предыдущей команде, в конвейере необходимо организовать задержку (холостой такт). Для этого в последовательность включается команда NOOP.

35. Порівняльні характеристики risc і сisc комп’ютерів

После начального периода эйфории от перспектив, открывающихся перед RISC-архитектурой, наступило некоторое отрезвление. Все больше конструкторов стали приходить к выводу, что RISC-архитектура выиграет, заимствуя некоторые особенности CISC-архитектуры, а CISC-архитектура получит преимущество, если в ее рамках будут реализованы некоторые идеи RISC-архитектуры. В результате большинство современных процессоров, которые принято относить к классу RISC, таковыми в чистом виде уже не являются. В частности, это относится к процессорам семейства PowerPC. Аналогично, и многие современные CISC-процессоры, например Pentium II, имеют определенные черты RISC-архитектуры.

Интересное сопоставление характеристик разных типов процессоров проведено в работе [MASH95]. В табл. 12.8 перечислены несколько моделей процессоров и проведено их сравнение по ряду характеристик. Считалось, что типовыми характеристиками RISC-архитектуры являются следующие.

Единый размер машинных команд.

Типовой размер команды — 4 байт.

Весьма ограниченное количество режимов адресации (как правило, менее 5). Этот параметр в некоторых моделях процессоров оценить однозначно довольно трудно. Например, в таблице литеральный и регистровый режимы не учитыва лись, а форматы с разными размерами смещений учитывались раздельно.

Отсутствие косвенной адресации, которая требует двойного обращения к памяти для извлечения операнда.

Отсутствие команд, сочетающих обращение к памяти с выполнением ариф метических операций (т.е. сложение с операндом, извлеченным из памяти, или сложение с записью результата в память).

Не более одного операнда, извлекаемого из памяти, в каждой команде.

Отсутствие произвольного выравнивания элементов данных в операциях загрузки/сохранения (т.е. все данные выравниваются по границе ма шинного слова).

Использование в минимальной степени устройства управления памятью (MMU — memory management unit) для адресации данных в команде.

Количество битов для задания регистра целых чисел в команде должно быть больше или равно пяти, т.е. не менее 32 регистров можно в явном ви де адресовать в команде.

10. Количество битов для задания регистра чисел в формате с плавающей точкой в команде должно быть больше или равно четырем, т.е. не менее 16 таких регистров можно в явном виде адресовать в команде.

Свойства от 1-го до 3-го определяют сложность дешифрации команды. Свойства от 4-го до 8-го позволяют упростить схему конвейера операций, особенно при использовании виртуальной памяти. Свойства 9 и 10 связаны с возможностями построения компиляторов.

Процессоры, перечисленные в первых восьми строках табл. 12.8, представляют собой типичную реализацию идей RISC-архитектуры. Следующие пять — типичные CISC-процессоры, а последние два, хотя и считаются RISC-процессорами, имеют множество свойств, характерных для CICS-архитектуры.