Лабораторная работа №4 / Laba_4

.docСанкт-Петербургский Государственный

Электротехнический Университет «ЛЭТИ»

Лабораторная работа №4

Выполнил: студенты гр. 3372

Сивков А. А.

Проверил: Фахми Ш. С.

Санкт-Петербург,

2005 г.

Лабораторная работа №4

Цель работы: реализовать устройство выводящие на семи - сегментный

индикатор заданные числа в шестнадцатеричном виде, на вход поступает 4-х разрядный код выводимого числа. На семи – сегментный индикатор поступает 7-ми разрядный код, отвечающий за состояние всех сегментов индикатора.

Задание: реализовать возможность вывода на семи – сегментный индикатор

следующих шестнадцатеричных чисел: 1, 4, 5, 6, 7, 9, A, E, F.

Разработка:

Разрабатываемой схеме будет соответствовать следующая таблица истинности:

|

hexit |

X0 |

X1 |

X2 |

X3 |

Ya |

Yb |

Yc |

Yd |

Ye |

Yf |

Yg |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

|

4 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

5 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

6 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

7 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

9 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

A |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

E |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

|

F |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

где: hexit – выводимое шестнадцатеричное число; X0 X1 X2 X3 – его 4-х разрядный код; Ya Yb … Yg – семиразрядный код поступающий на индикатор (Ya – соответствует сегменту ‘a’ семи - сегментного индикатора, Yg – сегменту ‘g’).

Нахождение функций: Минимизировав функции Ya - Yg картами Карно, получим:

Ya = X0 !X1 !X2 + !X0 X2 + X1 !X2

Yb = !X0 !X2 + X1 X2 !X3

Yc = !X1 !X2 + !X0 !X1 X2 + X1 X2 !X3

Yd = !X0 !X1 X2 + X1 X3

Ye = !X1 X2 X3 + X1 X2 + X0 !X2

Yf = !X0 X3 + !X0 X2 !X3 + X0 !X2

Yg = !X0 X3 + !X0 X2 !X3 + X0 !X2

для упрощения минимизации можно предположить, что на всех наборах X, больше 1000 значение функции равно 1 в «удобных» для минимизации картами Карно местах.

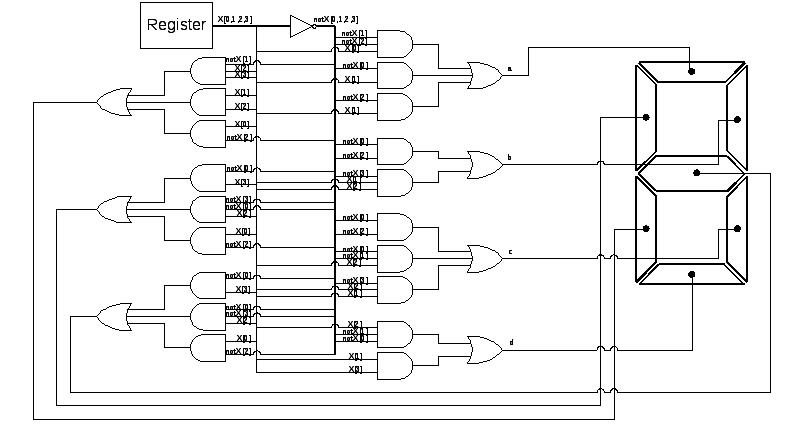

Логическая схема:

Проектирование цифрового устройства:

для реализации данного устройства необходимы следующие элементы:

CmdReg

– регистр задающий X1,

X2,

X3,

X4.

![]()

lpm_inv

– логическое НЕ

![]()

lpm_and

– логическое И

![]()

lpm_or

– логическое ИЛИ

![]()

Output

– выход с CLS

![]()

Все эти элементы находятся в Module library программы Triscend Fastchip. Перетаскиваем эти элементы из Module library на CSL. Настраиваем входы и выходы элементов в соответствии с функциональной схемой устройства, при этом lpm_inv имеет четыре входа, и четыре выхода (в этом элементе инвертируются значения x1, x2, x3, x4 на выходе получаем notx1, notx2, notx3, notx4). Элемент lpm_and имеет 9 входов и три выхода (по 1 выходу на 3 входа) всего потребуется 7 таких элементов. Элемент lpm_or имеет 3 (или 2) входа и 1 выход. В регистре CmdReg задаются значения x1, x2, x3, x4, значению регистра 0x05 соответствует последовательность 0, 1, 0, 1. Output используется для вывода значении a, b, c, d, e, f, g на семи - сегментный индикатор. Для того, чтобы присоединить выходы a, b, c, d, e, f, g к соответствующим ножкам (a – 127, b – 126, c – 101, d – 102, e – 103, f – 135, g - 136) необходимо в I/O editor (значок которого можно найти в правом углу) Output_A.x перетащить на нужные ножки.

Следующим этапом является Bind (приготовление проекта для использования в CSoC, проверка связей и т.д.), щелкаем на значок Bind в верху программы и ждем.

Загрузка проекта в устройство:

Из программы Fastchip запускаем программу Device link (одноименная кнопка на панели инструментов). Вводим IP адрес в Tools-> Device link options.

Нажимаем Configuration на панели инструментов -> Save and download.

Выводы:

В данной работе было спроектировано устройство преобразующее 4 бита входных данных в 7 бит выходных данных таким образом, чтобы для каждого входного набора на 7-сегментном индикаторе отображалась некоторая цифра (буква), указанная в задании.