- •1. Аналіз класів пам’яті змінних

- •2. Аналіз класів пам’яті функцій.

- •3. Концепція типу у мові програмування. Аналіз відомих методів типізації

- •4. Вільні масиви в мові програмування Сі, їх призначення та відмінність від звичайних. Навести приклади опису та застосування.

- •7, 26. Правила формування атрибутів доступу до членів похідного класу в залежності від атрибуту доступу базового класу та заданого атрибуту у списку спадкування.

- •8, 27. Вказівники та динамічна пам’ять. Аналіз методів виділення та звільнення динамічної пам’яті

- •9, 28. Аналіз методів передачі параметрів до підпрограм через локальні та нелокальні середовища

- •10. Зв’язний список та наскрізний прохід по зв’язному списку. Операції над зв’язними списками. Додавання та вилучення елементів у зв’язному списку. Навести приклади.

- •11. Структури даних. Типові статичні та динамічні структури даних. Доступ до даних.

- •12. Аналіз методів подання графів у вигляді динамічних та статичних структур даних. Матриця суміжності

- •13. Парадигма об’єктно-орієнтованого програмування та основні його принципи, їх зміст.

- •14. Порівняльний аналіз статичних та віртуальних методів в об’єктно-орієнтованому програмуванні, їх особливості. Призначення та правила формування конструкторів та деструкторів.

- •15. Правила віртуалізації методів в ооп.

- •16. Поняття технології створення програмного забезпечення та основні технологічні етапи. Приклади технологій.

- •17. Взаємозв’язок імен масивів та вказівників в мові програмування Сі. Операції над вказівниками. Приклади для одно- та двомірних масивів.

- •18. Контейнерні класи та їх призначення

- •19, 29. Вкладені класи та їх призначення.

- •20. Локальні класи та їх призначення

- •23. Абстрактні типи даних, правила і засоби їх формування.

- •30. Математичні моделі біполярного транзистора програми Spice

- •31. Алгоритм розрахунку перехідної характеристики програми Spice

- •32. Алгоритм розрахунку режиму за постійним струмом програми Spice

- •34. Поняття об’єкту в мові vhdl

- •35. Поняття сигналу в мові vhdl. Драйвер сигналу

- •36. Модель дискретного часу в мові vhdl.

- •37. Модель польового транзистора програми Spice

- •38. Архітектурне тіло та об’єкт в мові vhdl

- •39. Призначення та можливості програми spice

- •40. Оператор процесу в мові vhdl

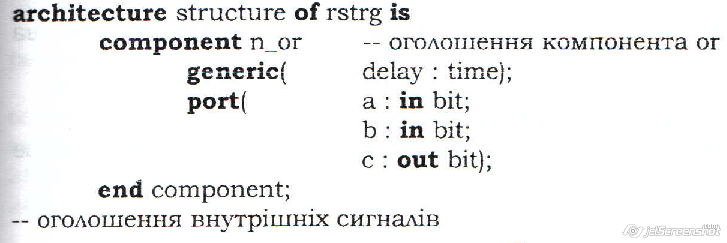

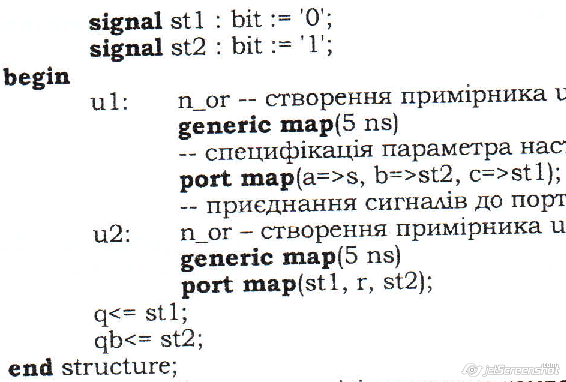

- •41. Створення структурного опису цифрової системи мовою vhdl

- •42. Змінні та сигнали в мові vhdl

- •43. Присвоювання сигналу в мові vhdl

- •44. Планування транзакцій та драйвер сигналу в мові vhdl

- •45. Розрахунок амплітудно-частотної характеристики в програмі Spice.

- •46. Послідовні та паралельні оператори мови vhdl

- •47. Створення примірників компонентів та опис топології цифрового пристрою мовою vhdl

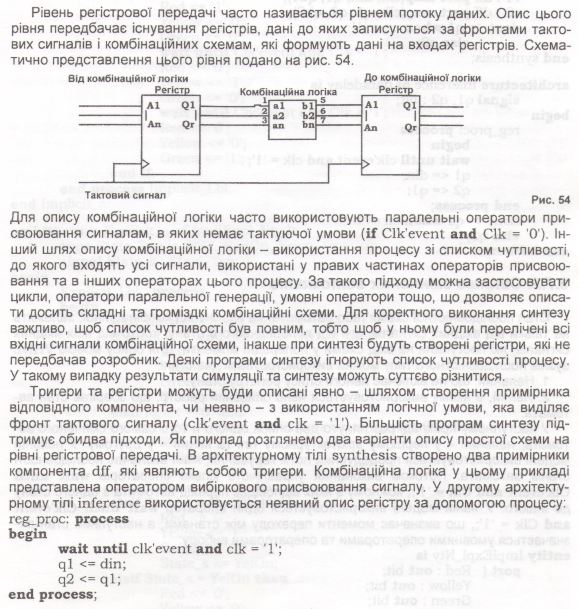

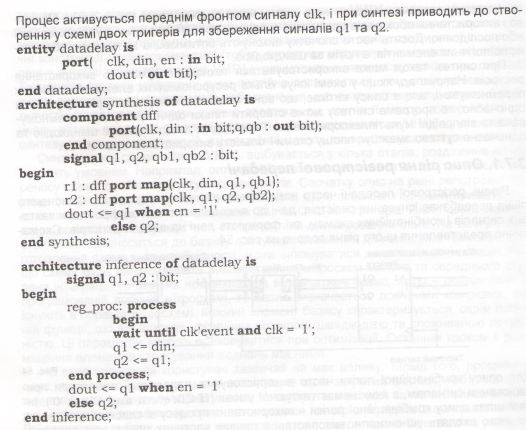

- •48.Опис рівня регістрової передачі мовою vhdl

- •49. Вхідна мова програми Spice

- •50. Модель Еберса-Мола біполярного транзистора

- •51. Модель Гумеля-Пуна біполярного транзистора

- •52. Інерційна та транспортна затримки в мові vhdl

- •53. Принципи роботи системного інтерфейсу isa (8 біт).

- •54. Стандарти систем автоматизації, побудованих на основі системних інтерфейсів.

- •55. Інтерфейс hs-488 ( швидкісний канал спільного користування).

- •57, 66, 70, 71.Канал спільного користування. Структура магістралі. Робота шини. Реалізація інтерфейсу.

- •58, 73. Приладовий інтерфейс (канал загального користування). Адресування приладів на магістралі. Алгоритми обміну інформацією в магістралі.

- •59. Приладовий інтерфейс (канал загального користування). Пошук джерела сигналу “запит на обслуговування”. Послідовне опитування.

- •60. Приладовий інтерфейс (канал загального користування). Пошук джерела сигналу “запит на обслуговування”. Паралельне опитування

- •64. Основні принципи перетворення сигналів. Дискретизація сигналів. Цифро-аналогові перетворювачі.

- •67, 72. Основні принципи перетворення сигналів. Дискретизація сигналів. Цифро-аналогові перетворювачі.

- •65, 68, 69. Аналогово-цифрове перетворення. Принципи роботи. Реалізація інтерфейсу з ibm pc. Реалізація систем збору інформації

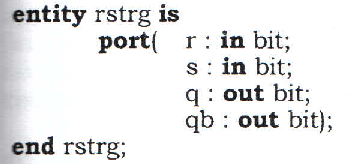

47. Створення примірників компонентів та опис топології цифрового пристрою мовою vhdl

(опціонально)

Примірник компонента створюється наступним чином:

<назва примірника>: <назва компонента, примірник якого створюємо>

generic map (<задання параметрів>);--може бути відсутнім у компонента

port map (<приєднання сигналів до портів примірника>);

Якщо під’єднання до портів компонентів недостатньо для опису топології данного пристрою, сигнали с портами прострою можно з’днувати наступним чином:

<порт> <= <сигнал>;

наприклад

a <= s after 10 ns;

Приклад:

48.Опис рівня регістрової передачі мовою vhdl

49. Вхідна мова програми Spice

До появи засобів автоматизації електронного проектування, які дозволяли створення графічного зображення принципових схем описувалися у вигляді текстового файлу з використанням однієї з мов опису апаратних засобів (Hardware Description Language – HDL). За сутністю такий опис являє собою список всіх компонентів схеми та список їх з’єднань.

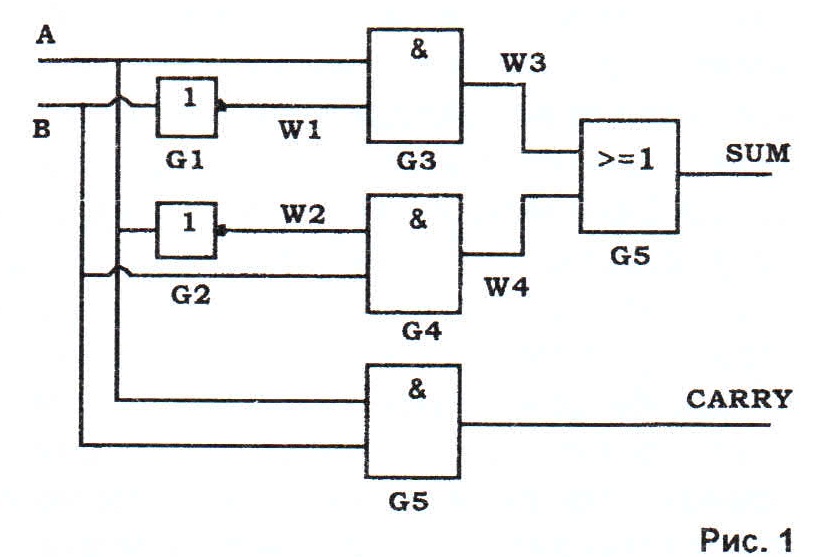

Як приклад можна розглянути одно розрядний напівсуматор (рис. 1).

Опис цієї схеми мовою апаратних засобів має такий вигляд:

Circuit halfadd (a, b, sum, carry)

inv(a, f)

and2(a, b, f)

or2(a, b, f)

g1: inv(b, w1)

g2: inv(a, w2)

g3: and2(a, w1, w3)

g4: and2(w2, b, w4)

g5: or2(w3, w4, sum)

g6: and2(a, b1, carry)

end circuit;

У заголовку цього опису вказано назву схеми, її входи та виходи. Після цього наведено список використаних компонентів, а в кінці – список примірників цих компонентів і з’єднань між ними. Аналогічна мова використовується для опису аналогових схем у програмі SPICE. Подібних мов було свого часу створено досить багато. Їх було запропоновано фірмами-розробниками мікросхем, а синтаксичні конструкції мов було тісно пов’язано з технологіями, що реалізують ці фірми. Такі мови опису апаратних засобів дозволяють описати схему на структурному рівні, тобто представити її як сукупність пов’язаних між собою елементів. Відносно нещодавно з’явилися мови опису апаратних засобів, які дозволяють створити поведінковий опис схеми. Це мови VHDL і Verilog. Вони також дозволяють створювати структурний опис схеми, але їх справжня потужність виявляється у можливості синтезу електронної схеми за її технологічно незалежним функціональним описом.

Вибір між використанням мов опису апаратних засобів і вводом графічного зображення принципової схеми завжди є складним питанням при виборі методології розробки електронних пристроїв. Досвідчені користувачі мов опису апаратних засобів вважають, що їх використання є найбільш швидшим і зручним методом розробки. Наприклад, створення двадцятирозрядного регістра зсуву при використанні схемного підходу вимагає розміщенні та з’єднання двадцяти тригерів. При використанні мов опису апаратних засобів для опису такого регістру або іншої регулярної структури достатньо кількох рядків коду. Використання засобів синтезу також суттєво спрощує та прискорює розробку систем, які складаються з комбінаційних схем, суматорів, перемножувачів, скінченних автоматів тощо. Проте, використання пакетів створення принципових схем потребує меншої кваліфікації розробника та нетривалого часу навчання користувача. За схемою підходу (завдяки його наочності) пошук, локалізація та виправлення помилок зазвичай вимагає менших втрат часу, ніж при використанні мов опису апаратних засобів.