- •Курсовой проект

- •2007 Г Оглавление

- •Введение.

- •Техническое задание.

- •1. Разработка устройства

- •1.1 Обобщенная функциональная схема и принцип работы устройства

- •1.2 Функциональная схема и принцип работы блока “Анализатор прихода пакета по последовательному интерфейсу rs-232” (rs_232_Analyzer_Incoming, первый блок устройства).

- •1.3 Функциональная схема и принцип работы блока “Анализатор информации, принятой по последовательному интерфейсу rs-232” (Part3, второй блок устройства).

- •1.4 Функциональная схема и принцип работы блока “Формирователь сигналов” (Part4, третий блок устройства).

- •1.5 Дополнительные элементы устройства и характеристика устройства в целом.

- •2. Тестирование устройства

- •2.1 Тестирование блока rs_232_Analyzer_Incoming

- •2.2 Тестирование блока Part3

- •2.3 Тестирование блока Part4

- •2.4 Тестирование устройства в целом

- •Заключение

- •Список использованной литературы

- •Приложение 1

- •Приложение 2.

- •1. Текст автомата rs_232_Analyzer (rs_232_Analyzer_Incoming).

- •2.Текст подблока Decounter (Part3).

- •3.Текст подблока Sig_Counter (Part3).

- •Текст автомата requester (Part4).

- •Текст устройства spad (Part4).

- •Текст устройства Sig_Sender (Part4).

- •Приложение 3.

Текст устройства spad (Part4).

Entity spad is

port

(col_1, col_2 : in integer range 0 to 255;

col : out bit);

end spad;

architecture arch of spad is

begin

process (col_1, col_2)

begin

if col_1 = 1 and col_2 = 0 then

col <= '1';

else

col <= '0';

end if;

end process;

end arch;

Текст устройства Sig_Sender (Part4).

Entity Sig_Sender is

Port

(External_clk, dir, ena : in bit;

delta : in integer range 0 to 1000000;

k_vo : in integer range 0 to 255;

pausa : in integer range 0 to 10000000;

p : in integer range 0 to 200000;

dq, sig: out bit);

end Sig_Sender;

architecture arch of Sig_Sender is

begin

process (External_clk, ena, delta, k_vo, p, pausa)

variable cnt: integer :=0;

variable cnt1: integer :=0;

variable cnt2: integer :=0;

variable p1: integer := 0;

begin

p1 := 10*p;

if ena = '1' then

if External_clk'event and External_clk='1' then

cnt := cnt + 1;

dq <= '0';

if dir = '0' then

p1 := p1 + delta*cnt1;

else

p1 := p1 - delta*cnt1;

end if;

if cnt = p1 then

p1 := p1 + delta;

sig <= '1';

elsif cnt = 2*p1 then

p1 := p1 + delta;

sig <= '0';

cnt := 0;

cnt1 := cnt1 + 1;

end if;

if cnt1 >= k_vo then

sig <= '0';

cnt := 0;

cnt2 := cnt2 + 1;

if cnt2 = 5*pausa then

cnt1 := 0;

cnt2 := 0;

dq <= '1';

end if;

end if;

end if;

end if;

END PROCESS;

end arch;

Приложение 3.

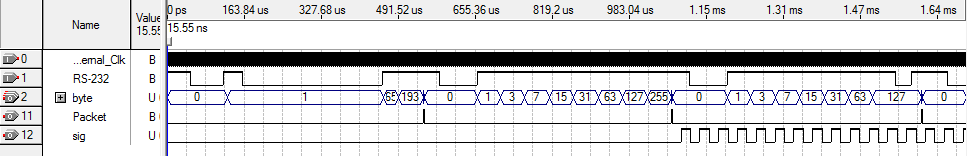

Рис. пр_3.1. Временная диаграмма работы блока RS_232_Analyzer_Incoming.

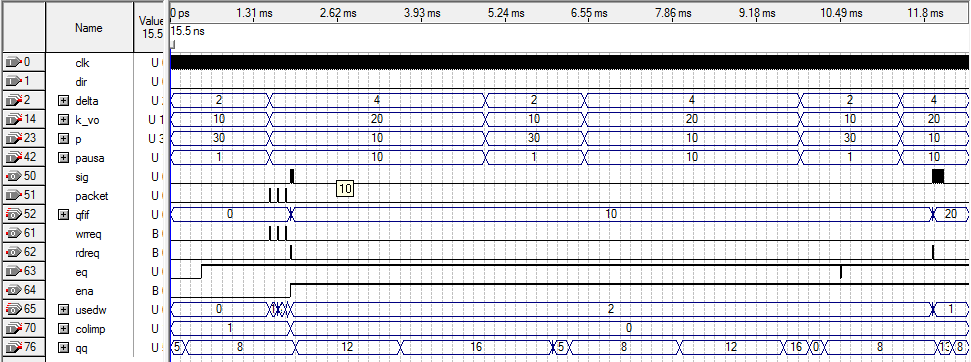

Рис. пр_3.2. Временная диаграмма работы блока Part4.

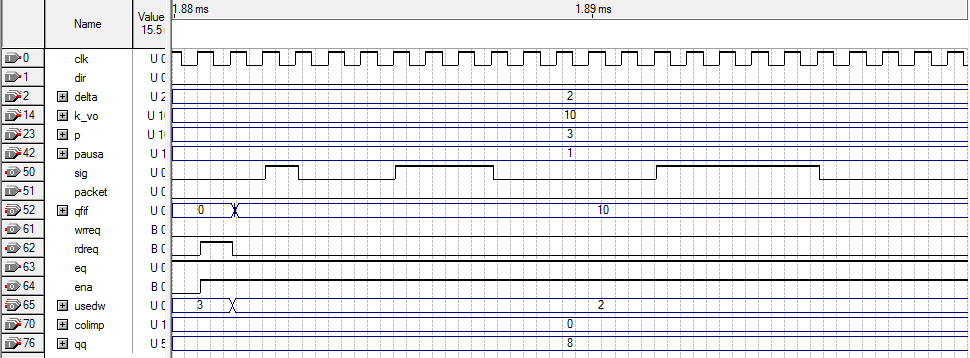

Рис. пр_3.3. Временная диаграмма работы блока Part4.

Рис. пр_3.4.а Увеличенный фрагмент временной диаграммы работы блока Part4.

Рис. пр_3.4.б Увеличенный фрагмент временной диаграммы работы блока Part4.

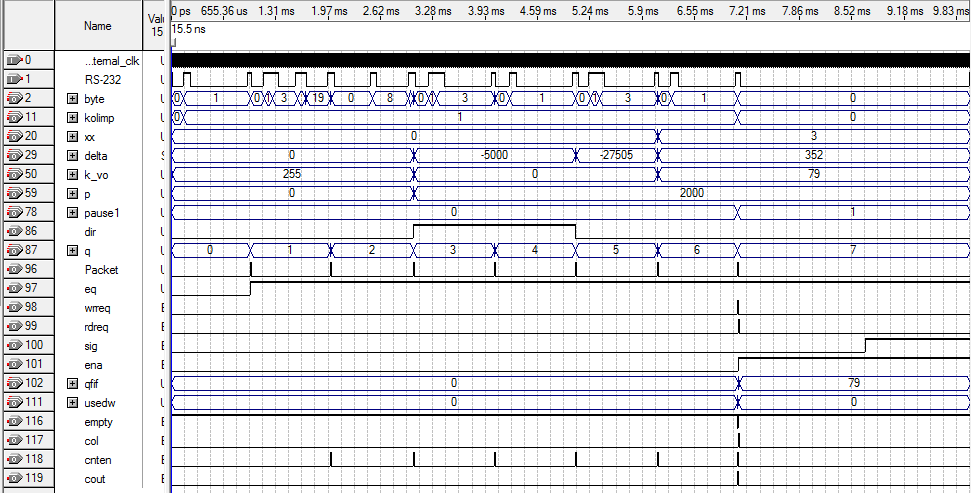

Рис. пр_3.5. Временная диаграмма работы устройства в целом.