- •27 Лекция. Принцип построения сложных программируемых логических устройств (сплу). Методика построения функциональных узлов на сплу. Базовые матричные кристаллы.

- •27.1 Программируемые логические матрицы

- •9.3. Программируемая матричная логика (пмл)

- •9.4. Функциональные разновидности плм и пмл

- •9.4.1. Схемы с программируемым выходным буфером

- •9.4.2. Схемы с двунаправленными выводами

- •9.4.3. Схемы с памятью

- •9.4.4. Пмл с разделяемыми конъюнкторами

- •9.5.Базовые матричные кристаллы (вентильные матрицы с масочным программированием)

- •9.5.1. Основные понятия и определения

- •9.5.2. Структуры бмк

27 Лекция. Принцип построения сложных программируемых логических устройств (сплу). Методика построения функциональных узлов на сплу. Базовые матричные кристаллы.

Наряду со стандартными в системах обработки информации присутствуют и некоторые нестандартные части, специфичные для данной разработки. Реализация нестандартной части исторически была связана с применением микросхем малого и среднего уровней интеграции. Это характерно резким ростом числа корпусов ИС, усложнением монтажа, снижением надежности системы. В то же время заказать для разрабатываемой системы обработки информации специализированные ИС высокого уровня интеграции затруднительно, так как это связано с очень большими затратами средств и времени на проектирование БИС и СБИС.

Возникшее противоречие нашло разрешение на путях разработки БИС и СБИС с программируемой и репрограммируемой структурой [29].

Первыми представителями указанного направления явились программируемые логические матрицы ПЛМ (PLA, Programmable Logic Array), программируемая матричная логика ПМЛ (PAL, Programmable Array Logic) и базовые матричные кристаллы БМК, называемые также вентильными матрицами ВМ (GA, Gate Array).

PLA и PAL в английской терминологии объединяются также термином PLD (Programmable Logic Devices).

Микросхемы ПЛМ, ПМЛ и БМК положили начало двум основным ветвям дальнейшего развития логических схем с программируемой и репрограммируемой структурами. Продолжением линии ПМЛ стали БИС и СБИС CPLD (Complex Programmable Logic Devices), а линии БМК – FPGA (Field Programmable Logic Devices). Стремление объединить достоинства обеих линий привело к созданию БИС–СБИС смешанной (комбинированной) архитектуры, для которых еще не выработано общепринятое название (ф. Altera пользуется названием FLEX (Flexible (гибких) Logic Element MatriX). Рост уровня интеграции дал возможность размещать на кристалле схемы, сложность которых соответствует целым системам. Эти схемы именуются SOC (Systems On Chip).

Следует отметить, что в области современной вычислительной техники, отсутствует устоявшаяся терминология, особенно в русскоязычной литературе, где иногда одни и те же термины обозначают разные вещи. Для некоторых терминов русские аналоги еще не определились.

Для сложных программируемых логических схем CPLD некоторые авторы используют название ПЛИС, что нежелательно, так как более употребительное трактование термина ПЛИС – наименование всех интегральных схем программируемой логики вообще. Также неудачным следует считать и термин СПЛИС, так как на слух он воспринимается как ПЛИС. По [29] более удачным названием схем CPLD было бы СПЛУ – сложные программируемые логические устройства, что соответствует переводу термина CPLD на русский язык.

27.1 Программируемые логические матрицы

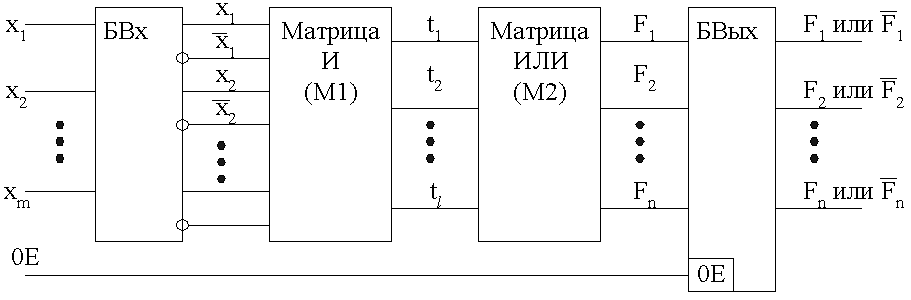

Программируемые логические матрицы (ПЛМ, PLA) появились в середине 70-х годов. Базовая структура ПЛМ приведена на рисунке 27.1. Основой их служит последовательность программируемых матриц элементов И и ИЛИ. В структуру входят также блоки входных и выходных буферных каскадов (БВх и БВых). Входные буферы, если не выполняют более сложных действий, преобразуют однофазные входные сигналы в парофазные и формируют сигналы необходимой амплитуды для работы матрицы элементов И. Выходные буферы обеспечивают необходимую нагрузочную способность выходов, разрешают или запрещают выход ПЛМ на внешние шины с помощью сигнала 0E, а иногда выполняют и более сложные действия.

Рисунок 27.1 – Базовая структура ПЛМ

Основными параметрами ПЛМ являются число входов m, число термов (элементов) l и число выходов n.

Переменные x1,…, xm подаются через БВх на входы элементов И, и в матрице И образуется l термов. Под термом здесь понимается конъюнкция (логическое произведение), связывающая входные переменные, представленные в прямой или инверсной форме. Число формируемых термов равно числу выходов матрицы И, которое определяется числом схем И в ней. Термы подаются далее на входы матрицы ИЛИ, т. е. на входы дизъюнкторов (логическое сложение), вырабатывающих выходные функции. Число дизъюнкторов равно числу вырабатываемых функций n.

Таким образом ПЛМ реализует дизъюнктивную нормальную форму воспроизводимых функций. ПЛМ способна реализовать систему n логических функций от m аргументов, содержащую не более l термов. Воспроизводимые функции являются комбинациями из любого числа термов, формируемых матрицей И. Какие именно термы будут выработаны и какие комбинации этих термов составят выходные функции, определяется программированием ПЛМ.

Выпускаются ПЛМ как на основе биполярной технологии, так и на МОП-транзисторах. Первые отечественные ПЛМ были выпущены в составе серии К556. Микросхемы 556РТ1 (прототип – микросхема 82S100), 556РТ2 (прототип – микросхема 82S101) выпускаются по схемотехнологии ТТЛШ, программируются пережиганием перемычек, m = 16, l = 48, n= 8. На рисунке 27.2,а в упрощенном виде (без буферных элементов) приведена часть принципиальной схемы биполярной ПЛМ К556РТ1, запрограммированной для реализации функций:***********

![]()

![]()

![]()

Рисунок 27.2 – Часть принципиальной схемы ПЛМ К556РТ1, запрограммированной для реализации функции

Элементами связей

в матрице И

служат диоды, соединяющие горизонтальные

и вертикальные шины, как показано на

рисунке 27.2,а, изображающем цепи выработки

терма t1.

Совместно с резистором и источником

питания цепи выработки термов образуют

диодные схемы И.

До программирования все перемычки целы

и диоды связи размещены во всех узлах

координатной сетки. При любой комбинации

аргументов на выходе будет ноль, так

как на вход схемы подаются одновременно

прямые и инверсные значения аргументов,

а

![]() .

При программировании в схеме оставляются

только необходимые элементы связи, а

ненужные - устраняются пережиганием

перемычек. В рассматриваемом примере

на вход конъюнктора поданы

.

При программировании в схеме оставляются

только необходимые элементы связи, а

ненужные - устраняются пережиганием

перемычек. В рассматриваемом примере

на вход конъюнктора поданы

![]() и x3.

Высокий уровень выходного напряжения

(логическая единица) появится только

при наличии высоких напряжений на всех

входах, низкое напряжение хотя бы на

одном входе фиксирует выходное напряжение

на низком уровне, так как открывается

диод этого входа и делает потенциал

данного терма низким.

и x3.

Высокий уровень выходного напряжения

(логическая единица) появится только

при наличии высоких напряжений на всех

входах, низкое напряжение хотя бы на

одном входе фиксирует выходное напряжение

на низком уровне, так как открывается

диод этого входа и делает потенциал

данного терма низким.

Элементами связи в матрице ИЛИ служат транзисторы (рисунок 27.2,в), включенные по схеме эмиттерного повторителя относительно линий термов и образующие схему ИЛИ относительно выхода (горизонтальной линии). На рисунке 27.2,в показано формирование функции F1.

При изображении запрограммированных матриц наличие элементов связей (неразрушенные перемычки) отмечаются точкой в соответствующем узле.

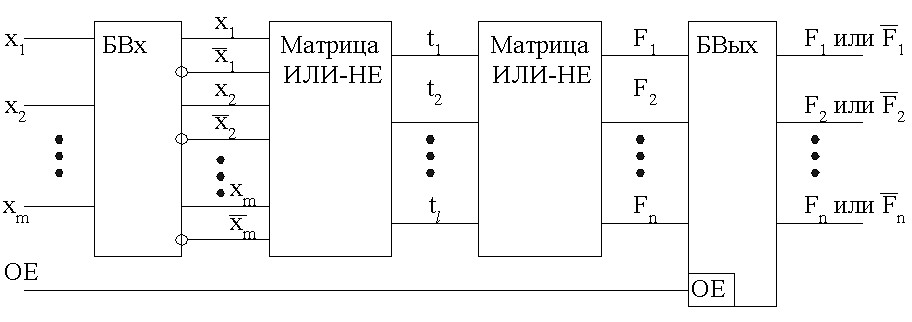

В схемах на МОП-транзисторах в качестве базовой логической ячейки используют инвертирующие (ИЛИ-НЕ, И-НЕ) элементы. Соответственно этому меняются и операции, реализуемые в первой и второй матрицах ПЛМ. В схемотехнике n-МОП базовым элементом является элемент ИЛИ-НЕ, а структура ПЛМ имеет вид, изображенный на рис.9.4. ПЛМ содержит две последовательно включенные матрицы ИЛИ-НЕ, одна из которых служит для выработки термов, другая - для выработки выходных функций. На основании правил де Моргана можно для терма t1 из предыдущего примера записать:

![]() .

.

Функция

![]() будет формироваться в инвертированном

виде.

будет формироваться в инвертированном

виде.

Рис. 9.1. Структура ПЛМ на МОП–транзисторах

Программирование ПЛМ, выполняемое пользователем, проводится с помощью программаторов (аналогично PROM). Перед программированием необходимо провести минимизацию заданной системы функций. Содержанием минимизации функций является поиск кратчайших дизъюнктивных форм. Вести поиск минимальных по числу термов представлений задачи целесообразно до уровня, когда число термов станет равным l у имеющейся микросхемы ПЛМ. Дальнейшая минимизация не требуется. Если размерность имеющихся ПЛМ обеспечивает решение задачи в ее исходной форме, то минимизации не требуется, так как она не ведет к сокращению оборудования.

Сведения для программирования подготовленной системы функций удобнее всего сводить в специальную таблицу [13], в которой указывается, что нужно сделать с перемычками: сохранить перемычку у прямого входа и пережечь перемычку инверсного входа, пережечь перемычку у прямого входа, сохранить перемычку у инверсного входа, пережечь перемычки у обоих входов переменной (т.е. переменная не входит в данный терм).

Внимание!

Оставление

перемычек у обоих входов переменной

недопустимо, так как в силу равенства

![]() ,

выход терма будет всегда нулевым. Также

должны быть указаны состояния перемычек

в матрице ИЛИ.

,

выход терма будет всегда нулевым. Также

должны быть указаны состояния перемычек

в матрице ИЛИ.