- •Глава 5 коммуникационные микроконтроллеры и системы на их основе

- •5.1. Общие понятия

- •5.1.1. Семиуровневая модель управления в сетях

- •5.1.2. Функции, реализуемые коммуникационным контроллером

- •5.1.3. Семейство коммуникационных микроконтроллеров мрс860

- •5.2. Организация коммуникационных процессорных модулей в кмк

- •5.2.1. Структура коммуникационного процессорного модуля

- •5.2.2. Контроллеры коммуникационных каналов scc

- •5.2.3. Контроллеры управления smc

- •5.2.4. Контроллеры дополнительных коммуникационных каналов

- •5.3. Поддержка протоколов в коммуникационных

- •5.3.1. Доступ к линиям т1/серт. Поддержка basic isdn

- •5.3.2. Виртуальные каналы и поддержка primary isdn

- •5.3.3. Работа в асинхронных каналах связи

- •5.3.4. Доступ к сетям с пакетной передачей (с протоколами х.25)

- •Алгоритмы работы сети. Процесс установления соединения

- •Процесс разъединения

- •Процесс передачи сообщения

- •5.3.5. Доступ к сетям ethernet

- •5.3.6. Протоколы, поддерживаемые на уровне загружаемого микрокода

Алгоритмы работы сети. Процесс установления соединения

Первичная станция. Для установления соединения станция передает в канал непрерывную последовательность флагов, т. е. переводит канал в активное состояние. Затем посылает команду установления соединения (например, SABM или SABME) и включает таймер Т1.

Вторичная станция. Если команда «установить режим работы» принята без ошибок, посылает кадр подтверждение UA и соединение считается установленным или, если не может установить соединение, посылает кадр DM и соединение считается не установленным. При установления соединения счетчики принятых и переданных кадров Nr и Ns сбрасываются.

Первичная станция. Получив ответ без ошибок, выключает таймер Т1, сбрасывает счетчики принятых и переданных кадров и полагает, что соединение установлено.Если принят ответ DM, то таймер выключается и соединение считается не установленным. Если ответ-подтверждение принят с ошибкой или истек тайм-аут на таймере Т1, то выполняется повтор процесса установления соединения. Число повторных попыток ограничено, если все попытки израсходованы, то станция переходит в режим «разъединения».

Во время процесса установки соединения все кадры, кроме кадров установки соединения (в примере SABM или SABME), - DISC, UA, DM, станциями, участвующими в попытке связаться, игнорируются.

Процесс разъединения

Первичная станция. Посылает команду DISC с установленным битом опроса Р = 1 и включает таймер Т1.

Вторичная станция. Приняв правильный кадр DISC, посылает ответ подтверждение в кадре UA и переходит в режим разъединения. Если станция уже находилась в режиме разъединения , то она посылает кадр-подтверждение DM с установленным битом конца F = 1 , оставаясь в режиме разъединения.

Первичная станция. Приняв кадр «ответ-подтверждение», выключает таймер Т1 и переходит в режим разъединения. Если в процессе ожидания истек таймер Т1, то производится повтор процесса разъединения. Число повторных попыток ограничено, если все попытки разъединить соединение израсходованы, об этом сообщается более высокому уровню управления сети, чтобы он начал процедуру восстановления канала связи на своем уровне.

Во время передачи команды DISC станция игнорирует все команды, за исключением команд и ответов установления соединения (в примере SABM и SABME), UA, DISC, DM.

Находясь в режиме разъединения, станция реагирует только на команды установления соединения и команду DISC. Приняв любой другой кадр-команду с битом опроса Р = 1, станция передает ответ DM в кадре с битом конца F = 1.

Процесс передачи сообщения

Первичная станция. При передаче информационного l-кадра указывает в поле Ns его порядковый номер: Ns = Vs. Запускает таймер ожидания ответа Т1 и увеличивает значение счетчика переданных кадров Vs := Vs+1.

Вторичная станция. При получении кадра из сети запускает таймер выдачи ответа Т2, который измеряет максимальное время от получения пакета до выдачи ответа. Получив адресованный ей информационный l-кадр, станция сравнивает значение в поле Ns-кадра со значением счетчика ожидаемых кадров Vr. Если значения совпали, то кадр передается в буфер, а значение счетчика увеличивается Vr := Vr+1. Если буфер перепол нен, то пакет сбрасывается, станция переходит в режим «занято» и посылает первичной станции уведомление в виде S-кадра типа RNR со значением поля Mr = Vr. Станция- передатчик, получив такой кадр, останавливает передачу новых l-кадров и повторную передачу неподтвержденных l-кадров, пока не получит S-кадр типа RR или REJ, либо же не истечет интервал ожидания ответа, контролируемый таймером Т1.

Получив без ошибок кадр от первичной станции, вторичная станция должна передать подтверждение приема кадра. Если у станции есть данные для передачи, то подтверждение посылается в l-кадре, установив значение поля Nr := Vr. Если данных для передачи нет, то посылается управляющий S-кадр типа RR со значением поля Nr = Vr.

Если же вторичная станция приняла без ошибок кадр с порядковым номером Ns <> Vr, то станция переходит в режим «прием неупорядоченного l-кадра», не учитывает информацию из принятого кадра и посылает S-кадр переспроса типа REJ с номером Nr = Vr. После передачи этого кадра станция игнорирует все l-кадры, пока не будет принят без ошибок I-кадр с номером Ns = Vr.

Если у станции истекает интервал, ограниченный таймером Т2, то первичной станции уведомление не пересылается, так как значения таймеров Т1 и Т2 подобраны так, что если станция-приемник не выдаст подтверждение до окончания счета Т2, то кадр не успеет дойти по станции-передатчика до окончания счета Т1.

3. Первичная станция. Ожидает пока не придет или подтверждение в виде информа ционного l-кадра, или S-кадр (типа RNR или REJ). После получения этих кадров станция останавливает таймер ожидания ответа Т1 и переходит к передаче следующего кадра данных. Получив подтверждение приема Nr-1-го кадра в пакете REJ, станция прерывает передачу новых Ι-кадров и повторно передает Ι-кадры с номерами от Nr до Ns. Если станция передавала S-кадры или U-кадры, то она заканчивает их передачу и только потом начинает повторную передачу 1-кадров. Если истек интервал ожидания ответа, то станция передает управляющий S-кадр типа RR, RNR или REJ с установленным битом опроса Р = 1 и снова запускает таймер Т1. Эти действия производятся для определения изменения статуса станции приемника.

Вторичная станция. В ответ на прием S-кадра определения статуса с установлен ным битом опроса F = 1 станция передает S-кадр типа RNR, установив бит F := 1, указы вая, что она продолжает оставаться в состоянии «занято», или S-кадр типа RR, или REJ с битом F = 1, если состояние «занято» снято. Состояние «занято» заканчивается, если станция снова может принимать информационные Ι-кадры.

Первичная станция. Если истек таймер ожидания ответа Т1, а ответ о статусе станции не пришел, то снова посылается кадр запроса о статусе. Число повторных попы- ток посылки это кадра ограничено конкретной реализацией протокола.

Использование режима повторной передачи. Режим повторной передачи может быть начат первичной станцией и без использования специального REJ-пакета с помощью механизма P/F-битов. Согласно требованиям протокола, на каждый кадр, передаваемый с битом Р = 1, должен прийти кадр ответа с битом F = 1. Передача новых кадров с битом Р = 1 не начинается, пока не будет получен ответный кадр с битом F = 1. Таким образом, если на переданный кадр с установленным битом Р = 1 не пришел ответ и истек интервал ожидания ответа, контролируемый таймером Т1, то первичная станция, не ожидая получения REJ-кадра, может произвести повторную передачу.

Если текущая версия протокола поддерживает S-кадры типа SREJ, то вторичная станция может запросить повторную передачу только одного искаженного кадра, запомнив при этом все принятые неупорядоченные l-кадры. Кадр SREJ передается станцией получателем, если она не получила l-кадр с номером Ns-1 = Vr, при этом в кадре указывается номер кадра Mr = Vr, который станции передатчику необходимо повторно передать. Это кадр также служит подтверждением приема l-кадров с номерами Ns < Nr.

Передав SREJ кадр, станция-приемник не может больше передавать новые SREJ-кадры, связанные с новыми ошибками, пока не придет правильный повторный 1-кадр с номером, указанным в первом SREJ-кадре. Так как передача нового SREJ-кадра может привести к подтверждению приема Ι-кадра, запрос на повторную передачу которого передан в первом SREJ-кадре и который может быть еще не получен станцией приемником. Для повышения эффективности передачи SREJ-кадров было принято соглашение, что все SREJ-кадры запрашивают повторную передачу Ι-кадра с номером Nr, но только кадры с установленными битами P/F = 1 подтверждают прием информационных кадров с номерами Ns < Mr, a SREJ-кадры с битами P/F = 0 не используются для подтверждений приема информационных кадров.

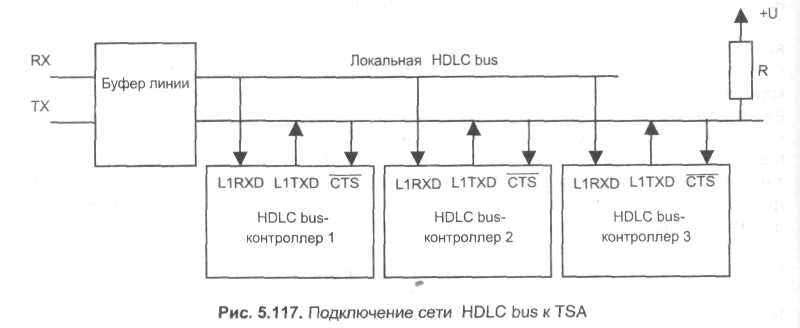

HDLC-контроллер. Основные режимы работы. HDLC - один из наиболее известных протоколов канального уровня управления 7-уровневой модели OSI. Решения, применяемые в протоколе для контроля за процессом передачи, оказались настолько удачными, что многие другие протоколы (SDLC, SS#7, LAPD, LAPB) базируются на основе HDLC-протокола и используют его алгоритмы обработки кадров данных. Формат HDLC-кадра показан на рис. 5.112.

Введение в формат кадра поля адреса позволяет протоколу работать с групповыми адресами и в многоточечных соединениях. Размер адресного поля зависит от конкретной реализации протокола. Обычно HDLC-протокол использует или 8- или 16-битное поле адреса.

Поле контроля (8- или 16-битное) предназначено для указания типа передаваемого кадра (информационный l-кадр, управляющий S-кадр, служебный U-кадр) и для нумерации пакетов при выполнении контроля за передачей и контроля правильности последовательности принимаемых пакетов.

В поле данных передается информация 3-го (сетевого) уровня модели OSI. Размер поля данных ограничивается только типом конкретной реализации протокола. Если пакет, содержащий данные сетевого уровня управления, невозможно передать внутри одного кадра данных HDLC-протокола, то длинные кадры при передаче разбиваются на части и каждая часть пакета нумеруется по модулю 8 или 128. Номер пакета передается в поле контроля.

Для контроля за правильностью передаваемой информации используются или 16-разрядные, или 32-разрядные циклические коды. Результат контроля записывается в 16-битное поле контрольной суммы CRC. При передаче байта данных первым передается младший значащий бит LSB, но при передаче байта CRC поля первым передается старший значащий бит MSB. Такой порядок передачи позволяет начинать проверку контрольной суммы поступающей информации сразу же после приема первого бита данных.

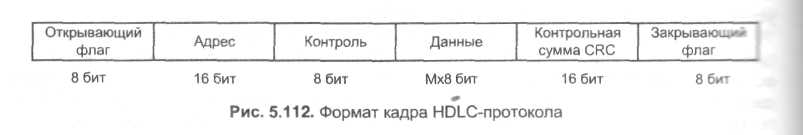

Настройка SCC-контроллера на работу с HDLC-протоколом выполняется в регистре GSMR при программировании битов MODE. Настройка режимов работы HDLC-контроллера выполняется в регистре PSMR (рис. 5.113). HDLC-контроллер может работать с любым ISDN-интерфейсом (IDL, GCI или РСМ) и выдавать информацию в В-канал или в D-канал, или может работать с внешними контактами соответствующего SCC-контроллера при работе в NMSI-режиме. Обычно из-за большого количества хорошо продуманных управляющих функций HDLC-протокол используют для управления передачей коммуникационного контроллера и передач данных по D-каналу ISDN-интерфейса.

Для работы в кольцевых структурах в контроллере МРС860 реализован дополнительный режим работы контроллера HDLC bus. Биты BUS в регистре конфигурации PSMR (рис. 5.113) определяют режим работы HDLC-контроллера (0 - нормальный HDLC-контроллер, 1 - контроллер HDLC bus).

Для управления передачей HDLC-контроллера, работающего в режиме HDLC bus, в регистре режима введен бит BRM. Если BRM = 0, то сигнал работает нормально, он выставляется = 0 при начале передачи первого бита и сбрасывается = 1 по окончании передачи, или если обнаружена коллизия во время передачи. Режим с установленным битом BRM = 1 используется при передаче в протяженных сетях. В этом режиме вначале выставляются данные, а затем, с задержкой на 1 бит, вырабатывается активный сигнал о начале

HDLC-контроллер имеет полностью независимую приемную и передающую части. Только если контроллер работает в мультиплексируемом режиме, его приемник и передатчик должны иметь одинаковую тактовую частоту, поступающую от внешнего источника. При работе в NMSI-режиме приемник и передатчик могут иметь различные тактовые частоты, которые могут поступать или от внутреннего генератора BRG, или от внешнего источника. HDLC-контроллер поддерживает и синхронный, и асинхронный режимы работы SCC-каналов.

Приемник и передатчик каждого HDLC-контроллера имеют полностью независимые таблицы буферных дескрипторов BD для работы с буферами данных. Контроллер поддерживает мультибуферную структуру, когда длинный кадр данных может быть расположен в нескольких буферах данных. Для указания первого буфера кадра в слове состояния BD используется бит F = 1 (First), а для указания последнего буфера кадра - бит L = 1 (Last). При работе с мультибуферной структурой пользователь может подготавливать следующие буферы данных постепенно, по мере обработки уже подготовленных буферов. Только в этом случае возможно возникновение ошибки переполнения (overrun) при приеме данных и ошибки незаполнения (underrun) при передаче, если центральный процессор не успеет вовремя подготовить новые буферы данных к тому моменту, когда будет завершена обработка старых.

Пользователь может управлять работой передатчика HDLC-контроллера с помощью команд STOP TRANSMIT, GRACEFUL STOP TRANSMIT, RESTART TRANSMIT, INIT TX PARAMETERS и работой приемника с помощью команд ENTER HUNT MODE, INIT RX PARAMETERS.

В СРМ добавлена возможность выключить работу приемника при передаче данных передатчиком этого же канала контроллера. Данный режим выбирается при программировании значения бита DRT := 1. При этом приемник будет находиться в выключенном состоянии, пока выставлен сигнал передачи RTS = 0. Такой режим работы полезен, когда линии данных приемника и передатчика объединены в одну шину (режим multidrop), и пользователь не желает принимать данные, которые он сам передает в текущий момент времени.

Распределение памяти параметров в микроконтроллере МРС860 приведено в табл. 5.77.

Таблица 5.77

Память параметров HDLC-протокола в микроконтроллере МРС860

Адрес |

Название |

Размер, бит |

Описание |

SCC base+30 |

- |

32 |

Зарезервировано |

SCC base+34 |

C_MASK |

32 |

Константа CRC |

SCC base+38 |

C_PRES |

32 |

Начальные значения CRC |

SCC base+3C |

DISFC |

16 |

Счетчик непринятых кадров |

SCC base+3E |

CRCEC |

16 |

Счетчик ошибок контрольной суммы CRC |

SCC base+40 |

ABTSC |

16 |

Счетчик принятых ABORT-последовательностей |

SCC base+42 |

NMARC |

16 |

Счетчик несовпадений адресов при приеме |

SCC base+44 |

RETRC |

16 |

Счетчик переданных кадров |

SCC base+46 |

MFLR |

16 |

Максимальная длина кадра |

SCC base+48 |

MAX_cnt |

16 |

Текущая длина кадра |

SCC base+4A |

RFTHR |

16 |

Число принятых кадров до прерывания |

SCC base+4C |

RFCNT |

16 |

Счетчик принятых кадров |

SCC base+4E |

HMASK |

16 |

Регистр маски адресов |

SCC base+50 |

HADDR1 |

16 |

Адрес, заданный пользователем |

SCC base+52 |

HADDR2 |

16 |

Адрес, заданный пользователем |

SCC base+54 |

HADDR3 |

16 |

Адрес, заданный пользователем |

SCC base+56 |

HADDR4 |

16 |

Адрес, заданный пользователем |

SCC base+58 |

ТМР |

16 |

Ячейка временного хранения |

SCC base+5A |

ТМР_ MB |

16 |

Ячейка временного хранения |

Примечание. Все переменные в таблице, кроме ячеек MAX_cnt, RFCNT, ТМР и ТМР_МВ, |

|||

ТМР_МВ инициализируются пользователем до начала работы с HDLC-контроллером. |

|||

Прием данных. При приеме данных HDLC-контроллер в МРС860 может без вмешательства центрального процессора принимать до 196 кадров, удалять открывающие и закрывающие флаги, распознавать, кому адресован пакет, проверять контрольную сумму и контролировать максимальную длину пакета.

После включения в работу приемник ожидает получение открывающего флага кадра. Когда флаг получен, далее контроллер проверяет содержимое поля адреса, чтобы определить, ему адресован пакет или нет. Для операций с адресами в памяти параметров HDLC-контроллера выделены четыре регистра адреса HADDR1-HADDR4 и один регистр маски адреса HMASK. Контроллер проверяет адрес, полученный в пакете, на совпадение с одним из четырех допустимых адресов, при этом учитывается содержимое регистра маски. Если некоторый бит регистра маски равен единице, то при сравнении адресов в этих битах в регистрах HADDR и в поле адреса принятого пакета должно быть совпадение. Если бит в регистре маски равен нулю, то при сравнении адресов совпадение этих битов необязательно. Например, если необходимо контролировать все 16 разрядов адреса в пакете, то регистр маски HMASK = 0xFFFF, если же достаточно контролировать только восемь младших разрядов адреса, то HMASK = 0x00FF. Маскирование отдельных разрядов адреса при сравнении часто используется при работе с групповыми адресами. Если пользователь желает установить для работы с контроллером только один сетевой адрес, то во все регистры HADDRi необходимо записать одно и то же значение единственного адреса. HDLC-контроллер допускает работу с широковещательными адресами, для этого в одной из ячеек HADDRi достаточно записать широковещательный (broadcast) адрес 0xFFFF.

Если пакет принят без ошибки, но совпадения адресов в регистрах и в поле адреса пакета не произошло, то пакет игнорируется и увеличивается счетчик непринятых пакетов в ячейке NMARC памяти параметров HDLC-контроллера.

Если совпадение адреса в принятом пакете с одним из допустимых адресов произошло, то содержимое пакета, начиная с поля адреса, записывается в память. Для этого HDLC-контроллер проверяет готовность следующего буфера BD для записи в него данных. Если бит незанятости в слове состояния BD E = 1, то контроллер производит запись информации в этот буфер по каналам SDMA. После заполнения текущего буфера контроллер сбрасывает бит Е := 0 и, если установлен бит прерывания в слове состояния текущего BD I = 1, вырабатывает прерывание к центральному процессору, чтобы он мог начать обработку данных из этого буфера. Если же прием текущего кадра еще не закончен, то контроллер проверяет, свободен ли следующий буфер BD в таблице дескрипторов, чтобы продолжить запись информации в данный буфер. Этот процесс повторяется, пока не будет принят весь кадр данных.

Во время приема данных HDLC-контроллер контролирует длину принимаемого кадра (размер полей кадра в байтах между ограничивающими флагами). Пользователь может в ячейке MFLR памяти параметров задать максимально допустимую длину кадра данных для этой сети. Если длина текущего кадра достигла этого предела, прием кадра в буфер прекращается и в слове состояния последнего BD устанавливается бит приема длинного кадра LG := 1. Далее контроллер, не принимая данные из кадра, дожидается окончания кадра, устанавливает в слове состояния последнего BD соответствующие биты статуса принятого кадра и записывает длину реально принятого кадра в последний буфер кадра. В ячейке MAX_CNT памяти параметров вычитающий счетчик ведет подсчет текущей длины принятого кадра. При начале приеме нового кадра в эту ячейку загружается значение максимальной допустимой длины кадра MAX_CNT := MFLR. Для полученной и записанной в буфер части длинного кадра также вычисляется контрольная сумма, которая записывается в последний буфер кадра.

По окончании приема кадра нормальной длины заново вычисляется контрольная сумма кадра по всем полям внутри ограничивающих флагов, которая сравнивается с содержимым поля контрольной суммы. Если произошла ошибка сравнения контрольных сумм, то принятая контрольная сумма записывается в последний буфер кадра, затем буфер закрывается, в слове состояния последнего BD устанавливается бит ошибки проверки контрольной суммы CR := 1 и вырабатывается, если разрешено, RXF-прерывание к центральному процессору через регистр событий канала. При этом увеличивается счетчик CRC ошибок в ячейке CRCEC памяти параметров, и приемник переходит в режим «охоты» (режим поиска нового кадра).

Если проверка контрольной суммы закончилась успешно, то контроллер устанавливает в слове состояния последнего BD биты состояния кадра, закрывает буфер и сбрасывает бит свободное™ этого буфера Е := 0. Далее контроллер генерирует, если разрешено, прерывание к центральному процессору, уведомляя его, что кадр получен и находится в памяти, и переходит в режим приема нового кадра.

При работе с HDLC-контроллером пользователь может запрограммировать выработку сигналов прерывания по окончании обработки каждого нового буфера BD или после обработки нескольких буферов, или целого кадра данных. В СРМ пользователь может разрешить HDLC-контроллеру прерывать центральный процессор не после приема каждого кадра данных, а только после приема определенного в ячейке RFTHR-памяти параметров числа кадров. Подсчет текущего числа принятых кадров производится в ячейке RECNT. Установив этот режим работы и настроив таймеры на соответствующий режим работы, пользователь может измерять рабочие параметры канала связи, например его пропускную способность. Но для того чтобы успешно использовать этот режим работы, следует заранее подготовить необходимое число буферов для приема заданного числа кадров без вмешательства центрального процессора.

Для временного хранения принятой информации каждый HDLC-контроллер имеет внутренние буферы FIFO. Данные из FIFO по SDMA-каналам под управлением RISC-контроллера начинают передаваться в соответствующие буферы памяти, как только будут получены первые 8-32 байта кадра. Если RISC-контроллер не успевает очищать ячейки FIFO для приема новой информации из сети и в момент прихода новой порции данных все ячейки FIFO окажутся занятыми, то возникает ошибка переполнения бусре-ров overrun. При этом контроллер будет вынужден записать новые данные поверх старых, что приведет к потере информации. Далее текущий буфер закрывается, в его слове состояния устанавливается бит ошибки переполнения OV := 1 и через регистр событий генерируется, если оно разрешено, прерывание к центральному процессору. В некоторых случаях, если размер FIFO минимален и RISC-контроллер работает с максимальной загрузкой, это прерывание может возникнуть при приеме и анализе поля адреса в любом пакете, даже если этот пакет адресован другому контроллеру. В случае возникновения ошибки переполнения контроллер после вышеуказанных действий переходит в режим «охоты» (поиска нового кадра).

Если кадр данных, адресованный данному контроллеру, был принят без ошибок, но RISC-контроллер не нашел свободных буферов для сохранения данных, то информация из кадра сбрасывается и увеличивается счетчик непринятых кадров в ячейке DISFC памяти параметров.

Во время приема кадра данных контроллер постоянно проверяет наличие сигнала на линии . Если во время приема этот сигнал будет потерян ( = 1), то контроллер прекращает прием, закрывает текущий буфер, устанавливает в слове состояния текущего BD бит потери сигнала (CD := 1) и генерирует, если разрешено, прерывание RXF через регистр событий. Эта ошибка имеет самый высокий приоритет, и после ее обнаружения другие ошибки не проверяются, а приемник переходит в режим поиска нового кадра (hunt-режим).

Длина всех полей в HDLC-кадре всегда кратна 8 битам. Если принят кадр с длиной, не кратной 8, то он сохраняется в буфере, затем буфер закрывается, устанавливается бит ошибки NO := 1 в слове состояния BD и генерируется, если разрешено, RXF-преры-вание центрального процессора через регистр событий контроллера. Результат проверки контрольной суммы этого кадра игнорируется.

Если во время приема кадра контроллер получил из канала подряд семь и более единичных бит, то регистрируется ошибка принятия ABORT-последовательности. Текущий буфер закрывается, в слове состояния BD устанавливается бит ошибки АВ := 1 и генерируется, если разрешено, прерывание RXF через регистр событий. Контроллер увеличивает счетчик принятых ABORT-последовательностей в ячейке ABTSC памяти параметров, и приемник переходит в режим «охоты». Принятый кадр игнорируется, проверка его контрольной суммы CRC и кратности 8 битам не производятся.

Передача данных. Для синхронизации станций в канале при включении в работу передатчик HDLC-контроллера начинает передавать символы флага (формат 01111110). Если установлен бит FSE = 1 и бит RTSM в регистре GSMR равен единице, то между кадрами передается [NOF+1] флагов. Если же бит RTSM = 0, то между кадрами передаются IDLE-символы.

Далее контроллер начинает опрашивать готовность первого буфера BD. Если буфер готов, то данные по SDMA-каналу загружаются в буфер FIFO канала. Передав заданное пользователем число символов флага между кадрами, контроллер начинает передавать данные из FIFO в сеть. Минимальное число символов, передаваемых между соседними кадрами, задается в битах NOF3 – NOF0. Если в этих битах записан код 0000, то открывающий флаг одного кадра следует сразу без интервала за закрывающим флагом предыдущего кадра.

Когда переданы все буферы текущего кадра, и контроллер обнаружил в слове состояния последнего буфера BD установленный бит L = 1 (Last), то он передает в канал контрольную сумму кадра и закрывающий флаг. Если биты CRC = 00, то контрольная сумма вычисляется с помощью 16-разрядного циклического кода. Если биты CRC = 10, то контрольная сумма вычисляется по 32-разрядному циклическому коду. Вид образующего полинома задается пользователем в ячейках C_MASK памяти параметров, где «1» в i-бите соответствует включению в полином слагаемого X в степени i. Для полинома Х16+Х12+Х5+1 в этой ячейке хранится код OxOOOFOB8, а для полинома Х32+ Х26+Х23+Х22+ Х16+Х12 + + Х11+Х10+Хв+Х7+Х5+Х4+Х2+Х1+1 - код 0xDEBB20E3. При инициализации параметров HDLC-контроллера в ячейку C_PRES памяти параметров записывается начальное значение счетчика CRC. Для 16-разрядного полинома это код 0x0000FFFF, а для 32-разрядного -0xFFFFFFFF. Пользователю не рекомендуется при работе изменять содержимое ячеек, связанных с настройкой работы счетчика CRC, так как это может привести к неправильному применению теории циклического кодирования.

Формирование контрольной суммы начинается сразу же при начале передачи первого бита кадра данных. Временные промежуточные значения контрольной суммы хранятся в ячейках TCRC памяти параметров при передаче и в ячейке RCRC - при приеме данных.

32-битная контрольная сумма часто используется, если необходимо пересылать пакеты между сетями HDLC и Ethernet. При согласовании форматов пакетов в узле коммутации целесообразно использовать одинаковый формат 32-разрядной CRC, чтобы упростить и ускорить преобразование форматов, а не тратить дополнительное время на перекодировку 16-разрядной контрольной суммы в 32-разрядную.

Если все данные из текущего буфера переданы в сеть, то RISC-контроллер сбрасывает бит готовности буфера R := 0 в слове состояния BD, чтобы центральный процессор мог в этом буфере подготовить новые данные для передачи. Если текущий буфер был еще и последним буфером кадра, то контроллер дополнительно устанавливает биты состояния кадра при передаче в слове состояния последнего буфера BD. Далее контроллер переходит к передаче данных из следующего буфера, если, конечно, в нем установлен бит готовности к передаче R = 1.

Если в слове состояния переданного буфера был установлен бит I = 1 (Interrupt), то после окончания передачи буфера будет генерироваться прерывание. Пользователь может гибко устанавливать требования прерывания после передачи каждого буфера, после передачи определенных буферов или после передачи всех буферов кадра.

Пользователь может в любой момент времени остановить передачу и переопределить содержимое буферов, передав контроллеру команду STOP TRANSMIT. Часто эта команда используется, когда надо передать более приоритетные кадры данных из других буферов, прервав передачу текущих данных, или в случае возникновения ошибки при передаче текущей информации. Для передачи более приоритетных кадров без прерывания передачи текущего кадра в СРМ предназначена команда GRACEFUL STOP TRANSMIT. Получив команду остановки передачи STOP TRANSMIT, HDLC-контроллер начинает передавать в канал или символы IDLE, или символы флага и ожидает получения команды RESTART TRANSMIT для возобновления передачи.

Если во время передачи обнаруживается ошибка, то HDLC-контроллер прерывает текущую передачу, закрывает буфер, устанавливает бит соответствующей ошибки в слове состояния BD и генерирует, если разрешено, ТХЕ-прерывание через регистр событий SCC-канала. Получив команду возобновления передачи RESTART TRANSMIT, контроллер продолжает дальнейшую передачу.

При передаче регистрируются два типа ошибок. Ошибка незаполнения буфера underrun возникает, если при передаче мультибуферных кадров данных центральный процессор не успел подготовить для передачи новые буферы, содержащие данные текущего кадра, а данные из последнего подготовленного буфера уже переданы в сеть. Признаком этой ошибки будет установка бита UN := 1 в слове состояния текущего BD.

При передаче HDLC-контроллер постоянно контролирует наличие сигнала = 0. Если этот сигнал будет сброшен ( = 1), то генерируется ошибка потери CTS-сигнала (ошибка коллизии). Признаком этой ошибки будет установка бита СТ := 1 в слове состояния текущего BD. Бит RTE в регистре конфигурации определяет действия контроллера при восстановлении сигнала = 0 после состояния коллизии. Если сигнал CTS был потерян при передаче двух первых буферов кадра и бит RTE = 1, то HDLC-контроллер просто начинает повторную передачу прерванного кадра данных и увеличивает на единицу счетчик повторных передач в ячейке RETRC памяти параметров контроллера. Если бит RTE = 0, то повторная передача не производится, и контроллер переходит к передаче следующего кадра. Для того чтобы механизм обнаружения коллизий и повторных передач был успешно применен, размер первых двух буферов данных должен быть не менее 36 байт для канала SCC1 и 20 байтов - для других SCC-каналов в контрол лере МРС860.

Сброс сигнала = 1 при передаче может служить признаком конца передачи текущего кадра. Но при передаче может сложиться ситуация, когда в буфере FIFO находятся данные от нескольких HDLC-кадров и тогда анализ состояния CTS-сигнала может быть проведен некорректно. Для исключения возможных ошибок в состав регистра режима СРМ введен бит MFF. Если этот бит равен нулю, то в буфере FIFO могут быть данные только одного кадра, и появление сигнала = 1 свидетельствует о завершении передачи текущего кадра. Если бит MFF = 1, то в буфере могут находиться данные от нескольких кадров, и для обнаружения конца передачи кадра производить анализ сигнала CTS бесполезно. Такой режим работы может быть удобен для случая, когда передаются небольшие кадры back-to-back (кадры, требующие немедленного возврата), или пользователь жестко фиксировал число флагов, передаваемых между кадрами. В этих случаях конец передачи кадра может быть проанализирован или вычислен на основе имеющейся информации.

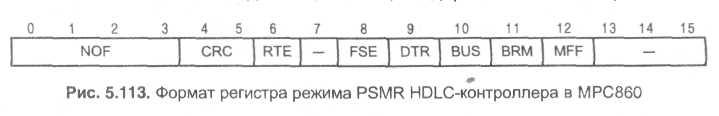

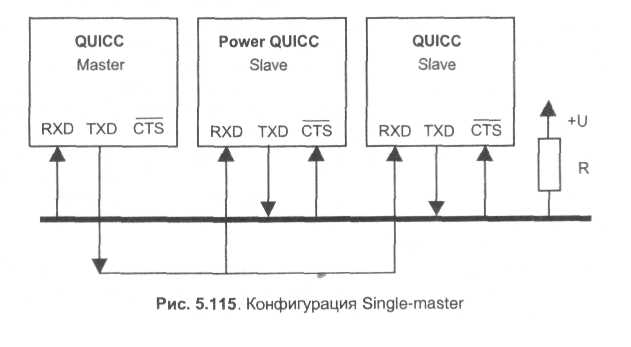

Контроллер HDLC bus. Контроллер HDLC bus - это расширение HDLC-протокола, позволяющее применять его в сетях с конфигураций point-to-point и point-to-multipoint. Протокол HDLC bus используется на канальном уровне управления как вариант HDLC-протокола, часто называемый LAPD, для работы в point-to-multipoint конфигурациях, так как контроллер HDLC может работать только в конфигурациях point-to-point. На физическом уровне управления протокол позволяет восьми терминалам получить доступ к S/T bus для передачи кадров. Контроль доступа к каналу связи производится через D-канал.

Контроллер HDLC bus позволяет создавать сеть небольшого размера, при этом выходы TxD станции должны быть сконфигурированы как выходы open-drain, чтобы было возможно объединять их в общую шину. Контроллер HDLC bus может работать с внешними контактами или в режиме NMSI, или в режиме TDM bus.

Устройства S/T-интерфейса проверяют незанятость канала передачи, просматривая состояние «эхо»-бита на линии. В «эхо»-бите отражаются все биты, которые недавно передавались по D-каналу. В зависимости от класса терминала устройства могут ожидать получение от 7 до 10 единичных битов на «эхо»-бите канала, перед тем как начать передачу LAPD-кадра. Наличие 7-10 последовательных «1» в канале свидетельствует о том, что в канале нет передачи данных и идет передача IDLE-последовательностей. Контроллер HDLC bus поддерживает формат кадра HDLC, а значит максимальное число последовательных «1» в кадре не может превышать шести, так как после каждых пяти последовательных «1» в кадре происходит вставка «0» (операция bit-stuffing).

После начала передачи станция постоянно контролирует, что она передала, читая «эхо»-бит. В контроллере HDLC bus механизм «эхо»-бита реализован через внешние контакты. Вывод TxD соединен с контактом .Контроллер передает данные на контакт TxD и контролирует их с контакта . Передача продолжается, пока бит, который станция передала, совпадает с битом, который станция прочитала («эхо»-бит). Если эти биты не совпадают, возникает состояние коллизии между терминалами. При этом станции, которые передавали нулевой бит, прекращают передачу, а станции, которые передавали единичный бит, продолжают передачу. Для того чтобы уменьшить вероятность возникновения коллизии и захвата шины одной станцией, после завершения передачи станции понижают свой приоритет, чтобы разрешить другим станциям доступ к шине.

Основные отличия протокола HDLC bus:

• протокол HDLC bus поддерживает все другие протоколы, которые базируются на HDLC-кадре; таким образом, в сети могут одновременно работать несколько станций, которые используют различные варианты HDLC-протокола;

• станции HDLC bus могут объединяться в сеть с HDLC-станциями для совместной работы;

перед началом передачи контроллер HDLC bus ожидает получение или 8, или 10 единичных битов, чтобы убедиться, что канал передачи свободен;

HDLC bus позволяет строить более короткие по размерам сети; это ограничение связано с типом выхода контакта TxD, так как выход open-drain требует дополнительного со противления, подключенного к источнику питания, и ориентирован на небольшие сети;

карта памяти параметров контроллера HDLC bus полностью совпадает с картой памяти обычного HDLC-контроллера; таким образом, основные режимы функционирова ния контроллеров HDLC и HDLC bus совпадают.

Доступ к HDLC bus. Для доступа к шине контроллер HDLC bus подсчитывает число единичных битов, полученных по линии контакта . Если на этом контакте обнаружен «0», то счетчик единиц сбрасывается. Наличие «0» на линии данных может свидетельствовать о том, что кто-то уже начал передачу, послав открывающий флаг кадра формата 01111110. Если два и более передатчиков пытаются получить доступ к шине, то возникает состояние коллизии. В этом случае только один передатчик продолжит передачу, а остальные ее прервут. В дальнейшем контроллер HDLC bus обеспечит автоматическую повторную передачу для передатчиков, работа которых была прервана во время коллизии.

Если с линии получено восемь последовательных единичных бит, то передатчик считает канал свободным и начинает свою передачу. При передаче данные на контакт TxD выставляются по отрицательному перепаду сигнала TCLK, а сигнал читается по следующему положительному перепаду тактового сигнала. Если значение бита, переданного на линию TxD, совпадает со значением бита, полученного по линии , то передача бита прошла успешно. Поскольку контроллер HDLC bus использует схему «монтажное ИЛИ» для соединения выходов TxD, то передача «0» всегда имеет больший приоритет, чем передача «1», поэтому коллизия обнаруживается, только если TxD = 1, a = 0 и в этом случае контроллер прекращает текущую передачу. Если в формат HDLC-кадра включен адрес отправителя, то коллизия будет обнаружена не позднее конца передачи адреса источника.

Для того чтобы избежать захвата канала передачи одной станцией, введен приоритетный механизм. Станция, которая только что закончила передачу, ожидает не 8, а 10 последовательных «1» из канала перед тем, как начать новую передачу. Это задержка в два дополнительных бита дает другим станциям возможность выйти в сеть для передачи. Если станция обнаружила в сети 10 последовательных «1», то она повторно выходит в сеть для передачи новой информации, снижая обратно свое время ожидания до 8 единичных битов, так как никакая другая станция за этот интервал времени не начала свою передачу.

Протяженность сети HDLC bus зависит от метода подключения станции в сети. Так как выходы TXD объединены в «монтажное ИЛИ», и на них данные выставляются по отрицательному переходу сигнала TCLK, а сигнал считывается по положительному переходу тактового сигнала, то протяженность сети зависит от длительности нулевого полупериода тактового сигнала, поскольку за это время сигнал с линии TXD должен успеть дойти до самой удаленной станции в сети, иначе при анализе сигнала на линии может произойти ошибка, и возникшая коллизия не будет обнаружена. Для увеличения протяженности сети рекомендуется использовать несимметричный тактовый сигнал, у которого длительность «1» короче длительности «О» полупериода.

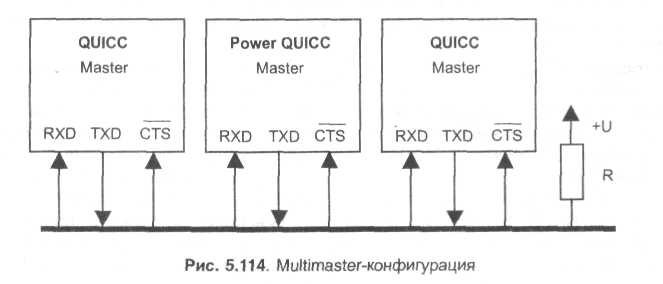

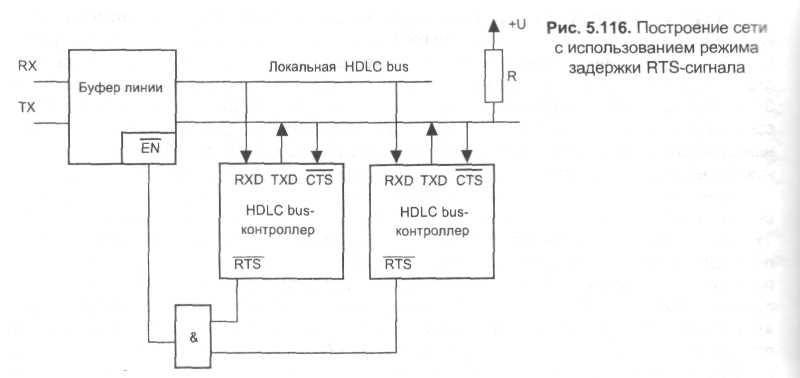

Для того чтобы обеспечить доступ локальной сети HDLC bus к сетям, которые не являются сетью HDLC bus, в контроллере реализован режим работы «задержки RTS-сигнала». Обычно сигнал = 0 выставляется при начале передачи первого бита открывающего флага, и этот сигнал не используется для построения сети HDLS bus. Но в контроллере МРС860 введен дополнительный режим работы «задержки RTS-сигнала» на 1 бит, если установлен бит BRM = 1 в регистре PSMR. В этом режиме данные на линию передаются как обычно, но сигнал = 0 выставляется с задержкой на один период тактовой частоты. Наличие сигнала RTS = 0 можно использовать для открытия буфера (рис. 5.116). Введение режима задержки -сигнала позволяет не пропускать во внешнюю сеть первый бит кадра, который используется для обнаружения коллизий и не является битом данных. В этой схеме контроллеры HDLC bus не взаимодействуют друг с другом, но могут передавать информацию во внешнюю сеть. При этом выходы TXD всех контроллеров должны быть объединены и настроены на режим open-drain. А все RTS-выводы должны быть настроены на режим работы с задержкой.

Если включен режим задержки RTS, то этот сигнал появляется активным ( = 0) с задержкой на 1 бит относительно момента выставления битов данных. Таким образом, за этот такт задержки контроллеры HDLC bus определяют, есть коллизия или нет. Если коллизия возникла, то сигнал = 1 и выхода на внешнюю сеть нет. Если коллизии нет, то данные передаются во внешнюю сеть, так как сигнал = 0 откроет буфер.

Если необходимо организовать доступ из локальной сети HDLS bus к сети, которая работает с TDM-каналами передачи, то можно применить схему, похожую на схему рис. 5.117. Отличие заключается в том, что нет необходимости использовать сигнал RTS. Просто в каждом контроллере HDLC bus производится настройка его TSA-блока в последовательном интерфейсе SI на работу с определенным временным слотом. К каждому временному слоту может быть подключено произвольное число контроллеров HDLC bus. Локальные контроллеры HDLC bus не смогут общаться друг с другом, но смогут передавать информацию на внешний TDM-канал. Данные будут передаваться по контакту L1TXD и приниматься по линии L1RXD. Коллизия будет обнаруживаться через линию , но этот сигнал следует анализировать только во время наступления выбранного временного слота (см. рис 5.117).