mov [bx+0d9feh], 0b6ceh | 81 AD D9 C6 BD A2

============== №1 Ассемблирование – mov [bx+0d9feh], 0b6ceh =============

Комментарий к команде: M(DS:Bx+0D9FEh) ← 0B6CEh

1-й байт(код операции):

из табл. команд, № 7 находим КОП 11000111b=C7h, w=1, т. к. длина операнда 16 бит.

2-й байт(постбайт):

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0d9feh);

000 – reg: поле reg содержит расширение КОП (1-й байт);

111 – reg/mem: поле reg/mem =111, т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: ЕА=BX+disp= BX+0D9FEh.

Получаем второй байт: 10000111=87h.

3-й байт(dispLow):

FEh.

4-й байт(dispHigh):

D9h

5-й байт(dataLow):

CEh

6-й байт(dataHigh):

B6h

Машинный код команды: C7 87 FE D9 CE B6

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базовая, где BX – база, 0d9feh – смещение относительно базы.

Правый операнд – непосредственная, 0b6ceh – непосредственный 16-и битный операнд.

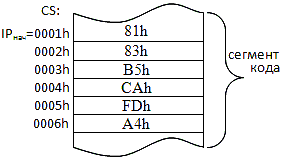

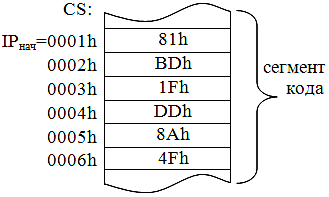

Размещение команды в памяти:

|

Время выполнения команды: Время выполнения в тактах: nТ = (n+Tиа) = 10+Tиа, где Tиа – время вычисления эффективного адреса: EA = BX+0D9FEh. По таблице 11 находим, что для базовой адресации Tиа = 9, тогда nТ = 10+9 = 19 тактов. Время выполнения команды в секундах: Tk = (n+Tиа)*tТ = nТ*tТ = 19*10-8 = 0,19 мкс, где tТ = 1/fТ = 1/100000000 = 10-8.

|

=============== №2 Дизассемблирование – (81 AD D9 C6 BD A2) ===============

Задание: 81 AD D9 C6 BD A2

Длина команды: 6 байт.

1-й байт(код операции):

1000 0001b=81h –SUB (r/m <- r/m-data), поле w=1, т.е. операнд 16-ми разрядный.

2-й байт(постбайт):

1010 1101b=ADh, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0c69dh);

101 – reg

101 – reg/mem, mod=10: левый операнд – DI+disp

3-й байт(dispLow):

D9

4-й байт(dispHigh):

С6

5-й байт(dataLow):

BD

6-й байт(dataHigh):

А2

Мнемоника команды: SUB [word DI+0C6D9h], 0A2BDh

Адрессация операндов:

Левый оператор – индексная, где DI – индекс, 0C6D9h – смещение

Правый оператор – непосредственная, 0A2BDh – непосредственное значение

Комментарий к команде: M(DS:DI+0C6D9h) <- M(DS:DI+0C6D9h)- 0A2BDh

Размещение команды в памяти:

|

Время выполнения: Время выполнения в тактах: nТ=(n+Tиа)=8+Tиа, где Tиа – время вычисления эффективного адреса: EA=DI+disp16. По таблице 11 находим, что Tиа=9, тогда nТ=8+9=17 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=17*10-8=0,17 мкс, где tТ=1/fТ=1/100000000=10-8.

|

================ №3 Навести команду мікропроцесора x86… ===============

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки необхідно інвертувати парні біти (тобто 0-й, 2-й, 4-й, 6-й), то маска буде мати вигляд 01010101. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL,01010101:

-

XOR

Х

0

Х

1

Х

0

Х

1

Х

0

Х

1

Х

0

Х

1

Х

Х

Х

Х

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, парні біти якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 30 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 30-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 30*4 = 120D = 0001111000В. Таким чином повна 20-и розрядна фізична адреса обробника 30-ого переривання має вигляд: 00000000000001111000В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики (прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -15 буде віднято 46, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -15-46 можна замінити операцією -15+(-46). Для цього треба представити число -46 в додатковому коді: записуємо модуль цього числа в двійковій формі: 46D = 00101110B; інвертуємо отриманий результат: 11010001В; додаємо до отриманої комбінації одиницю:

-

+

1

0

1

0

0

0

1

0

0

0

0

0

0

0

1

1

1

1

0

1

0

0

1

0

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11010010В = 1 + 4 + 8 + 3 2 = 45. До отриманого результату додаємо одиницю і отримуємо 46, а оскільки знаковий розряд = 1, то маємо -46. Переведення в додатковий код виконано вірно. Таким же чином переведемо -15 в додатковий код: 15D = 00001111B; інвертуємо: 11110000В; додаємо одиницю: 11110001B. Робимо перевірку: 11110001B = 2 + 4 + 8 = 14. До отриманого результату додаємо одиницю і отримуємо 15, а оскільки знаковий розряд = 1, то маємо -15. Виконуємо операцію додавання над числами в додатковому коді:

-

+

1

1

1

1

0

1

1

1

0

0

0

0

1

0

0

1

1

1

1

0

0

0

0

1

1

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

-

+

1

1

1

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

0

0

0

0

1

0

Переведемо отриманий результат з додаткового коду в десяткову систему:

111000010 = (32 + 16 + 8 + 4 + 1) + 1 = 62D.

Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -62.

ADD [DI+0C5BDh], 0D36Ah | 81 BC 9F 4B CD DB

============ №1 Ассемблирование – ADD [DI+0C5BDh], 0D36Ah ============

Комментарий к команде: M(DS:DI+0C5BDh) ← M(DS:DI+0C5BDh) + 0D36Ah

1-й байт(код операции):

из табл. команд, № 7 находим КОП 100000swb = 10000001b = 81h, sw=01, т. к. длина операнда 16 бит.

2-й байт(постбайт):

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0C5BDh);

000 – reg: поле reg содержит расширение КОП (1-й байт);

101 – reg/mem: поле reg/mem =101, т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: ЕА=DI+disp.

Получаем второй байт: 10000101=85h.

3-й байт(dispLow):

BDh.

4-й байт(dispHigh):

C5h

5-й байт(dataLow):

6Ah

6-й байт(dataHigh):

D3h

Машинный код команды: 81 85 BD C5 6A D3

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базовая, где DI – база, 0C5BDh – смещение относительно базы.

Правый операнд – непосредственная, 0D36Ah – непосредственный 16-и битный операнд.

Размещение команды в памяти:

|

Время выполнения команды: Время выполнения в тактах: nТ = (n+Tиа) = 4/17+Tиа, где Tиа – время вычисления эффективного адреса. По таблице 11 находим, что для базовой адресации Tиа = 9, тогда nТ = 17+9 = 26 тактов. Время выполнения команды в секундах: Tk = (n+Tиа)*tТ = nТ*tТ = 26*10-7 = 2,6 мкс, где tТ = 1/fТ = 1/10000000 = 10-7.

|

=============== №2 Дизассемблирование – (81 BC 9F 4B CD DB) ===============

Задание: 81 BC 9F 4B CD DB

Длина команды: 6 байт.

1-й байт(код операции):

1000 0001b=81h – CMP (r/m – data), поле w=1, т.е. операнд 16-ми разрядный.

2-й байт(постбайт):

1011 1100b=BCh, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение;

111 – reg

100 – reg/mem, mod=10: левый операнд – SI+disp

3-й байт(dispLow):

9F

4-й байт(dispHigh):

4B

5-й байт(dataLow):

CD

6-й байт(dataHigh):

DB

Мнемоника команды: CMP [word SI+04B9Fh], 0DBCDh

Адресация операндов:

Левый операнд – базовая, где SI – база, 04B9Fh – смещение

Правый операнд – непосредственная, 0DBCDh – непосредственное значение

Комментарий к команде: M(DS:SI+04B9Fh) – 0DBCDh

Размещение команды в памяти:

|

Время выполнения: Время выполнения в тактах: nТ=(n+Tиа)=17+Tиа, где Tиа – время вычисления эффективного адреса: EA=SI+disp16. По таблице 11 находим, что Tиа=9, тогда nТ=17+9=26 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=26*10-7=2,6 мкс, где tТ=1/fТ=1/10000000=10-7. |

================ №3 Навести команду мікропроцесора x86… ===============

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки необхідно інвертувати непарні біти (тобто 1-й, 3-й, 5-й, 7-й), то маска буде мати вигляд 10101010. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL,10101010:

-

XOR

Х

1

Х

0

Х

1

Х

0

Х

1

Х

0

Х

1

Х

0

Х

Х

Х

Х

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, непарні біти якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 32 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 30-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 32*4 = 128D = 0010000000В. Таким чином повна 20-и розрядна фізична адреса обробника 30-ого переривання має вигляд: 00000000000010000000В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики (прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -20 буде віднято 44, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -20-44 можна замінити операцією -20+(-44). Для цього треба представити число -44 в додатковому коді: записуємо модуль цього числа в двійковій формі: 44D = 00101100B; інвертуємо отриманий результат: 11010011В; додаємо до отриманої комбінації одиницю:

-

+

1

0

1

0

0

0

1

0

0

0

0

0

1

0

1

1

1

1

0

1

0

1

0

0

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11010100В = 1 + 2 + 8 + 3 2 = 43. До отриманого результату додаємо одиницю і отримуємо 44, а оскільки знаковий розряд = 1, то маємо -44. Переведення в додатковий код виконано вірно. Таким же чином переведемо -20 в додатковий код: 20D = 00010100B; інвертуємо: 11101011В; додаємо одиницю: 11101100B. Робимо перевірку: 11101100B = 1 + 2 + 16 = 19. До отриманого результату додаємо одиницю і отримуємо 20, а оскільки знаковий розряд = 1, то маємо -20. Виконуємо операцію додавання над числами в додатковому коді:

-

+

1

1

1

1

0

1

1

0

0

1

1

1

0

0

0

0

1

1

1

0

0

0

0

0

0

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

-

+

1

1

1

1

0

1

0

1

0

1

0

1

0

1

0

1

1

1

0

1

1

1

1

1

1

Переведемо отриманий результат з додаткового коду в десяткову систему:

110111111 = 64 + 1 = 65D.

Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -65.

sub [bx + 0bc5fh], 0e78dh | 81 83 B5 CA FD A4

============= №1 Ассемблирование – sub [bx + 0bc5fh], 0e78dh =============

Комментарий к команде: M(DS*16+ bx + 0bc5fh) - 0e78dh

r/m r/m – data

1-й байт(код операции):

из табл. комманд находим КОП 100000sw =10000001 = 81h

sw=01, так как есть data H.

2-й байт(постбайт):

md101 r/m = 10101111 = AFh

md = 10, так как смещение disp = 16 біт;

r/m = 111, так как исполнительній адрес = bx+disp

3-й байт:

Молодший байт від disp із першого операнду = 5Fh

4-й байт:

Старший байт від disp із першого операнду = BCh

5-й байт:

Молодший байт від другого операнду = 8Dh

6-й байт:

Старший байт від другого операнду = E7h

Машинный код команды: 81 AF 5F BC 8C 8D E7

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базовая, где BX – база

Правый операнд – непосредственная

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)= 4/17+TИА, где Tиа – время вычисления эффективного адреса: EA=BX+0bc5fh. По таблице 11 находим, что для базовой адресации Tиа=9, тогда nТ=17+9=26 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=26*10-8=0,26 мкс, где tТ=1/fТ=1/100000000=10-8.

|

=============== №2 Дизассемблирование – (81 83 B5 CA FD A4) ==============

Задание: 81 83 B5 CA FD A4

Длина команды: 6 байт.

1-й байт(код операции):

1000 0001b=81h – ADD (r/mr/m+data),

sw=01, т.е. операнд ы 16-ми разрядные.

2-й байт(постбайт):

1000 0011b=83h, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0CAB5h);

011 – reg/mem, mod=10: левый операнд – BP+DI+disp

3-й байт(dispLow):

B5

4-й байт(dispHigh):

CA

5-й байт(dataLow):

FD

6-й байт(dataHigh):

A4

Мнемоника команды: ADD [BP+DI +0CAB5h], 0 A4FDh

Адрессация операндов:

Левый операнд – базово-индексная со смещением

Правый операнд – непосредственная

Размещение команды в памяти:

|

Время выполнения Время выполнения в тактах: nТ=(n+Tиа)=8+Tиа, где Tиа – время вычисления эффективного адреса: EA= BP+DI +data16. По таблице 11 находим, что Tиа=11, тогда nТ=17+11=28 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=17*10-8=0,28 мкс, где tТ=1/fТ=1/100000000=10-8. |

================ №3 Навести команду мікропроцесора x86… ===============

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Маска буде мати вигляд 00010101. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL, 01010101:

-

XOR

Х

0

Х

1

Х

0

Х

1

Х

0

Х

1

Х

0

Х

1

Х

Х

Х

Х

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, парні біти якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 33 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 30-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 33*4 = 132D = 0010000100В. Таким чином повна 20-и розрядна фізична адреса обробника 33-ого переривання має вигляд: 00000000000010000100В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -25 буде віднято 42, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -15-42 можна замінити операцією -15+(-46). Для цього треба представити число -42 в додатковому коді: записуємо модуль цього числа в двійковій формі: 42D= 00101010B; інвертуємо отриманий результат: 11010101В; додаємо до отриманої комбінації одиницю:

+ |

1 0 |

1 0 |

0 0 |

1 0 |

0 0 |

1 0 |

0 0 |

1 1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11010110В = 1+8+32=41. До отриманого результату додаємо одиницю і отримуємо 42, а оскільки знаковий розряд = 1, то маємо -42.

Переведення в додатковий код виконано вірно. Таким же чином переведемо -25 в додатковий код: 25D = 00011001B; інвертуємо: 11100110В; додаємо одиницю: 11100111B. Робимо перевірку:

11100111B = 8 + 16 = 24. До отриманого результату додаємо одиницю і отримуємо 25, а оскільки знаковий розряд = 1, то маємо -25. Виконуємо операцію додавання над числами в додатковому коді:

+ |

1 1 |

1 1 |

0 1 |

1 0 |

0 0 |

1 1 |

1 1 |

0 1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

+ |

1 1 |

0 1 |

1 1 |

1 1 |

1 1 |

1 1 |

0 1 |

1 1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

Переведемо отриманий результат з додаткового коду в десяткову форму:

110111100В = (64 + 2 + 1) + 1 = 68D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -68.

add [si + 0e56fh], 0f13eh | C7 80 DC CC 6C D3

============ №1 Ассемблирование – add [si + 0e56fh], 0f13eh =============

Комментарий к команде: M(DS:si+0E56Fh)←0F13Eh

1-й байт(код операции):

З табл. команд № 4 знаходимо КОП 100000sw, розширення знаком молодшого байта з 8-розрядної до 16-розрядної константи не відбувається, тому s=0. w=1, бо довжина операнда 16 біт.

10000001b=81h

2-й байт(постбайт):

md000r/m

поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0e56h);

так як використовується індексна адресація вигляду (SI)+data16, то mod=10, r/m=100, разом

10000100b=84h

3-й байт(dispLow):

6fh.

4-й байт(dispHigh):

e5h

5-й байт(dataLow):

3eh

6-й байт(dataHigh):

f1h

Машинный код команды: 81 84 6F E5 3E F1

Длина команды: 6 байт.

Способы адресации операндов:

Левый операнд – индексная, где SI – индекс, 0e56fh – смещение относительно индекса.

Правый операнд – непосредственная, 0f13eh – непосредственный 16-ти битный операнд.

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)=17+Tиа, где Tиа – время вычисления эффективного адреса: EA= si + 0e56fh. По таблице 11 находим, что для индексной адресации Tиа=9, тогда nТ=17+9=26 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=26*10-7=2,6 мкс, где tТ=1/fТ=1/10000000=10-7.

|

=============== №2 Дизассемблирование – (C7 80 DC CC 6C D3) ===============

Задание: C7 80 DC CC 6C D3

Длина команды: 6 байт.

1-й байт(код операции):

C7h=11000111b – MOV (r/m<-data) , поле w=1, т.е. операнд 16-ти разрядный.

2-й байт(постбайт):

80h=10000000b,

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение;

000 – reg/mem, mod=10: левый операнд – (BX)+(SI) + DATA16

3-й байт(dispLow):

DC

4-й байт(dispHigh):

CC

5-й байт(dataLow):

6C

6-й байт(dataHigh):

D3

Мнемоника команды: MOV [BX+SI+0CCDCh], 0D36Ch

Адрессация операндов:

левый – базово-индексная со смещением, где DI – индекс, BX - база, 0CCDCh – смещение

правый – непосредственная, 0D36Ch – непосредственное значение

Комментарий к команде: M(DS: BX+SI+0CCDCh) <- 0D36Ch

Размещение команды в памяти:

|

Время выполнения в тактах: nТ=(n+Tиа)=10+Tиа, где Tиа – время вычисления эффективного адреса: EA=(BX)+(SI) + DATA16. По таблице 11 находим, что Tиа=11, тогда nТ=10+11=21 такт. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=21*10-7=2,1 мкс, где tТ=1/fТ=1/10000000=10-7.

|

================ №3 Навести команду мікропроцесора x86… ===============

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки необхідно інвертувати біти №2, 4, 6, то маска буде мати вигляд 01010100. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL,01010100:

X X X X X X X X

0 1 0 1 0 1 0 0

X

X

X

X

X

X

X

Як бачимо, внаслідок виконання команди в регістр AL буде поміщена комбінація, 2, 4, 6 біти якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 35 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво (множення на 4) номеру переривання. Так для 35-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 35*4 = 140D = 0010001100В. Таким чином, повна 20-ти розрядна фізична адреса обробника 35-ого переривання має вигляд: 00000000000010001100В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -30 буде віднято 40, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -30-40 можна замінити операцією -30+(-40). Для цього треба представити число -40 в додатковому коді: записуємо модуль цього числа в двійковій формі: 40D= 00101000B; інвертуємо отриманий результат: 11010111В; додаємо до отриманої комбінації одиницю:

11010111

1

11011000

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11011000В = 1+2+4+32=39. До отриманого результату додаємо одиницю і отримуємо 40, а оскільки знаковий розряд = 1, то маємо -40. Переведення в додатковий код виконано вірно. Таким же чином переведемо -30 в додатковий код: 30D = 00011110B; інвертуємо: 11100001В; додаємо одиницю: 11100010B. Робимо перевірку: 11100010B = 1+4+8+16=29. До отриманого результату додаємо одиницю і отримуємо 30, а оскільки знаковий розряд = 1, то маємо -30. Виконуємо операцію додавання над числами в додатковому коді:

11011000

11100010

1 10111010

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10111010

11111111

1 10111001

Переведемо отриманий результат з додаткового коду в десяткову форму: 110111001В = 2+4+64+1=71D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -71.

mov [bp+ di + 0185dh], 0f65dh | 81 B4 F2 D2 8F CD

============ №1 Ассемблирование – mov [bp+ di + 0185dh], 0f65dh ===========

Комментарий к команде: M(DS:bp+ DS:di+0185dh) ←0f65dh

1-й байт(код операции):

из табл. комманд, № 7 находим КОП 11000011b=C7h, w=1, т. к. длина операнда 16 бит.

2-й байт(постбайт):

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0D9FEh);

000 – reg: поле reg содержит расширение КОП (1-й байт);

011 – reg/mem: поле reg/mem =011, т.к. для вычисления EA используется bp и si

Получаем второй байт: 10000011=83h.

3-й байт(dispLow):

5Dh.

4-й байт(dispHigh):

18h

5-й байт(dataLow):

5Dh

6-й байт(dataHigh):

F6h

Машинный код команды: C7 83 5d 18 5d f6

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базово-индексная со смещением, bp-база, di-индекс, 185dh -смещение

Правый операнд – непосредственная, 0f65dh – непосредственный 16-и битный операнд.

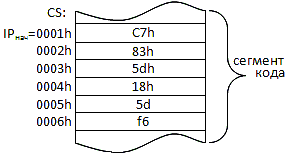

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)=10+Tиа, где Tиа – время вычисления эффективного адреса: EA=bp+di+0185dh. По таблице 11 находим, что для базовой адресации Tиа=11, тогда nТ=10+11=21 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=21*10-8=0,21мкс, где tТ=1/fТ=1/100000000=10-8. |

=============== №2 Дизассемблирование – (81 B4 F2 D2 8F CD) ===============

Задание: 81 B4 F2 D2 8F CD

Длина команды: 6 байт.

1-й байт(код операции):

1000 0001b=81h –XOR r/m r/mdata, поле w=1, т.е. операнд 16-ти разрядный.

2-й байт(постбайт):

10110100b= B4h, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0c69dh);

110 – reg

100 – r/m, mod=10: левый операнд – (SI) + disp16

3-й байт(dispLow):

F2

4-й байт(dispHigh):

D2

5-й байт(dataLow):

8F

6-й байт(dataHigh):

CD

Мнемоника команды: XOR [word SI+D2F2h], CD8Fh

Адресация операндов:

Левый операнд – индексная, где SI – индекс, D2F2h – смещение

Правый операнд – непосредственная, CD8Fh – непосредственное значение

Комментарий к команде: M(ES:SI+0 D2F2h) ← M(ES:SI+0 D2F2h) & 0CD8Fh

Размещение команды в памяти:

|

Время выполнения Время выполнения в тактах: nТ=(n+Tиа)=17+Tиа, где Tиа – время вычисления эффективного адреса: EA=SI+disp16. По таблице 11 находим, что Tиа=9, тогда nТ=17+9=26 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=26*10-8=0,26мкс, где tТ=1/fТ=1/100000000=10-8. |

=============== №3 Навести команду мікропроцесора x86… ================

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки необхідно інвертувати 1-й,2-й,7-й,8-й біти, то маска буде мати вигляд 01100011. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL,01010101:

Х 1 |

Х 1 |

Х 0 |

Х 0 |

Х 0 |

Х 0 |

Х 1 |

Х 1 |

|

|

Х |

Х |

Х |

Х |

|

|

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, відповідні біти якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 42 ===============

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 42-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 42*4 = 168D = 0010101000В. Таким чином повна 20-и розрядна фізична адреса обробника 30-ого переривання має вигляд: 00000000000010101000В.

============== №5 Виконати функцію … команди SBB AL, data8 =============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -35 буде віднято 38, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -35-38 можна замінити операцією -35+(-38). Для цього треба представити число -38 в додатковому коді: записуємо модуль цього числа в двійковій формі: 38D= 00100110B; інвертуємо отриманий результат: 11011001В; додаємо до отриманої комбінації одиницю:

-

1

0

1

0

0

0

1

0

1

0

0

0

0

0

1

1

1

1

0

1

1

0

1

0

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11011010В = 1+4+32=37. До отриманого результату додаємо одиницю і отримуємо 38, а оскільки знаковий розряд = 1, то маємо -38. Переведення в додатковий код виконано вірно. Таким же чином переведемо -35 в додатковий код: 35D = 00100011B; інвертуємо: 11011100В; додаємо одиницю: 11011101B. Робимо перевірку: 11011101B = 2+32=34. До отриманого результату додаємо одиницю і отримуємо 35, а оскільки знаковий розряд = 1, то маємо -35. Виконуємо операцію додавання над числами в додатковому коді:

-

1

1

1

1

0

0

1

1

1

1

1

0

0

1

1

0

1

1

0

1

1

0

1

1

1

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

-

+

1

1

0

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

0

1

1

0

1

1

0

Переведемо отриманий результат з додаткового коду в десяткову форму:

10110110В = (64 + 8 + 1) + 1 = 74D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -74.

test [bx + 0e26bh], 0ffffh | F7 81 CC C5 FF FF

============= №1 Ассемблирование – test [bx + 0e26bh], 0ffffh ===============

Комментарий к команде: M(D:bx+0e26bh) & 0ffffh

1-й байт(код операции):

из табл. Команд находим КОП 11110111b=F7h, w=1, т. к. длина операнда 16 бит.

2-й байт(постбайт):

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0e26bh);

000 – reg: поле reg содержит расширение КОП (1-й байт);

111 – reg/mem: поле reg/mem =111, т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: ЕА=BX+disp= BX+0e26bh.

Получаем второй байт: 10000111=87h.

3-й байт(dispLow):

6Bh.

4-й байт(dispHigh):

E2h

5-й байт(dataLow):

FFh

6-й байт(dataHigh):

FFh

Машинный код команды: F7 87 6B E2 FF FF

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базовая, где BX – база, 0e26bh – смещение относительно базы.

Правый операнд – непосредственная, 0ffffh – непосредственный 16-и битный операнд.

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)=10+Tиа, где Tиа – время вычисления эффективного адреса: EA=BX+0e26bh. По таблице 11 находим, что для базовой адресации Tиа=9, тогда nТ=10+9=19 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=19*10-7=1,9 мкс, где tТ=1/fТ=1/100000000=10-7.

|

============= №2 Дизассемблирование – (F7 81 CC C5 FF FF B) ==============

Длина команды: 6 байт.

1-й байт(код операции):

11110111b=F7h –TEST (r/m & data), поле w=1, т.е. операнд 16-ти разрядный.

2-й байт(постбайт):

10000001b=81h, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0c5cch);

000 – reg

001 – reg/mem, mod=10: левый операнд – BX+DI+disp

3-й байт(dispLow):

C5

4-й байт(dispHigh):

СC

5-й байт(dataLow):

FF

6-й байт(dataHigh):

FF

Мнемоника команды: TEST [bx + di + 0C5CCh], 0FFFFh

Адрессация операндов:

левый – базово-индексная со смещением, bx – база, di –индекс, 0C5CCh – смещение.

правый – непосредственная, 0FFFFh – непосредственное значение

Комментарий к команде: M(DS: BX+DI+0C5CCh)& 0FFFFh

Размещение команды в памяти:

|

Время выполнения Время выполнения в тактах: nТ=(n+Tиа)=10+Tиа, где Tиа – время вычисления эффективного адреса: EA=DI+disp16. По таблице 11 находим, что Tиа=12, тогда nТ=10+12=22 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=22*10-7= 2.2 мкс, где tТ=1/fТ=1/100000000=10-7.

|

================ №3 Навести команду мікропроцесора x86… ===============

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки необхідно інвертувати біти(3-й,4-й,6-й,7-й) то маска буде мати вигляд 11011000. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL, 11011000b:

X X X X X X X X

1 1 0 1 1 0 0 0

X X X X

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, парні біти якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 45 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0 до 255 і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 45-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 45*4 = 180 = 0010110100b. Таким чином повна 20-и розрядна фізична адреса обробника 45-ого переривання має вигляд: 00000000000010110100b.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -40 буде віднято 36, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -40-36 можна замінити операцією -40+(-36). Для цього треба представити число 36 в додатковому коді: записуємо модуль цього числа в двійковій формі: 36= 00100100b; інвертуємо отриманий результат: 11011011В; додаємо до отриманої комбінації одиницю:

11011011

1

1 1011100

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11011100b= 1+2+32=35. До отриманого результату додаємо одиницю і отримуємо 36, а оскільки знаковий розряд = 1, то маємо -36. Переведення в додатковий код виконано вірно. Таким же чином переведемо -40 в додатковий код: 40 = 00101000B; інвертуємо: 11010111В; додаємо одиницю: 11011000B. Робимо перевірку: 11011000B = 1+2+4+32=39. До отриманого результату додаємо одиницю і отримуємо 40, а оскільки знаковий розряд = 1, то маємо -40. Виконуємо операцію додавання над числами в додатковому коді:

11011100

1 1011000

110110100

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10110100

11111111

110110011

Переведемо отриманий результат з додаткового коду в десяткову форму: 110110011b = 4+8+64+1=77. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -77.

7. sub [bx + si + 0f913h], 0e22dh | 81 87 D8 78 E4 F8

========== №1 Ассемблирование – sub [bx + si + 0f913h], 0e22dh ===========

Комментарий к команде: M(DS:bx+ si + f913) ←0e22dh

1-й байт(код операции):

из табл. 2.2.5.3 комманд, № 15 находим КОП 10000001b=81h, w=1, s=0 т. к. длина операнда 16 бит.

2-й байт(постбайт):

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0f913h);

101– reg: поле reg содержит расширение КОП (1-й байт);

000 – reg/mem: поле reg/mem =000, т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: ЕА=BX+SI+disp= BX+SI+0f913h.

Получаем второй байт: 10101000=A8h

3-й байт(dispLow):

13h.

4-й байт(dispHigh):

f9h

5-й байт(dataLow):

2dh

6-й байт(dataHigh):

e2h

Машинный код команды: 81 A8 13 f9 2d e2

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базово-индексная, где BX – база,SI-индекс, 0f913h – смещение относительно базы и индекса.

Правый операнд – непосредственная, 0e22dh – непосредственный 16-и битный операнд

Размещение команды в памяти:

|

Время выполнения в тактах: nТ=(n+Tиа)=10+Tиа, где Tиа – время вычисления эффективного адреса: EA=BX+4. По таблице 11 находим, что для базово-индексной адресации Tиа=11, тогда nТ=10+11=21 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=21*10-7=0,21 мкс, где tТ=1/fТ=1/10000000=10-7.

|

=============== №2 Дизассемблирование – (81 87 D8 78 E4 F8) ===============

Задание: 81 87 D8 78 E4 F8

Длина команды: 6 байт.

1-й байт(код операции):

1000 0001b=81h –AND (r/m <- r/m&data), поле w=1, т.е. операнд 16-ми разрядный.

2-й байт(постбайт):

1000 0111b=87h, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0c69dh);

000 – reg

111 – reg/mem, mod=10: левый операнд – BX+disp

3-й байт(dispLow):

D8

4-й байт(dispHigh):

78

5-й байт(dataLow):

E4

6-й байт(dataHigh):

F8

Мнемоника команды: AND [word BX+078D8h], 0F8E4h

Адрессация операндов:

левый – базовая, где BX – база, 078D8h – смещение

правый – непосредственная, 0F8E4h – непосредственное значение

Комментарий к команде: M(DS:DI+078D8h) <- M(DS:DI+078D8h)& 0F8E4h

Размещение команды в памяти:

|

Время выполнения Время выполнения в тактах: nТ=(n+Tиа)=8+Tиа, где Tиа – время вычисления эффективного адреса: EA=DI+disp16. По таблице 11 находим, что Tиа=9, тогда nТ=8+9=17 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=17*10-8=0,17 мкс, где tТ=1/fТ=1/100000000=10-8.

|

================ №3 Навести команду мікропроцесора x86… ===============

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки необхідно інвертувати біти №1, 4, 6, 8 то маска буде мати вигляд 101010010. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL,01010101:

X X X X X X X X X

1 0 1 0 1 0 0 1 0

X X X X X

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, парні біти якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 48 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 30-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 48*4 = 192D = 0011000000В. Таким чином повна 20-и розрядна фізична адреса обробника 30-ого переривання має вигляд: 00000000000011000000 В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -45 буде віднято 34, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -45-34 можна замінити операцією -45+(-34). Для цього треба представити число -34 в додатковому коді: записуємо модуль цього числа в двійковій формі: 34D= 00100010B; інвертуємо отриманий результат: 11011101В; додаємо до отриманої комбінації одиницю:

11011101

1

11011110

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11011110В = 1+32=33. До отриманого результату додаємо одиницю і отримуємо 34, а оскільки знаковий розряд = 1, то маємо -34. Переведення в додатковий код виконано вірно. Таким же чином переведемо -45 в додатковий код: 45D = 00101101B; інвертуємо: 11010010В; додаємо одиницю: 11010011B. Робимо перевірку: 11010011B = 4+8+32=44. До отриманого результату додаємо одиницю і отримуємо 45, а оскільки знаковий розряд = 1, то маємо -45. Виконуємо операцію додавання над числами в додатковому коді:

11011110

11010011

110110001

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10110001

11111111

1 10110000

Переведемо отриманий результат з додаткового коду в десяткову форму:

110110000В = 1+2+4+8+64+1=90D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -90.

8. add [bx + di + 0679ah], 0b138h | 81 AC F5 F3 5D C9

========== №1 Ассемблирование – add [bx + di + 0679ah], 0b138h ===========

Коментар до команди: М(DS:bx + DS:di + 0679ah) ← 0b13h

1-й байт(код операции):

из табл. комманд, № 3 находим КОП 10000001b=81h.

2-й байт(постбайт):

md=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0679ah);

000 – reg: поле reg содержит расширение КОП (1-й байт);

r/m =001, т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: ЕА=BX+DI+disp

Получаем второй байт:10000001=81h

3-й байт(dispLow):

9ah

4-й байт(dispHigh):

67h

5-й байт(dataLow):

38h

6-й байт(dataHigh):

b1h

Машинный код команды: 81 81 9a 67 38 b1

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базово-индексная со смещением, где BX – база, DI-индекс, 0679ah – смещение относительно базы.

Правый операнд – непосредственная, 0b138h – непосредственный 16-и битный операнд.

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)=4+Tиа, где Tиа – время вычисления эффективного адреса: EA=BX+di +0679ah. По таблице 11 находим, что для базово-индексной адресации Tиа=8, тогда nТ=4+8=12 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=12*10-7=1.2 мкс, где tТ=1/fТ=1/10000000=10-7.

|

=============== №2 Дизассемблирование – (81 AC F5 F3 5D C9) ==============

Длина команды: 6 байт.

1-й байт(код операции):

10000001b=81h, то AND(r/m <- r/m&data), поле w=1, т.е. операнд 16-ми разрядный.

2-й байт(постбайт):

10101100b=ACh, то:

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0c69dh);

101-reg

100- reg/mem, то левый операнд – SI+disp, sub(r/m <- r/m - data)

3-й байт(dispLow):

F5h

4-й байт(dispHigh):

F3h

5-й байт(dataLow):

5Dh

6-й байт(dataHigh):

C9h

Мнемоника команды:

SUB [word SI+ 0F3F5h],0C95Dh

левый – индексная, где SI – база, 0F3F5h – смещение

правый – непосредственная, 0C95Dh – непосредственное значение

Комментарий к команде:

M(DS:SI+0F3F5h) <- M(DS:SI+0F3F5h) - 0C95Dh

Размещение команды в памяти:

|

Время выполнения Время выполнения в тактах: nТ=(n+Tиа)=4+Tиа, где Tиа – время вычисления эффективного адреса: EA=SI+disp16. По таблице 11 находим, что Tиа=9, тогда nТ=4+9=13 тактов.

|

================ №3 Навести команду мікропроцесора x86… ===============

xor al, 01101100

X X X X X X X X

0 1 1 0 1 1 0 0

X X X X

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, №2, 3, 5, 6 біти якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 53 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 53-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 53*4 = 212D = 0011010100В. Таким чином повна 20-и розрядна фізична адреса обробника 30-ого переривання має вигляд: 00000000000011010100В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -50 буде віднято 32, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -50-32 можна замінити операцією -50+(-32). Для цього треба представити число -32 в додатковому коді: записуємо модуль цього числа в двійковій формі: 32D= 00100000B; інвертуємо отриманий результат: 11011111В; додаємо до отриманої комбінації одиницю:

11011111

1

11100000

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11100000В = 1+2+4+8+16=31. До отриманого результату додаємо одиницю і отримуємо 32, а оскільки знаковий розряд = 1, то маємо -32. Переведення в додатковий код виконано вірно. Таким же чином переведемо -50 в додатковий код: 50D = 00110010B; інвертуємо: 11001101В; додаємо одиницю: 11001110B. Робимо перевірку: 11001110B = 1+16+32=49. До отриманого результату додаємо одиницю і отримуємо 50, а оскільки знаковий розряд = 1, то маємо -50. Виконуємо операцію додавання над числами в додатковому коді:

11100000

11001110

1 10101110

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10101110

11111111

1 10101101

Переведемо отриманий результат з додаткового коду в десяткову форму: 110101101В = 2+16+64=82D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -82.

test [bx + si + 0f26ch], 00000h | C7 85 AE C1 CB C8

============ №1 Ассемблирование – test [bx + si + 0f26ch], 00000h ===========

1-й байт(код операции):

из табл. комманд, № 15 находим КОП 11110111b=F7h, w=1, т. к. длина операнда 16 бит.

2-й байт(постбайт): md000 r/m

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0f26ch);

000 – reg: поле reg содержит расширение КОП (1-й байт);

000 – reg/mem: поле reg/mem задает способ вычисления эффективного адреса второго операнда(источника) в сегменте данных EA=(BX)+(SI)+disp16.

Получаем второй байт: 10000000=80h.

3-й байт(dispLow):

6Ch

4-й байт(dispHigh):

F2h

5-й байт(dataLow):

00h

6-й байт(dataHigh):

00h

Машинный код команды: F7 80 6C F2 00 00

Длина команды: 6 байт.

Способы адресации операндов:

Левый операнд – базово-индексная со смещением

Правый операнд – непосредственная

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)=10+Tиа, где Tиа – время вычисления эффективного адреса По таблице 11 находим, что для базово-индексной со смещением адресации Tиа=11, тогда nТ=10+11=21 такт. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=21*10-8=0,21 мкс, где tТ=1/fТ=1/100000000=10-8.

|

============== №2 Дизассемблирование – (C7 85 AE C1 CB C8) ==============

Длина команды: 6 байт.

1-й байт(код операции):

1100 0111b= C7h MOV(r/m data) поле w=1, т.е. операнд 16-ми разрядный.

2-й байт(постбайт):

1000 0101b=85h, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение;

000 – reg

101 – reg/mem, mod=10: левый операнд – (DI) + disp16

3-й байт(dispLow):

AE

4-й байт(dispHigh):

C1

5-й байт(dataLow):

CB

6-й байт(dataHigh):

C8

Мнемоника команды: MOV [DI+0C1AEh], 0C8CBh

Адресация операндов:

Левый операнд – базовая, где DI – база, 0C1AEh – смещение

Правый операнд – непосредственная, 0C8CBh – непосредственное значение

Размещение команды в памяти:

|

Время выполнения: Время выполнения в тактах: nТ=(n+Tиа)=8+Tиа, где Tиа – время вычисления эффективного адреса: EA=DI+disp16. По таблице 11 находим, что Tиа=9, тогда nТ=8+9=17 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=17*10-8=0,17 мкс, где tТ=1/fТ=1/100000000=10-8. |

================ №3 Навести команду мікропроцесора x86… ===============

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки необхідно інвертувати біти молодшої тетради ( тобто 0-й,1-й,3-й,4-й) то маска буде мати вигляд 00001111. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL, 00001111:

X X X X X X X X

0 0 0 0 1 1 1 1

X Х Х Х

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, біти молодшої тетради якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 57 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 30-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 57*4 = 228D = 11100100В. Таким чином повна 20-и розрядна фізична адреса обробника 30-ого переривання має вигляд: 00000000000011100100В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -55 буде віднято 30, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -55-30 можна замінити операцією -55+(-30). Для цього треба представити число -30 в додатковому коді: записуємо модуль цього числа в двійковій формі: 30D= 00011110B; інвертуємо отриманий результат: 11100001В; додаємо до отриманої комбінації одиницю:

11100001

1

11100010

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто

11100010В = 1 + 4 + 8 + 16 = 29. До отриманого результату додаємо одиницю і отримуємо 30, а оскільки знаковий розряд = 1, то маємо -30. Переведення в додатковий код виконано вірно. Таким же чином переведемо -55 в додатковий код: 55D = 00110111B; інвертуємо: 11001000В; додаємо одиницю: 11001001B. Робимо перевірку: 11001001B = 2+4+16+32=54. До отриманого результату додаємо одиницю і отримуємо 55, а оскільки знаковий розряд = 1, то маємо -55. Виконуємо операцію додавання над числами в додатковому коді:

11100010

11001001

1 10101011

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10101011

11111111

1 10101010

Переведемо отриманий результат з додаткового коду в десяткову форму:

110101010В = (1 + 4 + 16 + 64) + 1 = 86D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -86.

cmp [di + 04f8ah], 0dd1fh | 81 98 DB B8 9C FD

============== №1 Ассемблирование – cmp [di + 04f8ah], 0dd1fh =============

Коментарий к команде: M(DS: di + 04f8ah) == 0dd1fh ???

1-й байт(код операции):

из табл. 2.2.5.3 (Арифметические команды), № 26 (CMP; r/m – data) находим КОП 100000sw. s=0, w=1. 10000001b = 81h.

2-й байт(постбайт):

md111 r/m.

при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=04f8ah), то mod(md) = 10.

Т.к. EA=(di)+disp, то r/m=101.

Получаем второй байт: 10111101b=BDh

3-й байт(младший байт данных):

1Fh.

4-й байт(старший байт данных):

DDh.

5-й байт(младший байт смещения disp16):

8Ah.

6-й байт(старший байт смещения disp16):

4Fh.

Машинный код команды: 83 BD 1F DD 8A 4F

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – идексная со смещением 04f8ah

Правый операнд – непосредственная.

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)=17+Tиа По таблице 2.2.6.2 Tиа=9, тогда nТ=17+9=26 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ =nТ*tТ=26*10-8=0,26 мкс, где tТ=1/fТ=1/100000000=10-8.

|

=============== №2 Дизассемблирование – (81 98 DB B8 9C FD) ==============

Длина команды: 6 байт.

1-й байт(код операции):

1000 0001b=81h – SBB (r/m ← r/m-data-CF), поле w=1, т.е. операнд 16-и разрядный.

2-й байт(постбайт):

1001 1000b=98h, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0B8DBh);

011 – reg

000 – reg/mem: левый операнд - (BX)+(SI)+disp16

3-й байт(dataLow):

B8

4-й байт(dataHigh)

DB

5-й байт(dispLow):

FDh

6-й байт(dispHigh):

9Ch

Мнемоника команды: SBB [BX+SI+0B8DBh], FD9C

Комментарий к команде: M(DS: BX+SI+0B8DBh) ← M(DS: BX+SI+0B8DBh)-FD9C-CF

Способы адресации операндов: 1) Базово – индексная со смещением 2) Непосредственная.

Размещение команды в памяти:

|

Время выполнения команды: Время выполнения в тактах: nТ =(n+Tиа)=17+Tиа Tиа=11, тогда nТ =17+11=28 тактов. Время выполнения команды в секундах: Tk =(n+Tиа)*tТ =nТ*tТ=28*10-8=0,28 мкс, где tТ = 1/fТ=1/100000000=10-8.

|

================ №3 Навести команду мікропроцесора x86… ===============

Для інвертування бітів двійкового числа використовується операція складання за модулем 2. В мові асемблера їй відповідає команда XOR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки необхідно інвертувати біти старшої тетради( тобто 7-й,6-й,5-й,4-й) то маска буде мати вигляд 11110000. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду XOR AL, 11110000:

X X X X X X X X

1 1 1 1 0 0 0 0

X X X X

Як бачимо в наслідок виконання команди в регістр AL буде поміщена комбінація, біти старшої тетради якої інвертовані відносно вихідної комбінації.

================ №4 Сформувати … номер переривання 60 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 60-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 60*4 = 240D = 0011110000В. Таким чином повна 20-и розрядна фізична адреса обробника 60-ого переривання має вигляд: 00000000000011110000В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -60 буде віднято 28, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -60-28 можна замінити операцією -60+(-28). Для цього треба представити число -28 в додатковому коді: записуємо модуль цього числа в двійковій формі: 28D= 00011100B; інвертуємо отриманий результат: 11100011В; додаємо до отриманої комбінації одиницю: 11100100В. Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто

11100100В = 1 + 2+ 8 + 16 = 27. До отриманого результату додаємо одиницю і отримуємо 28, а оскільки знаковий розряд = 1, то маємо -28. Переведення в додатковий код виконано вірно. Таким же чином переведемо -60 в додатковий код: 60D = 00111100B; інвертуємо: 11000011В; додаємо одиницю: 11000100B. Робимо перевірку: 11000100B = 1+2+8+16+32=59. До отриманого результату додаємо одиницю і отримуємо 60, а оскільки знаковий розряд = 1, то маємо -60. Виконуємо операцію додавання над числами в додатковому коді:

11100100

11000100

110101000

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10101000

11111111

110100111

Переведемо отриманий результат з додаткового коду в десяткову форму:

110100111В = (8 + 16 + 64) + 1 = 89D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -89.

add [bx + si + 0f45ch], 0db7ah | 81 85 BD B4 7F D3

============= №1 Ассемблирование – add [bx + si + 0f45ch], 0db7ah ============

Задание: add [bx + si + 0f45ch], 0db7ah

Комментарий к команде: M(DS: bx + si + 0f45ch)←M(DS: bx + si + 0f45ch) +0db7ah

1-й байт(код операции):

из табл. комманд, № 7 находим КОП 10000001b=81h, w=1, s=0 т. к. длина операнда 16 бит.

2-й байт(постбайт):

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0f45ch);

000 – reg: поле reg содержит расширение КОП (1-й байт);

000 – reg/mem: поле reg/mem =000, т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: (BX)+(SI)+disp16.

Получаем второй байт: 10000000=80h.

3-й байт(dispLow):

5ch.

4-й байт(dispHigh):

f4h

5-й байт(dataLow):

7ah

6-й байт(dataHigh):

dbh

Машинный код команды: 81 80 5C F4 7A DB

Длина команды: 6 байта.

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)= 4/17+TИА, где Tиа – время вычисления эффективного адреса: EA= BX + SI + 0f45ch. По таблице 11 находим, что для базовой адресации Tиа=11, тогда nТ=4/17+11=191/17 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=191/17 *10-7=1,1 мкс, где tТ=1/fТ=1/10000000=10-7.

|

=============== №2 Дизассемблирование – (81 85 BD B4 7F D3) ==============

Задание: 81 85 BD B4 7F D3

Длина команды: 6 байт.

1-й байт(код операции):

1000 0001b=81h – ADD (r/m←r/m+data), поле w=1, т.е. операнд 16-ми разрядный.

2-й байт(постбайт):

10000101 b =85h, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0bc9ah);

000 – reg

101 – reg/mem, mod=10: левый операнд – (DI)+disp16

3-й байт(dispLow):

BD

4-й байт(dispHigh):

B4

5-й байт(dataLow):

7F

6-й байт(dataHigh):

D3

Мнемоника команды: ADD [DI+0B4BDh], 0D37Fh

Адрессация операндов:

левый – индексная, DI – индекс смещения, 0B4BDh – смещение

правый – непосредственная, 0D37Fh – непосредственное значение

Комментарий к команде: M(ES: DI+0B4BDh) <- M(ES: DI+0B4BDh) + 0D37Fh

Размещение команды в памяти:

|

Время выполнения Время выполнения в тактах: nТ=(n+Tиа)= 17+ТИА, где Tиа – время вычисления эффективного адреса: EA=(DI)+disp16. По таблице 11 находим, что Tиа=9, тогда nТ=17+9=26 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=26*10-7=2,6 мкс, где tТ=1/fТ=1/10000000=10-7.

|

================ №3 Навести команду мікропроцесора x86… ===============

Для встановлення певних біт в «1» використаємо команду OR (логічне додавання). Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для інвертування. Оскільки потрібно встановити непарні біти (1-й, 3-й, 5-й, 7-й) в «1», то маска буде мати вигляд 10101010.

Команда: OR AL, 10101010

Нехай в регістрі AL записана наступна комбінація: XXXXXXXX.

Виконаємо команду OR AL, 10101010

X X X X X X X X

1 0 1 0 1 0 1 0

1 X 1 X 1 X 1 X

Як бачимо, в наслідок виконання команди в регістр AL буде поміщена комбінація, непарні біти якої встановлені в «1».

================ №4 Сформувати … номер переривання 65 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду, то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 65-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 65*4 = 260D = 0100000100В. Таким чином повна 20-и розрядна фізична адреса обробника 65-ого переривання має вигляд: 00000000000100000100В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -70 буде віднято 24, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -70-24 можна замінити операцією -70+(-24). Для цього треба представити число -24 в додатковому коді: записуємо модуль цього числа в двійковій формі: 24D= 00011000B; інвертуємо отриманий результат: 11100111В; додаємо до отриманої комбінації одиницю:

11100111

1

1 1101000

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11101000В = 1+2+4+16=23. До отриманого результату додаємо одиницю і отримуємо 24, а оскільки знаковий розряд = 1, то маємо -24. Переведення в додатковий код виконано вірно. Таким же чином переведемо -70 в додатковий код: 70D = 01000110B; інвертуємо: 10111001В; додаємо одиницю: 10111010B. Робимо перевірку: 10111010B = 1+4+64=69. До отриманого результату додаємо одиницю і отримуємо 70, а оскільки знаковий розряд = 1, то маємо -70. Виконуємо операцію додавання над числами в додатковому коді:

11101000

10111010

1 10100010

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10100010

00000001

10100001

Переведемо отриманий результат з додаткового коду в десяткову форму: 10100001В = (2+4+8+16+64)+1=95D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -95.

sub [bx + di + 0d2c3h], 0f27dh | 81 AF 7C BC 8D D7

======== №1 Ассемблирование – sub [bx + di + 0d2c3h], 0f27dh =============

Задание: sub [bx + di + 0d2c3h], 0f27dh;

Комментарий к команде: M(DS: bx + di + 0d2c3h)←M(DS: bx + di + 0d2c3h) - 0f27dh

1-й байт(код операции):

из табл. комманд, № 7 находим КОП 10000001b=81h, w=1, s=0 т. к. длина операнда 16 бит.

2-й байт(постбайт):

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0d2c3h);

101 – reg: поле reg содержит расширение КОП (1-й байт);

001 – reg/mem: поле reg/mem =001, т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: (BX)+(DI)+disp16.

Получаем второй байт: 10101001=a9h.

3-й байт(dispLow):

C3h.

4-й байт(dispHigh):

D2h

5-й байт(dataLow):

7dh

6-й байт(dataHigh):

F2h

Машинный код команды: 81 A9 C3 D2 7D F2

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базово-индексная, где BX – база, DI – индексное смещение, 0d2c3h – смещение относительно базы.

Правый операнд – непосредственная, 0f27dh – непосредственный 16-и битный операнд.

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)= 4/17+TИА, где Tиа – время вычисления эффективного адреса: EA= BX + DI + 0d2c3h. По таблице 11 находим, что для базовой адресации Tиа=12, тогда nТ=4/17+12=208/17 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=208/17*10-7=1,6 мкс, где tТ=1/fТ=1/10000000=10-7.

|

=============== №2 Дизассемблирование – (81 AF 7C BC 8D D7) =============

Задание: 81 AF 7C BC 8D D7

Длина команды: 6 байт.

1-й байт(код операции):

1000 0001b=81h –sub(r/m <- r/m-data) поле w=1, т.е. операнд 16-ми разрядный.

2-й байт(постбайт):

10101111 b=afh, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0bc7ch);

101 – reg

111 – reg/mem, mod=10: левый операнд – (BX)+disp16

3-й байт(dispLow):

7c

4-й байт(dispHigh):

BC

5-й байт(dataLow):

8d

6-й байт(dataHigh):

D7

Мнемоника команды: SUB [BX+0bc7ch], 0d78dh

Адрессация операндов:

левый – базова, где BX-база, 0BC7ch – смещение

правый – непосредственная, 0d78dh – непосредственное значение

Комментарий к команде: M(CS: BX+0BC7ch) <- M(CS: BX+0BC7ch)-0d78dh

Размещение команды в памяти:

|

Время выполнения Время выполнения в тактах: nТ=(n+Tиа)= 4/17+ТИА, где Tиа – время вычисления эффективного адреса: EA=(BX)+disp16. По таблице 11 находим, что Tиа=9, тогда nТ=4/17+9=157 /17 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=157/17*10-7=0.9 мкс, где tТ=1/fТ=1/10000000=10-7.

|

================ №3 Навести команду мікропроцесора x86… ===============

Для зміни 1,3,5 одиницю ми будемо використовувати операцію OR(логічне додавання). Оскільки необхідно встановити в одиницю біти №1,3,5 то маска буде мати вигляд 00101010

Команда: OR AL, 00101010

Перевірка:

1 1 0 0 1 0 1 0

0 0 1 0 1 0 1 0

1 1 1 0 1 0 1 0

================ №4 Сформувати … номер переривання 67 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 67-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 67*4 = 268D = 0100001100В. Таким чином повна 20-и розрядна фізична адреса обробника 30-ого переривання має вигляд: 00000000000100001100В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -75 буде віднято 22, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -75-22 можна замінити операцією -75+(-22). Для цього треба представити число -22 в додатковому коді: записуємо модуль цього числа в двійковій формі: 22D= 00010110B; інвертуємо отриманий результат: 11101001В; додаємо до отриманої комбінації одиницю:

11101001

1

11101010

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 11101010В = 1+4+16=21. До отриманого результату додаємо одиницю і отримуємо 22, а оскільки знаковий розряд = 1, то маємо -22. Переведення в додатковий код виконано вірно. Таким же чином переведемо -75 в додатковий код: 75D = 01001011B; інвертуємо: 10110100В; додаємо одиницю: 10110101B. Робимо перевірку: 10110101B = 2+8+64=74. До отриманого результату додаємо одиницю і отримуємо 75, а оскільки знаковий розряд = 1, то маємо -75. Виконуємо операцію додавання над числами в додатковому коді:

11101010

10110101

1 10011111

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10011111

00000001 (не правильно!!!)

1 10011110

Переведемо отриманий результат з додаткового коду в десяткову форму: 110011110В = 1+32+64=97D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -97.

mov [bp+ si + 0c95dh], 0d784h | 81 84 6F D6 5E F1

============ №1 Ассемблирование – mov [bp+ si + 0c95dh], 0d784h ==========

Комментарий к команде: M(DS*16+ bp+ si + 0c95dh) &0d784h

1-й байт(код операции):

из табл. комманд, находим КОП 11000111 =C7h, w=1, т. к. длина операнда 16 бит.

2-й байт(постбайт): 10000010

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0c95dh);

010 – reg/mem: т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: ЕА=BP+SI+disp= BP + SI + 0c95dh.

Получаем второй байт: 10000010=82h.

3-й байт(dispLow):

5Dh

4-й байт(dispHigh):

C9h

5-й байт(dataLow):

84h

6-й байт(dataHigh):

D7h

Машинный код команды: C7 82 5D C9 84 D7

Длина команды: 6 байта.

Способы адресации операндов:

Левый операнд – базово-индексная со смещением

Правый операнд – непосредственная.

Размещение команды в памяти:

|

Время выполнения команды Время выполнения в тактах: nТ=(n+Tиа)=10+12, где Tиа – время вычисления эффективного адреса: BP + SI + 0c95dh. По таблице находим, что для базовой адресации Tиа=12, тогда nТ=10+12=22 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=22*10-7=2.2 мкс, где tТ=1/fТ=1/100000000=10-7.

|

=============== №2 Дизассемблирование – (81 84 6F D6 5E F1) ===============

Задание: 81 84 6F D6 5E F1

Длина команды: 6 байт.

1-й байт(код операции):

11000001=81h –ADD (r/mr/m+data), поле w=1, т.е. операнд 16-ми разрядный.

2-й байт(постбайт):

10000100b=84h, где

10 – mod: при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0c69dh);

000

100 – reg/mem, mod=10: левый операнд –SI+disp

3-й байт(dispLow):

6F

4-й байт(dispHigh):

D8

5-й байт(dataLow):

5E

6-й байт(dataHigh):

F1

Мнемоника команды: ADD [SI+D86Fh], F15Eh

Адрессация операндов:

левый –индексная со смещением

правый – непосредственная.

Комментарий к команде: M(DS*16 + SI+D86Fh) <- F15Eh

Размещение команды в памяти:

|

Время выполнения Время выполнения в тактах: nТ=(n+Tиа)=17+Tиа, где Tиа – время вычисления эффективного адреса: EA= SI+disp16. По таблице находим, что Tиа=9, тогда nТ=17+9=26 тактов. Время выполнения команды в секундах: Tk=(n+Tиа)*tТ=nТ*tТ=26*10-7=2.6 мкс, где tТ=1/fТ=1/100000000=10-7.

|

================ №3 Навести команду мікропроцесора x86… ===============

Для встановлення бітів двійкового числа в «1» використовується операція «АБО». В мові асемблера їй відповідає команда OR. Першим операндом команди буде 8-и бітний регістр AL, другим – безпосереднє число, маска для встановлення. Оскільки необхідно встановити в «1» біти, то маска буде мати вигляд 00101010. Нехай в регістрі AL записана наступна комбінація: ХХХХХХХХ. Виконаємо команду OR AL,11001100:

X X X X X X X X

0 1 0 1 0 1 0 0

X 1 X 1 X 1 X X

================ №4 Сформувати … номер переривання 69 ================

Мікропроцесор іх86 має векторну (адресну) систему переривань із зовнішніми і внутрішніми джерелами запитів. Кожне джерело має свій “тип” – номер “входу” у таблицю векторів (адрес) оброблювачів переривань, за яким МП знаходить відповідну підпрограму обслуговування переривання. Таблиця векторів має 256 входів з номерами від 0D до 255 D і займає перші 1024 байти пам'яті – по чотири байти на кожен тип запиту (256х4 = 1024). Оскільки таблиця переривань знаходиться починаючи з нульових адрес в сегменті коду то старші 10 розрядів фізичної адреси представляють собою нулі. Молодші 10 розрядів фізичної адреси входу в таблицю переривань визначаються зсувом на 2 розряди вліво(множення на 4) номеру переривання. Так для 69-ого переривання молодші 10 розрядів фізичної адреси знаходимо як 69*4 = 276D = 00100010100 В. Таким чином повна 20-и розрядна фізична адреса обробника 69-ого переривання має вигляд: 000000000000100010100В.

============= №5 Виконати функцію … команди SBB AL, data8… ============

Команда SBB виконує віднімання значення правого операнда від лівого з урахуванням позики(прапорця СF) і результат поміщає в лівий операнд. В даному випадку від -80 буде віднято 20, а потім віднято 1. Результат буде записаний в регістр AL. Операцію -80-20 можна замінити операцією -80+(-20). Для цього треба представити число -80 в додатковому коді: записуємо модуль цього числа в двійковій формі: 80D= 01010000B; інвертуємо отриманий результат: 10101111В; додаємо до отриманої комбінації одиницю:

10101111

1

1 0110000

Зробимо перевірку: в додатковому коді значущими розрядами є нульові тобто 10110000В = 1+2+4+8+64=79. До отриманого результату додаємо одиницю і отримуємо 80, а оскільки знаковий розряд = 1, то маємо -80. Переведення в додатковий код виконано вірно. Таким же чином переведемо -20 в додатковий код: 20D = 00010100B; інвертуємо: 11101011В; додаємо одиницю: 11101100B. Робимо перевірку: 11101100B = 1+2+16=19. До отриманого результату додаємо одиницю і отримуємо 20, а оскільки знаковий розряд = 1, то маємо -20. Виконуємо операцію додавання над числами в додатковому коді:

10110000

11101100

110011100

Врахуємо СF: виконаємо віднімання СF від отриманого результату:

10011100

11111111

110011011

Переведемо отриманий результат з додаткового коду в десяткову форму: 110011011В = 4+32+64+1=101D. Оскільки знаковий біт встановлений в 1, то отриманий результат від’ємний, тобто -101.

xor [bx + 0b9dfh], 016cbh | C7 83 5D DD FD F6

============ №1 Ассемблирование – A xor [bx + 0b9dfh], 016cbh ==============

Комментарий к команде: M(DS:BX+0b9dfh) ←016cbh

1-й байт(код операции):

из табл. команд находим КОП 10000001=81h, w=1, т. к. длина операнда 16 бит.

2-й байт(постбайт):

10 – mod: поле mod=10, т.к. при вычислении эффективного адреса в команде используется 16-ти разрядное смещение(disp16=0b9dfh);

110 – reg: поле reg содержит расширение КОП (1-й байт);

111 – reg/mem: поле reg/mem =111, т.к. способ вычисления адреса левого(первого) операнда в сегменте данных: ЕА=BX+disp= BX+0b9dfh.

Получаем второй байт: 10110111=B7h.

3-й байт(dispLow):

df

4-й байт(dispHigh):

b9

5-й байт(dataLow):

cb

6-й байт(dataHigh):

16

Машинный код команды: 81 B7 DF B9 CB 16