Лабораторная работа №7

Моделирование комбинационных схем.

Цель занятия

Ознакомиться с возможностями программы Microcap.

Научиться моделировать комбинационные логические схемы.

Постановка задачи

Построить модель комбинационной схемы согласно приведенному заданию.

Содержание отчета

Постановка задачи для конкретного варианта.

Временные характеристики заданной модели.

Теоретические сведения

Комбинационными называются такие логические устройства, выходные сигналы которых однозначно определяются входными сигналами.

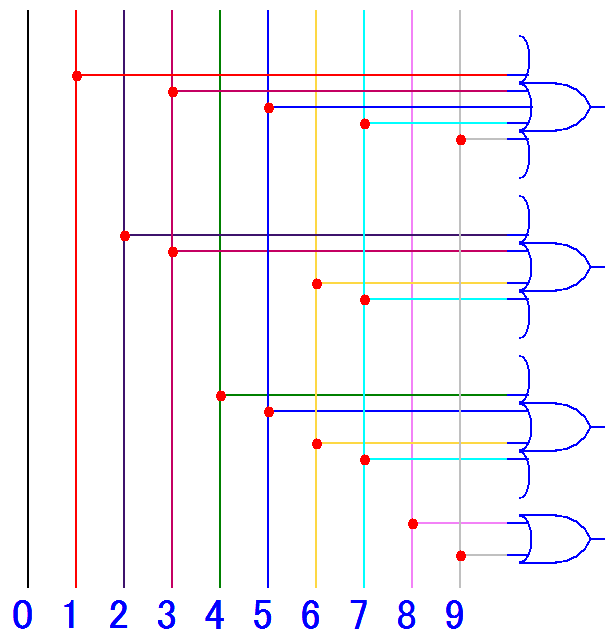

Шифратор (кодер) – (англ. encoder) логическое устройство, выполняющее операцию преобразования позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код.

Двоичный шифратор выполняет логическую функцию преобразования унитарного n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением:

где

n – число входов,

m – число выходных двоичных разрядов.

Рисунок 1 Реализация шифратора на элементах "ИЛИ"

Дешифратор

Это комбинационные схемы с несколькими входами и выходами, преобразующие код, подаваемый на входы в сигнал на одном из выходов. На одном выходе дешифратора появляется логическая единица, а на остальных – логические нули, когда на входных шинах устанавливается двоичный код определённого числа или символа, то есть дешифратор расшифровывает число в двоичном, троичном или k-ичном коде, представляя его логической единицей на определённом выходе. Число входов дешифратора равно количеству разрядов поступающих двоичных, троичных или k-ичных чисел. Число выходов равно полному количеству различных двоичных, троичных или k-ичных чисел этой разрядности.

Рисунок 2 Дешифратор 2 в 4

Таблица 1 Таблица истинности дешифратора

A |

B |

D0 |

D1 |

D2 |

D3 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

мультиплексор.

Мультиплексор представляет собой схемный элемент, который подключает один из цифровых входов к одному выходу. Вход выбирается из группы посредством селективных (адресных) входов.

В качестве примера представлен 4-разрядный мультиплексор (рис. 1).

Рисунок 3 4-входовый мультиплексор

Мультиплексор имеет в своем составе:

4 информационных входа (IN1…IN4);

2 адресных входа (X1, X2);

Каждый информационный вход мультиплексора соединен через элемент AND (I1…I4) с адресными входами X1 и X2. Сигнал с адресных входов снимается до и после инвертора. Работа мультиплексора описывается следующим образом:

Чтобы выбрать вход IN1, на адресные входы X1 и X2 необходимо подать комбинацию 00. Вход IN1 соединен с сигналами ⌐X1, ⌐X2(X1 и X2 после инвертора). Таким образом, на вход I1 придет сигнал IN1 и две логические единицы с X1 и X2. На вход элемента OR с I1 придет сигнал IN1, а с I2…I4 придут логические нули. На выходе элемента OR будет только сигнал IN1.

Чтобы выбрать вход IN2, на адресные входы X1 и X2 необходимо подать комбинацию 01. Вход IN2 соединен с сигналами ⌐X1, X2. Таким образом, на вход I2 придет сигнал IN2 и две логические единицы с X1 и X2. На вход элемента OR с I2 придет сигнал IN2, а с I1, I3, I4 придут логические нули. На выходе элемента OR будет только сигнал IN2.

Чтобы выбрать вход IN3, на адресные входы X1 и X2 необходимо подать комбинацию 10. Вход IN3 соединен с сигналами X1, ⌐X2. Таким образом, на вход I3 придет сигнал IN3 и две логические единицы с X1 и X2. На вход элемента OR с I3 придет сигнал IN3, а с I1, I2, I4 придут логические нули. На выходе элемента OR будет только сигнал IN3.

Чтобы выбрать вход IN4, на адресные входы X1 и X2 необходимо подать комбинацию 11. Вход IN4 соединен с сигналами X1,X2. Таким образом, на вход I4 придет сигнал IN4 и две логические единицы с X1 и X2. На вход элемента OR с I4 придет сигнал IN4, а с I1, I2, I3 придут логические нули. На выходе элемента OR будет только сигнал IN4.