4. Описание схемы сопряжения с интерфейсом на языке vhdl Компонент – селектор адреса

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity Selector is

port (

BaseAddr: in std_logic_vector (7 downto 0);

SA : in std_logic_vector (15 downto 0);

AEN : in std_logic;

CS : out std_logic_vector (1 downto 0)

);

end Selector ;

architecture Behave_selector of Selector is

signal Selector_active : std_logic;

begin

Selector_active <= '1' when (SA(15 downto 8) = BaseAddr(7 downto 0) and

AEN = '1' and

SA(7 downto 1)="0000000")

else '0';

Process (SA, Selector_active)

variable decode : integer range 1 downto 0;

begin

CS <= "00";

if selector_active = '1' then

decode := conv_integer(SA(0));

for i in 1 downto 0 loop

if i = decode then

CS(i) <= '1';

else

CS(i) <= '0';

end if;

end loop;

end if;

end process;

end Behave_selector;

Компонент - таймер

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity Timer is

port(

Freq_Mode : in integer range 0 to 65535;

AEN : in std_logic;

Reload : in std_logic;

Sysclk : in std_logic;

Timer_Clk : out std_logic

);

end Timer;

architecture Timer_Struct of Timer is

begin

process(Reload,Sysclk,Freq_mode)

variable i : integer range 0 to 65535;

variable clk : std_logic;

begin

if (Reload='1') then

i := Freq_Mode;

clk := '0';

elsif (Sysclk = '1' and Sysclk'event) then

if (i = 1) then

clk := not(clk);

Timer_Clk <= clk and AEN;

i := Freq_Mode;

else

Timer_Clk <= '0';

i := i-1;

end if;

end if;

end process;

end Timer_Struct;

Основное устройство

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity cpld is

port(

BaseAddr : in std_logic_vector (7 downto 0);

SA : in std_logic_vector (15 downto 0);

AEN : in std_logic;

Data_In : in std_logic_vector (15 downto 0);

Data_Out : out std_logic_vector (15 downto 0);

IOR : in std_logic;

IOW : in std_logic;

Rst : in std_logic;

Sysclk : in std_logic;

ADC_Start : out std_logic;

Out_Start : in std_logic;

Interrupt : out std_logic;

Fifo_Full1 : in std_logic;

Fifo_Full2 : in std_logic;

Fifo_Reset : out std_logic;

Fifo_Empty1 : in std_logic;

Fifo_Empty2 : in std_logic;

Fifo_In1 : in std_logic_vector (7 downto 0);

Fifo_In2 : in std_logic_vector (7 downto 0);

Fifo_Read : out std_logic;

Fifo_Write : out std_logic

);

end cpld;

architecture cpld_struct of cpld is

signal cs_signal : std_logic_vector (1 downto 0);

-------------------------------------------------------Ragister I/O Signals Declaration

signal csr_timer_mode : std_logic_vector (7 downto 0);

signal csr_out_start_en : std_logic;

signal csr_over_int_en : std_logic;

signal csr_over_flag : std_logic;

signal csr_data_ready : std_logic;

signal csr_ready_int_en : std_logic;

-------------------------------------------------------End

-------------------------------------------------------Register Control Signals Declaration

signal DR_RD : std_logic;

signal CSR_WR : std_logic;

signal CSR_RD : std_logic;

-------------------------------------------------------End

-------------------------------------------------------Component Declaration

component Selector

port(

BaseAddr : in std_logic_vector (7 downto 0);

SA : in std_logic_vector (15 downto 0);

AEN : in std_logic ;

CS : out std_logic_vector (1 downto 0)

);

end component;

component Timer

port(

Freq_Mode : in integer range 0 to 65535;

AEN : in std_logic;

Reload : in std_logic;

Sysclk : in std_logic;

Timer_Clk : out std_logic

);

end component;

-------------------------------------------------------End

begin

-------------------------------------------------------Ports Mapping

In_Selector : Selector

port map(

BaseAddr => BaseAddr,

SA => SA,

AEN => AEN,

CS => cs_signal

);

In_Timer : Timer

port map(

Freq_Mode => conv_integer(csr_timer_mode),

AEN => AEN,

Reload => Rst,

Sysclk => Sysclk,

Timer_Clk => ADC_Start

);

-------------------------------------------------------End

-------------------------------------------------------Register Control Signal Description

DR_RD <= '1' when ((cs_signal(1) = '1') and (IOR = '0')) else '0';

CSR_WR <= '1' when ((cs_signal(0) = '1') and (IOW = '0')) else '0';

CSR_RD <= '1' when ((cs_signal(0) = '1') and (IOR = '0')) else '0';

-------------------------------------------------------End

-------------------------------------------------------Register I/O Signals And CPLD Pins Declaration

csr_data_ready <= Fifo_Empty1 and Fifo_Empty2; -- Data Ready Flag

csr_over_flag <= not(Fifo_Full1) and not(Fifo_Full2); -- Overflow Flag

Fifo_Write <= (CSR_WR and Data_In(0)) or

(csr_out_start_en and Out_Start); -- Fifo Write Pin

Interrupt <= (csr_data_ready and csr_ready_int_en) or

(csr_over_flag and csr_over_int_en); -- Interrupt Pin

Fifo_Reset <= CSR_WR and Data_In(3); -- Fifo Reset Pin

Fifo_Read <= DR_RD; -- Fifo Read Pin

-------------------------------------------------------End

-------------------------------------------------------CSR Write

process(Rst,CSR_WR)

begin

if (Rst = '1') then

csr_out_start_en <= '0';

csr_over_int_en <= '0';

csr_timer_mode <= "00000001";

elsif (CSR_WR = '1' and CSR_WR'event) then

csr_out_start_en <= Data_In(1);

csr_over_int_en <= Data_In(2);

csr_ready_int_en <= Data_In(4);

csr_timer_mode <= Data_In(15 downto 8);

else

Data_Out <= "ZZZZZZZZZZZZZZZZ";

end if;

end process;

-------------------------------------------------------End

-------------------------------------------------------CSR Read

process(DR_RD,CSR_RD)

begin

if (DR_RD = '1') then

Data_Out <= "ZZZZZZZZZZZZZZZZ";

elsif (CSR_RD = '1' and CSR_RD'event) then

Data_Out(0) <= csr_data_ready;

Data_Out(1) <= csr_out_start_en;

Data_Out(2) <= csr_over_int_en;

Data_Out(3) <= csr_over_flag;

Data_Out(4) <= csr_ready_int_en;

Data_Out(7 downto 5) <= "000";

Data_Out(15 downto 8) <= csr_timer_mode;

else

Data_Out <= "ZZZZZZZZZZZZZZZZ";

end if;

end process;

-------------------------------------------------------End

-------------------------------------------------------DR Read

process(DR_RD)

begin

if (CSR_RD = '1') then

Data_Out <= "ZZZZZZZZZZZZZZZZ";

elsif (DR_RD = '1') then

Data_Out(15 downto 8) <= Fifo_In1(7 downto 0);

Data_Out(7 downto 0) <= Fifo_In2(7 downto 0);

else

Data_Out <= "ZZZZZZZZZZZZZZZZ";

end if;

end process;

-------------------------------------------------------End

end cpld_struct;

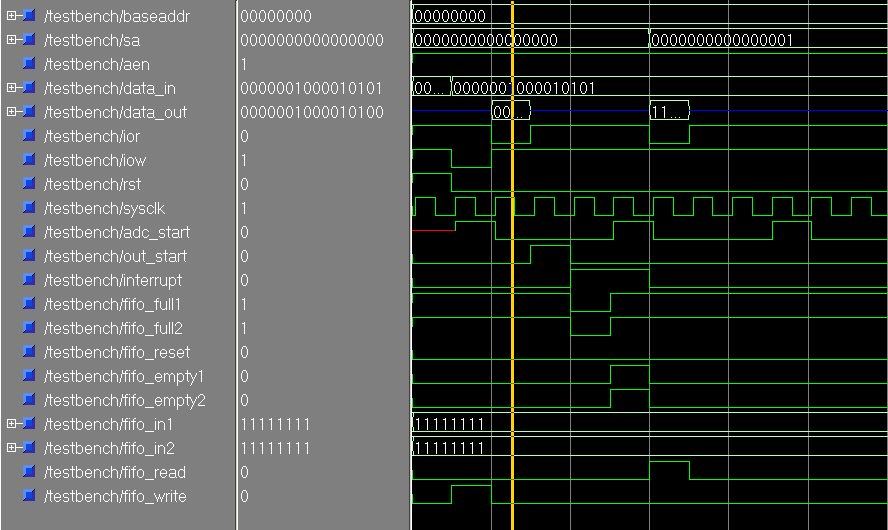

С помощью временной диаграммы проверим правильность функционирования схемы, описанной на языке VHDL.

Заключение:

В результате выполнения данного курсового проекта мной было разработано устройство сбора аналоговой информации, параметры которого удовлетворяют техническому заданию.

В ходе работ были получены новые знания, умения и навыки в области разработки аналоговой и цифровой техники, изучены принципы работы интерфейса USBиISA, проведён сравнительный анализ номенклатуры микросхем различных производителей, приобретён опыт разработки и отладки проектов, реализованных на микросхемах программируемой логики с использованием языкаVHDLи систем автоматизированного проектирования.

Список литературы:

Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П. “Проектирование систем на микросхемах программируемой логики” – СПб.: БХВ-Петербург, 2002

Угрюмов Е.П.”Цифровая схемотехника” – СПб.: БХВ-Петербург, 2002

Источники сети Internet:

Сайт фирмы “Analog Devices” – www.analog.com

Сайт фирмы “Cypress Semiconductor” – www.cypress.com