- •(Лэти).

- •Курсовой проект по дисциплине «пу и интерфейсы эвм» «Разработка аналогово-цифрового преобразователя».

- •1. Задание на курсовое проектирование (вариант №11).

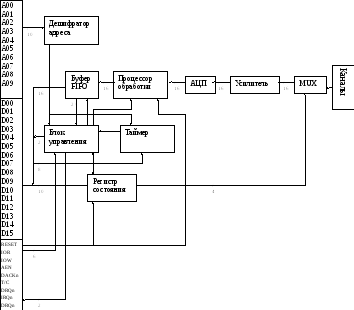

- •2. Структурная схема.

- •3. Выбор элементной базы.

- •Программируемый усилитель pga204.

- •Источник опорного напряжения ad780.

- •Программная модель устройства.

- •1.Регистр rc (режим записи). 180h

- •2. Регистр rc (режим чтения).

- •3. Регистр rd (режим чтения). 181h.

- •4 Регистр rd (режим записи).

- •Спецификация.

- •Содержание.

Периферийные

устройства.

Санкт-Петербургский Государственный Электротехнический Университет.

(Лэти).

Кафедра ВТ.

Курсовой проект по дисциплине «пу и интерфейсы эвм» «Разработка аналогово-цифрового преобразователя».

Преподаватель Павлов С.М.

Студент

Группа № 5373.

Вариант № 11.

<1999>

1. Задание на курсовое проектирование (вариант №11).

Разработать систему сбора аналоговой информации:

|

Магистраль |

ISA |

|

Диапазон входных напряжений |

50 мВ (термопара). |

|

Количество каналов |

32 (все дифференциальные) |

|

Входное сопротивление |

Не менее 10 МОм |

|

Разрядность АЦП |

16 |

|

Частота опроса любого канала |

Не менее 1Гц |

|

Гальваническая развязка от магистрали ISA |

есть |

Режимы обмена с магистралью:

-

Программный;

-

С прерыванием;

-

Прямой доступ к памяти.

Режим запуска:

-

От внутреннего таймера.

Особые требования:

-

Защита от перегрузки по входным напряжениям;

-

Наличие процессора предварительной обработки результатов измерения.

2. Структурная схема.

Устройство содержит два адресуемых порта доступных для записи\чтения. Выбираем адреса в доступном регионе адресов портов ввода-вывода, например, в диапазоне 180h-1EFh – этот диапазон адресов не зарезервирован и доступен для производителей аппаратного обеспечения. Примем адрес порта (PC – запись/чтение слова состояния) равным 180h. Адрес внутреннего порта таймера (для записи) и чтение содержимого буфера FIFO при чтении (PD) – 181h.

Запись порта 180 – установка регистра состояния устройства – настройка режимов работы:

-

установка номера канала;

-

сброс буфера FIFO и процессора предварительной обработки результатов;

-

запуск внутреннего таймера устройства;

-

разрешение режима прерываний по готовности;

-

установка режима ПДП;

-

выбор внутреннего регистра таймера.

Из этого порта можно прочитать состояние буфера FIFO.

Порт 181:

-

программирование таймера (запись);

-

чтение слова из буфера FIFO.

Все цифровые сигналы подключаются к аналоговым микросхемам, включаются через гальваническую развязку.

Для обеспечения правильной работы устройства, сигнал RESDRV – низкий уровень при загрузке машины, сбрасывает регистр состояния и процессор обработки результатов.

Сигналы со внешних каналов мультиплексируются и подаются на дифференциальный усилитель (PGA204). Для усиления сигнала до диапазона 10В необходим коэффициент усиления G=10, тогда напряжение на выходе усилителя рассчитывается по формуле: V0=G(V+in- V-in).

В усиленный сигнал подается на вход аналого-цифрового преобразователя (AD976) и обрабатывается с помощью микроконтроллера Intel MSC-51.

Обработанный сигнал поступает в буфер FIFO. Буфер вырабатывает сигналы empty и full, с учетом этих флагов в блоке управления инициируются аппаратное прерывание, или запрос на прямой доступ к памяти (при разрешении соответствующих режимов). Содержание буфера адресуется через порт 181 и может быть прочитано при программном обращении к устройству.

Управляющие сигналы в схеме управления тактируются таймером (ВИ53), запись во внутренние регистры доступна через порт 181, а адресация происходит с помощью 2-х байтов регистра состояния.

Блок управления и дешифратор адреса реализуются с помощью PLM.