- •1. Задание на курсовое проектирование. 4

- •2.Регистровая модель устройства.

- •2.1 Регистр csr.

- •2.2 Регистр dr.

- •3. Структурная схема устройства.

- •4. Выбор элементной базы.

- •5. Разработка принципиальной электрической схемы устройства.

- •5.1 Расчёт потребляемой мощности.

- •6. Пример программы для работы с устройством.

- •Выводы.

- •Список использованной литературы.

3. Структурная схема устройства.

┘└ Внешний

запуск

ПЛМ, использованное при построении, играет роль схемы, вырабатывающей сигналы управления:

– CSRWR, CSRRD - чтение и запись в/из регистра CSR, соответственно;

– DRWR, DRRD - чтение и запись в/из регистра DR, соответственно;

– DIR, OE - сигналы, необходимые для входного буфера данных: определение направления передачи данных (запись/чтение) и перевода своих выходов в Z-состояние, при работе с другими устройствами, соответственно;

– IOCS/16 - сигнал, задающий 16-разрядный режим обмена на шине ISA.

Выработка данных сигналов осуществляется на основе дешифрации адреса и анализа сигналов чтения или записи, поступающих с шины ISA. Для базового адреса в схеме допускается выбор значения седьмого бита. Особенности некоторых остальных бит: первый бит определяет выбор регистра CSR/DR, младший всегда должен быть равен “0".

__ __ __ __ __ __ __ __ ___ ___ ___

CSRWR=(A9∙A8∙A7∙A6∙A5∙A4∙A3∙A2∙A1∙A0∙AEN∙IOW∙SW)v

__ __ __ __ __ __ __ ___ ___

(A9∙A8∙A7∙A6∙A5∙A4∙A3∙A2∙A1∙A0∙AEN∙IOW∙SW)

______

__ __ __ __ __ __ __ __ ___ ___ ___

______

__ __ __ __ __ __ __ __ ___ ___ ___

CSRRD=(A9∙A8∙A7∙A6∙A5∙A4∙A3∙A2∙A1∙A0∙AEN∙IOR∙SW) &

__ __ __ __ __ __ __ ___ ___

__ __ __ __ __ __ __ ___ ___

(A9∙A8∙A7∙A6∙A5∙A4∙A3∙A2∙A1∙A0∙AEN∙IOR∙SW)

__ __ __ __ __ __ __ ___ ___ ___

DRWR=(A9∙A8∙A7∙A6∙A5∙A4∙A3∙A2∙A1∙A0∙AEN∙IOW∙SW) &

__ __ __ __ __ __ ___ ___

(A9∙A8∙A7∙A6∙A5∙A4∙A3∙A2∙A1∙A0∙AEN∙IOW∙SW)

_ ____

__ __ __ __ __ __ __ ___ ___ ___

____

__ __ __ __ __ __ __ ___ ___ ___

DRRD=(A9∙A8∙A7∙A6∙A5∙A4∙A3∙A2∙A1∙A0∙AEN∙IOW∙SW) &

__ __ __ __ __ __ ___ ___

__ __ __ __ __ __ ___ ___

(A9∙A8∙A7∙A6∙A5∙A4∙A3∙A2∙A1∙A0∙AEN∙IOW∙SW)

______

______

DIR=CSRWR v DRWR

______ _____

______ _____

OE=DIR v CSRRD v DRRD

4. Выбор элементной базы.

1. Коммутатор каналов.

В качестве коммутатора дифференциального сигнала была выбрана микросхема ADG7502 (4 Channel Analog Multiplexer).

2. Программируемый усилитель. PGA205.

A0, A1, Digital Ground – входы задают коэффициент усиления G=1,2,4,8 V/V.

V+in, V- in - вход усилителя.

V+, V- - напряжение питания схемы (±15 В).

Vos, Vadj – входы компенсации смещения усилителя, для настройки используется переменное сопротивление 200кОм …1МОм.

VOS = VOSI + VOSO / G, где VOSI – смещение входа; VOSO – смещение выхода; G – коэффициент усиления.

Входное сопротивление усилителя, равное 10 МОм, удовлетворяет условию задания на ограничение входного сопротивления схемы на аналоговый сигнал.

3. АЦП.

Критерием, по которому был выбран АЦП (кроме требований, указанных в задании), являлась минимизация аппаратных затрат на гальваническую развязку. Следствием данного условия явился выбор АЦП с последовательным выходом – AD667 фирмы “Analog Devices”.

VIN – вход аналогового сигнала (10 В).

AGND SENSE - вход базовой «земли».

VREF – опорное напряжение. (+5В)

AGND – аналоговая «земля».

CAL – вход управления автокалибровки. Сигнал имеет активный высокий уровень.

CLK – тактирование АЦП.

SAMPLE – запуск АЦП. Запуск происходит по положительному фронту.

BUSY – сигнал занятости микросхемы Принимает высокое значение во время выполнения преобразования или автокалибровки.

SCLK – выход тактирования последовательного результата преобразования. В остальных случаях выход имеет высокий уровень.

SDATA – выход последовательных данных.

4. Оптопара (оптрон).

Основным требованием для выбора микросхемы являлась дешевизна, а также конструктивное исполнение (2 оптрона в 1 корпусе).

По данным критериям была выбрана микросхема HCPL-2730 фирмы Agilent Technologies.

5. Высокоточный стабилизатор напряжения. AD586.

Vin – входное напряжение. (+15В)

Vout – выходное стабилизированное напряжение. (10,0±0,005 В)

GROUND – «земля»

TRIM, NOISE REDUCTION – входы балансировочного резистора и фильтрующего конденсатора.

6. FIFO.

Определяющим фактором выбора FIFO явился последовательный вход и параллельный выход данных. Данным критериям удовлетворяет асинхронное FIFO фирмы “Integrated Device Technology” IDT72132 с организацией 2048 х 9.

7. Генератор. КР531ГГ1

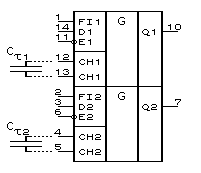

Микросхема содержит два одинаковых автоколебательных мультивибратора, у каждого из которых имеются входы управления частотой повторения импульсов (FI1 и FI2) и входы выбора диапазона генерируемых частот (D1 и D1), инверсные входы разрешения работы (E1 и E2), а также входы СH подключения внешнего резонатора (конденсатора или пьезоэлектрического резонатора). На выходе мультивибраторов (Q1 и Q2) формируются прямоугольные импульсы напряжения типа "меандр" (скважность Q=2). Частота следования выходных импульсов а может рассчитываться по выражению:

f0= 5∙10-4/ сτ,где сτ - величина электрической емкости навесного конденсатора.

Емкость навесных конденсаторов сτ выбирается в диапазоне 9 пФ - 500 мкФ.

Максимальная частота генерации составляет 45 МГц при емкости нагрузки не более 15 пФ.

Все остальные узлы и элементы были реализованы на микросхемах серии 1533.