Комбинационные схемы: полусумматор, одноразрядный сумматор.

Комбинационные схемы - это схемы ,логические состояния на выходах которых однозначно определяются комбинацией логических сигналов на их входах в данный момент времени и не зависит от комбинации логических сигналов на их входах в предыдущие моменты времени.

Комбинационные схемы – это схемы не обладающие памятью.

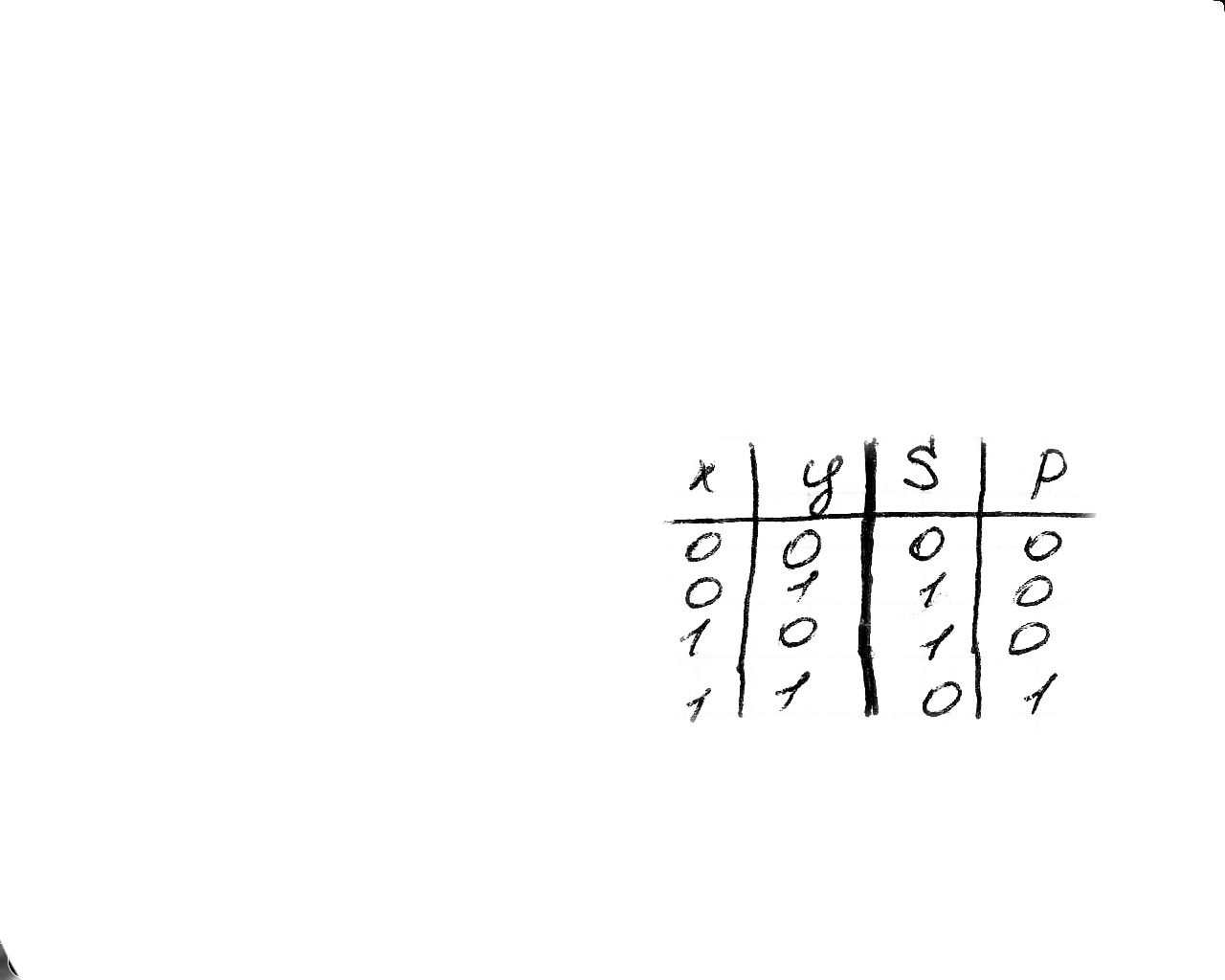

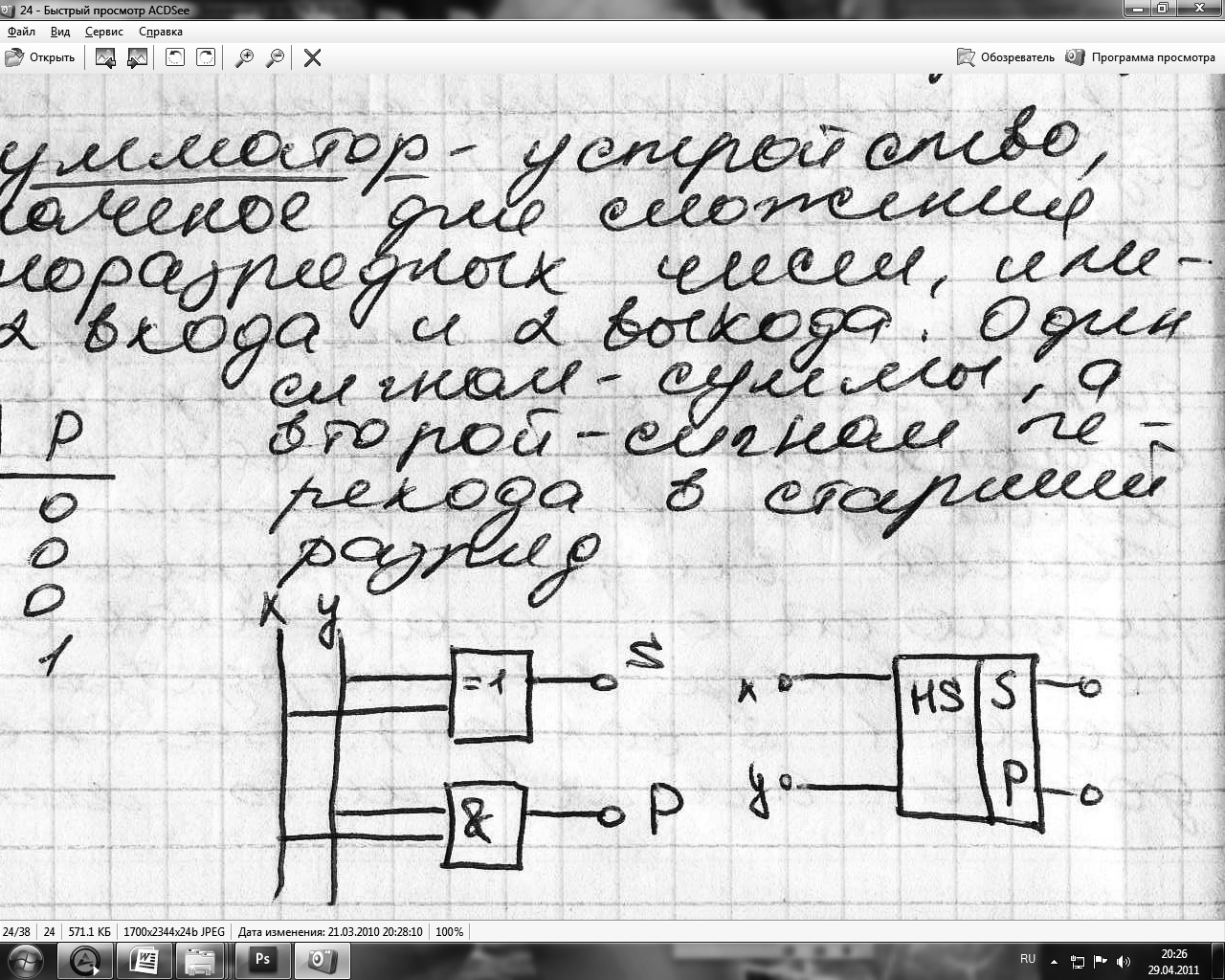

Полусумматоры – устройство , предназначенное для сложения двух одноразрядных чисел , имеющих 2 входа и 2 выхода . Один сигнал суммы ,а второй перехода в старший разряд.

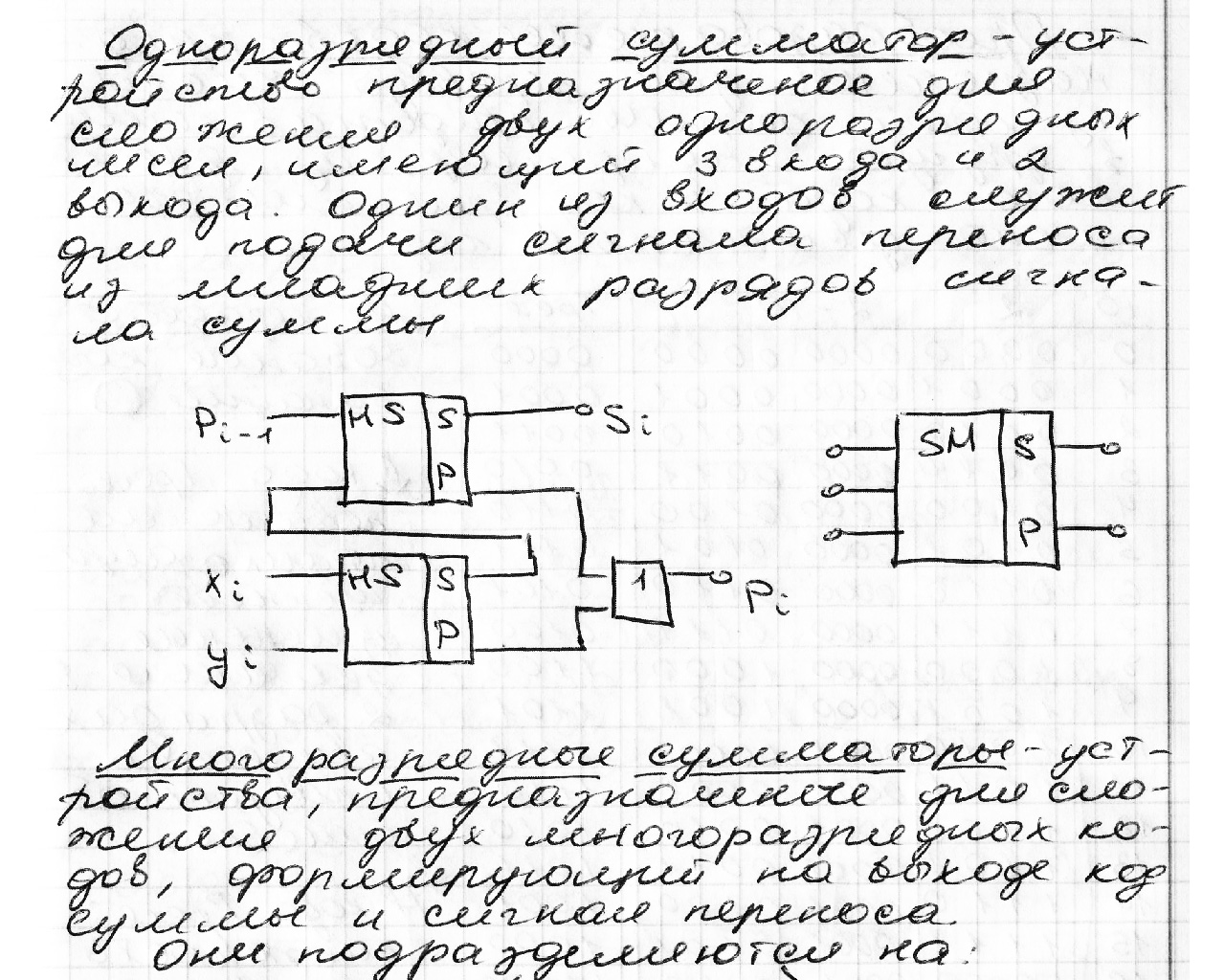

Одноразрядный

сумматор - устройство предназначенное

для сложения двух одноразрядных чисел,

имеющих 3 входа и 2 выхода. Один из входов

служит для подачи сигнала переноса из

младших разрядов сигналов суммы.

Комбинационные схемы: многоразрядные сумматоры.

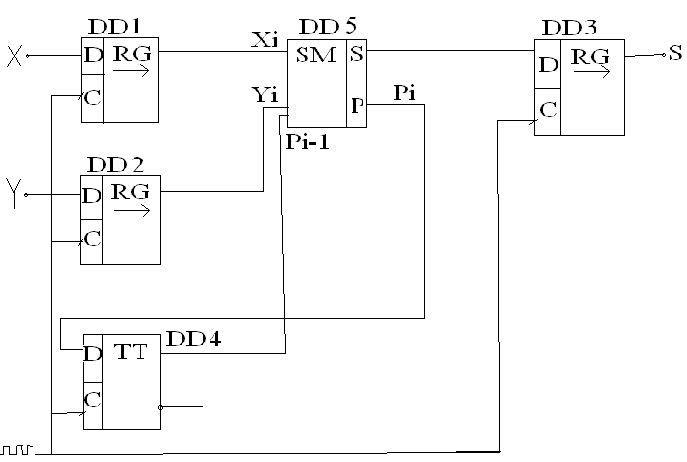

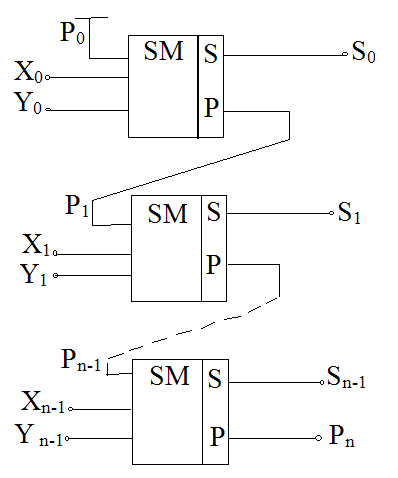

Многоразрядные сумматоры – устройства, предназначенные для сложения двух многоразрядных кодов, формирующий на выходе код суммы и сигнал переноса.

Подразделяются на: последовательные и параллельные.

Последовательные сумматоры: операция выполняется последовательно, разряд за разрядом, начиная с младшего. А в параллельных: все разряды суммируемых входов выполняются одновременно.

Операция суммирования регистров осуществляется с помощью одного и того же одноразрядного сумматора. Достоинство: малый объём микросхем. Недостатки: малое быстродействие.

П араллельный

многоразрядный сумматор с последовательным

переносом.

араллельный

многоразрядный сумматор с последовательным

переносом.

Окончательное время суммирования – с временем переноса.

С параллельным переносом. Для повышения быстродействия используют сумматор с параллельным переносом, в котором формируется одновременно для всех разрядов в блоке ускоренного переноса.

Для суммирования многоразрядных чисел используются параллельные многоразрядные сумматоры с групповым переносом.

Комбинационные схемы: преобразователи кодов; шифраторы.

Преобразователь кода- это цифровое устройство комбинационного типа, предназначенное для изменения вида кодирования информации. Например преобразования двоичного кода в двоично-десятичный код.

Условное графическое обозначение преобразователя кода:

На микросхемах обозначаются как ПР.

Для выходов преобразователей кодов можно записать логические уравнения:

;

;

;

;

;

;

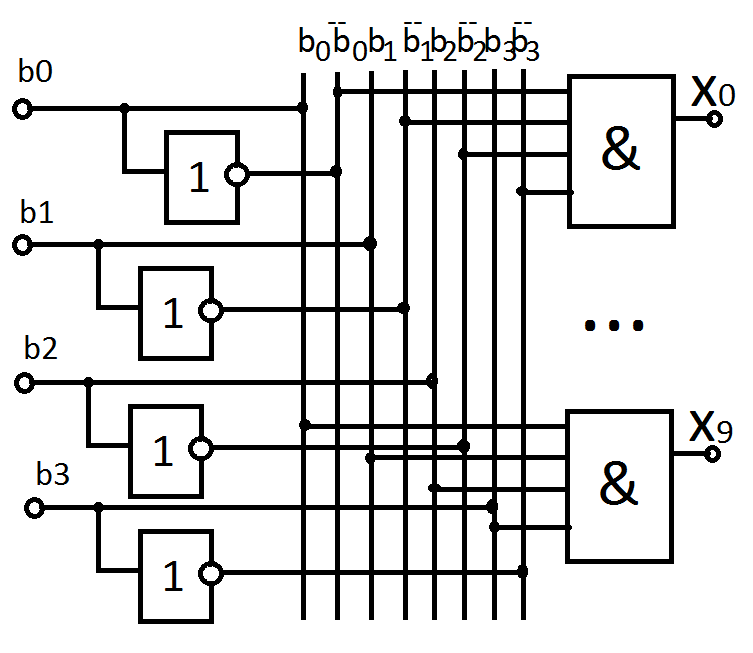

Шифратором называют комбинационное логическое устройство предназначенное для преобразования десятичного кода в двоичный.

У словно

графическое обозначение:

словно

графическое обозначение:

Q0=X1+X3+X5+X7+X9

Q1=X2+X3+X6+X7

Q3=X4+X5+X6+X7

Q3=X8+X9

Шифратор

имеющий

входов и n

выходов называется полный, в противном

случае неполный.

входов и n

выходов называется полный, в противном

случае неполный.

Нарисуем упрощённую схему шифратора 8 в 3.

Комбинационные схемы: дешифраторы.

Дешифратор – устройство для преобразования двоичного кода в десятичный. Маркировка ИД.

Е сли

число выходов 2n,

где n

– число входов, дешифратор – полный,

иначе – неполный.

сли

число выходов 2n,

где n

– число входов, дешифратор – полный,

иначе – неполный.

В

общем случае:

;

;

;

;

;

; ;

…

;

…

.

.

Дешифратор может иметь парафазные входы для подачи инверсного хода.

По способу построения – линейные, многоступенчатые. Многоступенчатые – прямоугольные, пирамидальные.

Э то

линейный дешифратор, обладает наибольшим

быстродействием, но с увеличением

разрядности возрастает нагрузка на

каждый вход. Поэтому применяется для

построения дешифраторов с n<=

4. При n>4

Дешифраторы выполняют по многоступенчатой

форме. В прямоугольных – входной разряд

разбивают на группы и они дешифруются

дешифраторами 1-й степени, во второй

ступени используется прямоугольная

матрица 2-хкодовых логических элементов.

В пирамидальных используются двухкодовые

логические элементы в каждой ступени,

общее количество элементов –

Nэл=22(2n-1-1)

где n-разрядность.

то

линейный дешифратор, обладает наибольшим

быстродействием, но с увеличением

разрядности возрастает нагрузка на

каждый вход. Поэтому применяется для

построения дешифраторов с n<=

4. При n>4

Дешифраторы выполняют по многоступенчатой

форме. В прямоугольных – входной разряд

разбивают на группы и они дешифруются

дешифраторами 1-й степени, во второй

ступени используется прямоугольная

матрица 2-хкодовых логических элементов.

В пирамидальных используются двухкодовые

логические элементы в каждой ступени,

общее количество элементов –

Nэл=22(2n-1-1)

где n-разрядность.

Комбинационные схемы: мультиплексор, демультиплексор.

Мультиплексор предназначен для управляемой передачи данных от нескольких источников информации на один выходной канал с помощью команды, называемой адресом. Каждый канал имеет свой адрес, в соответствии с которым будет подключаться D0, D1, D2 или D3. Мульт-р можно использовать для построения функций алгебры логики.

Обратная

задача решается демультиплексором.

Адресная линия получает адрес выходной

ли

Формирование задержанных импульсов.

Необходимо для временного согласования распространения сигналов по различным путям в цифровых устройствах с целью борьбы с критическими временными состязаниями нарушающими работоспособность автоматов с памятью.

На практике используют различные варианты задержки: отрезки обычных или специальных кабелей, цепочки логических элементов, RC цепочки, одновибраторы, схемы деления частоты тактовых сигналов.

Цепочки логических элементов- инверторы n-штук. Время задержки n дискретностью.

t d=Ntd0

d=Ntd0

Время задержки десятки сотни мкс.

З адержку

на большее время осуществляют с помощью

RC-цепи.

адержку

на большее время осуществляют с помощью

RC-цепи.

td=RCln2

Элемент задержки

Формирователи импульсов по длительности.

Формирователи импульсов служат для улучшения формы импульса (расширения, сужения, стандартизации).

Для формирования формы импульсов применяют одновибраторы. На вход поступает импульс любой формы на выходе — прямоугольной.

Схема формирователя импульсов заданной длительности:

tимп. = (ln2)C1R1

R1=10кОм—1Мом

C1≤1мкФ

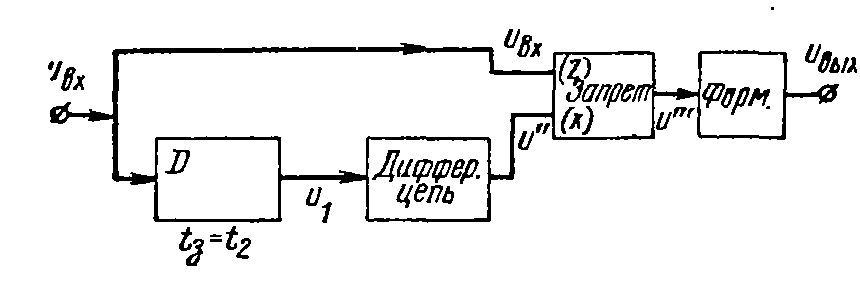

Для изменения длительности импульсов используют схему:

td

—

линия

задержки

td

—

линия

задержки

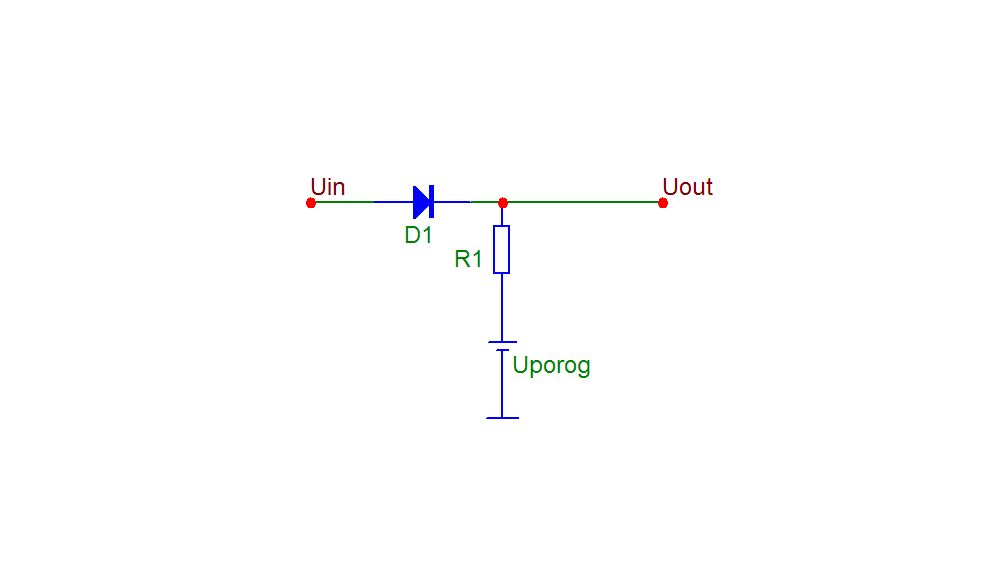

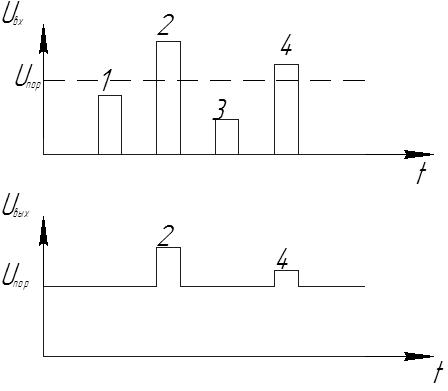

Селекторы импульсов амплитудные.

Селекторы импульсов

При решении различных технических задач возникает необходимость произвести отбор импульсов, отличающихся от остальных определенным признаком. При селекции форма выходного импульса может изменятся с помощью квазиселектора. Селекция производится по амплитуде, длительности и времени.

Амплитудные селекторы

Это устройства, отбирающие импульсы по амплитуде. С их помощью выделяют импульсы с амплитудой большей(меньшей) порогового уровня селекции или в заданном диапазоне.

Для отбора меньшей амплитуды испоьзуют след. схемы

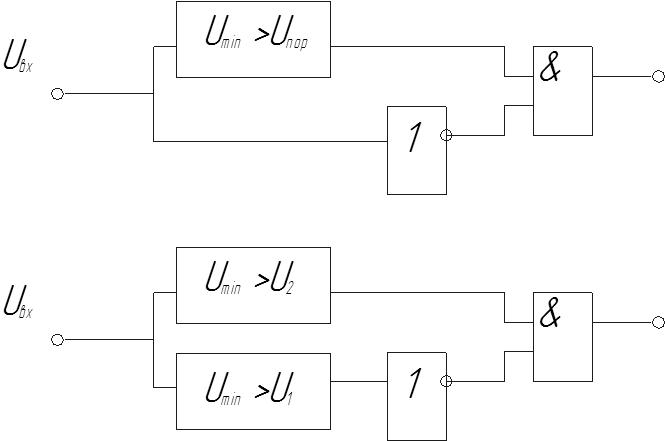

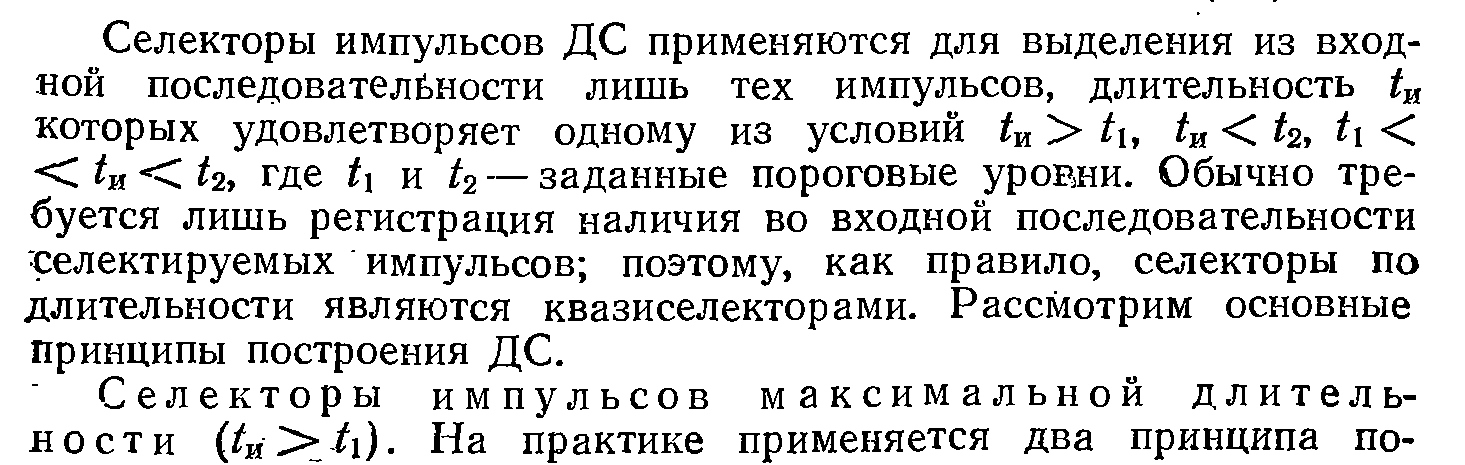

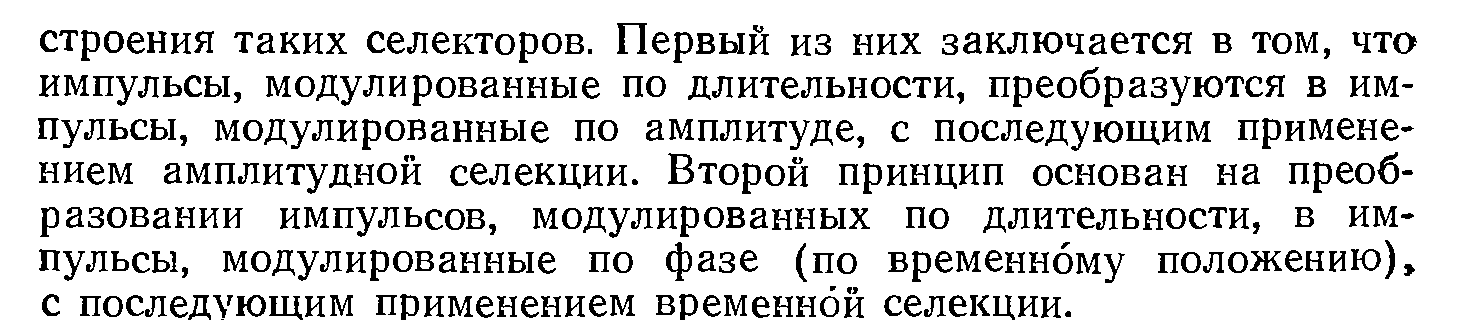

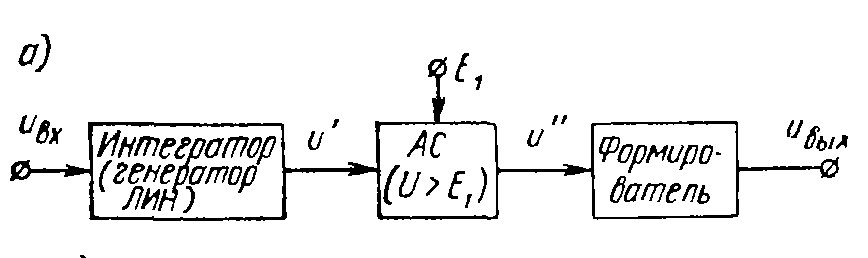

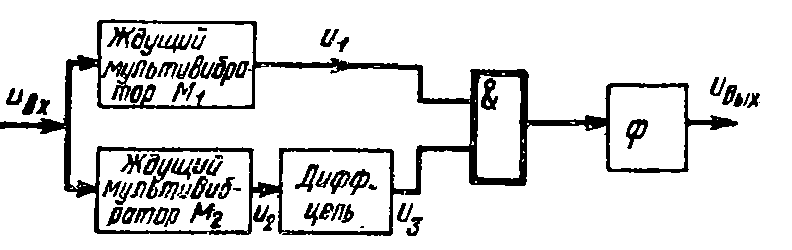

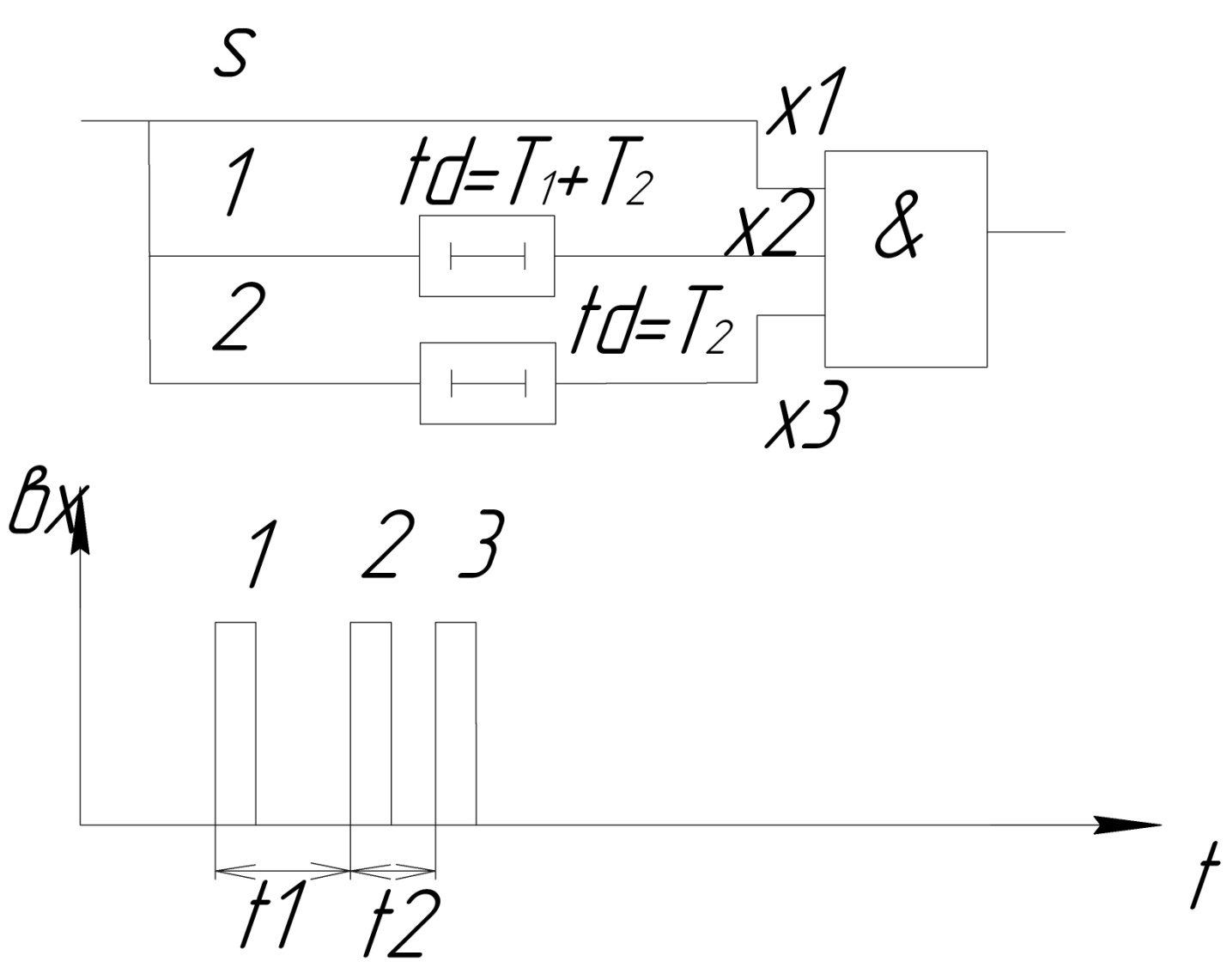

Селекторы импульсов по длительности.

![]()

Селекторы импульсов временны́е.

Представляют собой устройства, отбирающие те импульсы, которые поступают на вход в определенном интервале времени. Такая селекция обеспечивается сравнением заданной последовательности импульсов со стробом.

Интегральные таймеры: назначение, структурные схемы.

Одно

из наиболее широко применяемых аналоговых

цифровых схем. Они предназначены для

формирования импульсов с регулируемой

длительностью и скважностью:

коэффициент

заполнения.

коэффициент

заполнения.

Все современные таймеры можно разделить на однотактные и двухтактные со встроенным счетчиком.

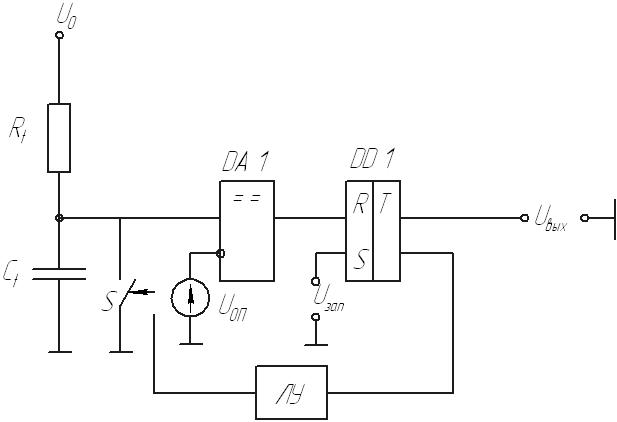

Структурная схема однотактного таймера:

Длительность

формирование интервала определяется

параметрами внешней времязадающей

цепи. По активному значению сигнала

напряжение запуска RS

– триггер устанавливается в единичное

состояние, что приводит к размыканию

ключа S.

В момент когда напряжение на конденсаторе

достигает уровня опорного напряжения

происходит срабатывание компаратора

DA

1, так же срабатывает RS

– триггер. Ключ S

при этом замыкается. Конденсатор

разряжается. Однотактный таймер,

построенный по описанной схеме может

формировать на выходе только одинаковые

импульсы длительностью от единиц

микросекунд до часов. Для обеспечения

формирования последовательности

импульсов, схема должна быть дополнена

вторым компоратором.

цепи. По активному значению сигнала

напряжение запуска RS

– триггер устанавливается в единичное

состояние, что приводит к размыканию

ключа S.

В момент когда напряжение на конденсаторе

достигает уровня опорного напряжения

происходит срабатывание компаратора

DA

1, так же срабатывает RS

– триггер. Ключ S

при этом замыкается. Конденсатор

разряжается. Однотактный таймер,

построенный по описанной схеме может

формировать на выходе только одинаковые

импульсы длительностью от единиц

микросекунд до часов. Для обеспечения

формирования последовательности

импульсов, схема должна быть дополнена

вторым компоратором.