1.2. Архитектуры с распределенной областью памяти

Ко второму важному классу параллельных машин относятся многопроцессорные системы с распределенной областью памяти - message-passing architectures (MPA). MPA используют законченные компьютеры, включающие микропроцессор, память и подсистему ввода-вывода, как узлы для построения системы, объединенные коммуникационной средой, обеспечивающую взаимодействие процессоров посредством простых операций ввода-вывода. Структура высокого уровня для MPA практически такая же, как и для NUMA машин, т.е. машин с разделяемой памятью, показанных на рис. 1.6. Первое отличие состоит в том, что коммуникации интегрированы в уровень ввода-вывода, а не в систему доступа к памяти. Этот стиль дизайна имеет много общего с сетями из рабочих станций или кластерными системами, за исключением того, что в МРА пакетирование узлов обычно более плотное, нет монитора и клавиатуры на каждом узле, а производительность сети намного выше стандартной. Интеграция между процессором и сетью имеет склонность быть более тесной чем традиционные структуры ввода-вывода, которые поддерживают соединения с оборудованием, которое более медленное, чем процессор. Начиная с посылки сообщения MPA есть фундаментальное взаимодействие ПРОЦЕССОР – ПРОЦЕССОР.

Системы с распределенной памятью имеют существенную дистанцию между программной моделью и действительными аппаратными примитивами. Коммуникации осуществляются через средства операционной системы или библиотеку вызовов, которые выполняют много акций более низкого уровня, включающих операции коммуникации.

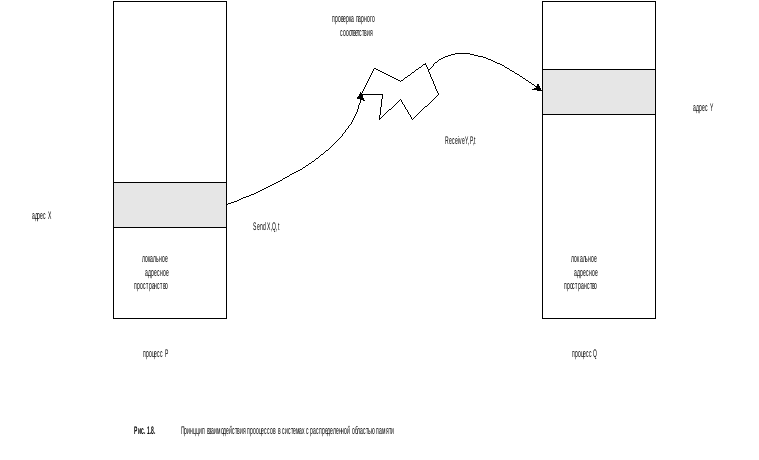

Наиболее общие операции взаимодействия на пользовательском уровне (user-level) в MPA есть варианты посылки (SEND) и получения (RECEIVE) сообщения. Совместный механизм SEND и RECEIVE, вызванный передачей данных из одного процесса в другой, показан на рис 1.8.

Передача данных из одного локального адресного пространства к другому произойдет, если посылка сообщения со стороны процесса - отправителя будет востребована процессом - получателем сообщения.

С этой целью в большинстве системах с распределенной памятью сообщение специфицируется операцией SEND, которая добавляет к сообщению специальный признак (tag), а операция RECEIVE в этом случае выполняет проверку сравнения данного признака.

Сочетание посылки и согласованного приема сообщения (на основе совпадения признаков) выполняет логическую связку – синхронизацию события, т.е. копирования из памяти в память. Имеется несколько возможных вариантов синхронизаии этих событий, в зависимости от того, завершиться ли SEND к моменту, когда RECEIV будет выполнен или нет (т.е. будет ли снова доступен буфер посылки для использования до момента получения подтверждения приема). Похожим образом RECEIV может, в принципе, подождать до момента согласованной посылки (SEND) или использовать "почтовый ящик" для получения сообщения. Каждый из этих вариантов имеет несколько различную интерпретацию и различные требования к реализации.

Механизм посылки сообщений долго использовался как средство коммуникации и синхронизации совокупности арбитрирующих взаимодействующих последовательных процессов, даже на одном процессоре. В качестве примеров можно привести языки программирования типа CSP и Occam, наиболее общие функции операционных систем, типа SOCKETS.

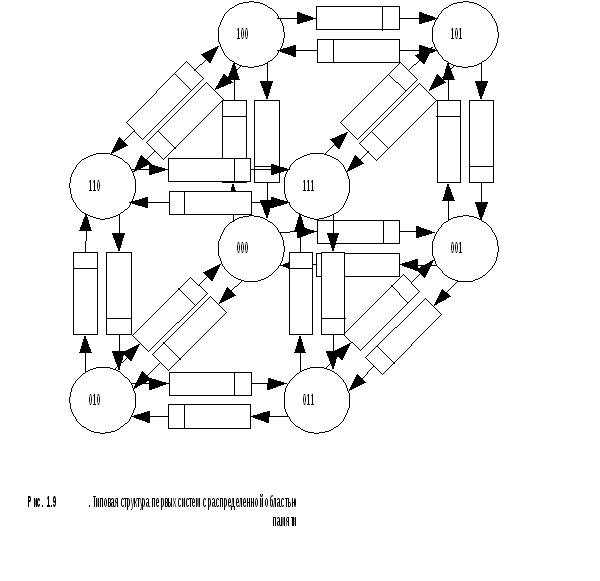

Первые машины с распределенной областью памяти обеспечивали аппаратную поддержку примитивов (команд), которые очень напоминали простую абстракцию взаимодействия SEND/RECEIV на пользовательском уровне, с некоторыми дополнительными ограничениями. Каждый узел системы соединялся с определенным (фиксированным) числом соседей по регулярной схеме (образцу) на основе связи точка-точка (poin-to-point), поведение которой, в свою очередь, описывалось простым FIFO. Такой тип конструкции для минимального 3D куба показан на рис. 1.9, где каждый узел имеет связи с соседями по трем направлениям через буфер FIFO.

В ранних системах, обычно, использовалась структура гиперкуба (на 2n узлов), в которой каждый узел соединялся с n другими узлами, бинарные адреса которых отличались на один бит. Другие машины имели решетчатую структуру, где узлы соединялись с соседями по двум или трем измерениям. Такая технология для более ранних машин была важна, потому что только соседние процессоры могли быть использованы в качестве адресата в операциях приема-посылки. Процесс - отправитель посылал сообщение, а процесс – получатель получал сообщение через канал - link. FIFO было маленьким, так что отправитель не успевал закончить формирование сообщения до момента, когда получатель начинал его читать, поэтому посылка блокировалась до момента начала приема (на современном языке это называется синхронной передачей сообщений, т.к. два события совпадают по времени). Детали передачи данных были скрыты от программиста в специальной, библиотеке, формирующей слой программного обеспечения между запросами на прием и передачу и реальным аппаратным обеспечением.

Прямое FIFO проектирование вскоре было заменено на более универсальное, при котором передача сообщений обеспечивалась механизмом прямого доступа к памяти direct memory access (DMA) на каждой стороне взаимодействующих процессов. DMA устройства представляют собой специализированный контроллер, который перемещает данные между памятью и устройством ввода-выводда без участия процессора до момента окончания передачи. Использование DMA позволяет осуществить неблокируемые посылки, при которых отправитель в состоянии инициировать посылку и одновременно продолжать полезные вычисления (или даже выполнять прием). На приемном конце сообщение принимается через устройство DMA, пересылается в буферный слой сообщений и ставится в режим ожидания до тех пор, пока заданный процесс выполнит соответствующий прием, после чего (в этот момент) данные копируются в адресное пространство процесса – получателя.

Физическая организация коммуникационной сети настолько влияла на программные модели этих ранних машин, что параллельные алгоритмы очень часто именовались в соответствии со спецификой внутренней топологии соединений, например, кольцо (Ring) , матрица (grid), гиперкуб (hypercube). Однако для придания большей универсальности, системы стали обеспечивать поддержку взаимодействия между независимыми процессорами, а не только между соседними. Первоначально это поддерживалось перенаправлением данных внутри уровня сообщений вдоль каналов (links) в сети. Вскоре эта распределяющая функция была перенесена на уровень аппаратного обеспечения. Каждый узел стал содержать процессор с памятью и коммутатор, который мог перенаправлять сообщения. Тем не менее, в таком подходе, известным под названием store-and-forward, время передачи сообщения пропорционально числу необходимых этапов передачи в сети, поэтому, все-таки, влияние топологии внутренних соединений оставалось существенным.

Такое внимание к сетевой топологии было значительно ослаблено, в связи с появлением гораздо более универсальных сетей, которые поплайнизировали передачу сообщения через каждый коммутатор, формирующий внутреннюю сеть. В наиболее современных машинах с распределенной памятью нарастающая задержка, вносимая каждым этапом передачи (скачком) достаточно мала. Это существенно упрощает программную модель [2]. Обычно процессор рассматривается как простой формирователь линейной последовательности с одинаковыми затратами на коммуникацию. Другими словами, коммуникационная абстракция отражает главным образом организационную структуру, показанную на рис 1.6. Один из важных примеров такой машины является IBM SP-2, изображенной на рис 1.10.

Это масштабируемый параллельный компьютер, состоящий из узлов на базе рабочих станций RS6000, масштабируемой сети и сетевым интерфейсом (NI)– network interface card (NIC), содержащим специализированный процессор (i860). NIC соединен с MicroChannel I/O bus и содержит драйверы сетевого линка, память (DRAM) для буферирования сообщений. Для реализации DMA, модуль содержит процессор i860, управляющий перемещением данных между памятью и сетью. Сеть представляет собой каскадное 8x8 коммутируемое перекрестное соединение (crossbar switches) (см. рис. 1.3а). Скорость передачи сообщений по линкам составляет 40 Mb/s в каждом направлении.

Другим примером является параллельный компьютер Intel Paragon, показанный на рис 1.11.

Intel Paragon иллюстрирует наиболее плотное аппаратное пакетирование в узлах. Каждая плата (узел) представляет собой SMP с двумя или более процессорами (i860) и кристалл сетевого интерфейса (NI) связанный с шиной памяти (Memory bus). Один из процессов специализируется на обслуживании сети. Узел имеет механизм DMA для передачи блоков данных через сеть высокого уровня. Сеть представляет собой 3D куб, аналогичный структуре сети компьютера CRAY T3E. Линки имеют пропускную способностью 175 Mb/s в каждом направлении.

В заключении, МРA и разделяемое адресное пространство являются двумя очевидно различными программными моделями, каждая из которых обеспечивает ясную парадигму для разделения коммуникации и синхронизации. Тем не менее лежащие в основе данных машин базовые структуры постепенно объединяются в рамках общей организации, представляемой набором законченных компьютеров усиленных специальным контроллером, соединяющим каждый узел с расширяемой коммуникационной сетью. Подробнее обобщенная архитектура параллельных систем будет рассмотрена ниже, в разделе 1.6.

1.3. МАТРИЧНЫЕ СИСТЕМЫ

Третий важный класс параллельных машин – матричные системы - относятся к классу single-instruction-multiple-data machines (SIMD) или data parallel architectures. Ключевой характеристикой этой модели программирования data parallel programming model [2] является то, что операция может быть выполнена параллельно на каждом элементе большой регулярной структуры данных, таких как массивы и матрицы.

Компьютерная таксономия, известная как Flynn’s taxonomy (Flynn 1972), появившаяся в изданиях начала 70–х годов, определяет структуру системы в терминах числа одновременно выполняемых различных инструкций и числа обрабатываемых элементов данных. В этом случае обычные последовательные компьютеры определяются как системы с одиночным потоком команд и одиночным потоком данных single-instruction-single-date (SISD), а параллельные машины, построенные из множества обычных процессоров как системы с множественным потоком команд и множественным потоком данных multiple-instruction-multiple-data (MIMD). Альтернативой им стали системы класса одиночного потока команд и множественного потока данных single-instruction-multiple-data (SIMD). Исторически, такой подход появился в середине 60‑х. Идея была в том, что вся последовательность инструкций могла бы быть консолидирована в управляющем процессоре. Процессор данных включал бы только ALU, память и обеспечивал простое взаимодействие с ближайшими соседями.

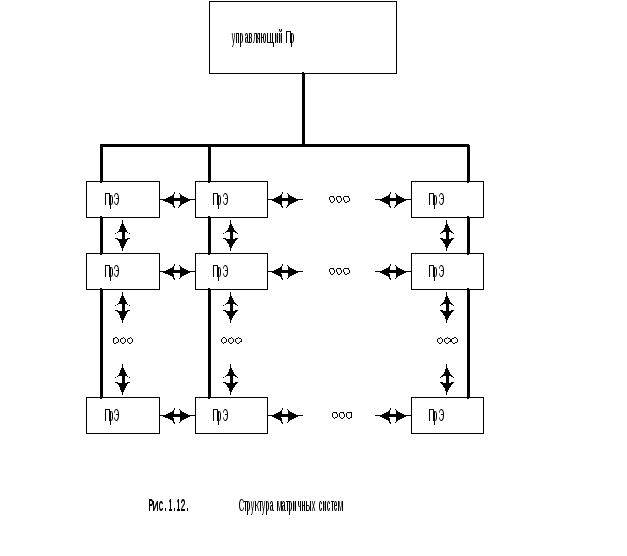

В SIMD машинах модель программирования (data parallel programming model) была напрямую реализована в физическом аппаратном уровне. Обычно управляющий процессор (Пр) осуществлял рассылку каждой инструкции по массиву процессорных элементов (data processing element) (ПрЕ), которые были соединены между собой в форме регулярной решетки, как показано на рис 1.12

Матричные системы ориентированы на большой класс вычислительных задач, которые требуют выполнения матричных операций или обработки массивов, т.е. когда выполняются одинаковые операции на уровне каждого элемента массива или матрицы, вовлекающие в процесс вычисления соседние элементы. Т.о. управляющий процессор инструктирует процессоры данных по выполнению каждой операции над локальным элементом данных или все выполняют операцию коммуникации-обмена данных (все сразу).

В дальнейшем, в середине 1970-х, векторные процессоры затмили собой развитие других многопроцессорных систем. Векторные процессоры интегрировали скалярный процессор с коллекцией функциональных единиц, которые оперировали с векторными данными на памяти с поплайновой организацией. Способность оперировать над векторами в любом месте памяти ликвидировало необходимость размещения используемых структур данных в жесткую структуру внутренних связей и значительно упростило проблему получения объединенных данных.

Набор команд первого векторного процессора CDC Star-100 включал в себя векторные операции, которые позволяли комбинировать два источника векторов из памяти и создавать в памяти вектор результата. Машина работала на полной скорости тогда, когда векторы были соседними и, следовательно, основное время тратилось на простое транспонирование матриц. Сенсационное изменение произошло в 1976 году, когда был представлен CREY-1, в котором концепция LOAD-STORE архитектуры была расширенна на обработку векторов и реализована в процессорах CDC 6600 и CDC 7600 (и продолжена в современных RISC машинах). Векторы в памяти, с любым фиксированным шагом по индексу, были перенесены в или из соседних (близких) регистров посредством загрузки вектора и хранения инструкций. Арифметика выполнялась на векторных регистрах. Использование очень быстрых скалярных процессоров (80 MHz), интегрированных с векторными операциями и использующих большую полупроводниковую память, привело к мировому господству суперкомпьютеров рассматриваемого класса. Более чем 20 последующих лет, CRAY Research лидировал на суперкомпьютерном рынке, увеличивая пропускную способность передачи векторов в памяти, число процессоров, число векторных поплайнов и длину векторных регистров.

Второй раз SIMD компьютеры (data parallel machine) пережили эпоху своего возрождения в середине 1980, когда развитие VLSI-design привело к появлению доступного 32 разрядного микропроцессора (это были, так называемые, одноразрядные секционные микропроцессоры или микропроцессоры с разрядно - модульной организацией). В уникальной петлевой архитектуре в data parallel режиме было размещено 32 простых одноразрядных элементарных процессоров на одном чипе, вместе с серией соединений с соседними процессорами. Совокупность последовательных инструкций была размещена на управляющем процессоре. Главное было в том, что такие системы с несколькими серийными процессорными элементами были созданы и имели разумную цену.

В дальнейшем технологические факторы, которые сделали это bit-serial проектирование привлекательным и обеспечили быстрое, недорогое проектирование на базе однокристальных процессоров с плавающей точкой, проложили путь очень быстрым микропроцессорам с интегрированными плавающими запятыми и кэш-памятью. Это устранило ценовые преимущества консолидированной последовательной логики, описанной выше, и обеспечило равенство пиковой производительности на более малом числе полных процессоров.

Таким образом, пока существует пользовательский уровень абстракции параллельных операций на больших регулярных структурах данных, продолжается и предложение интересных решений для рассматриваемого важного класса проблем. Машинная организация, поддерживая модели data parallel programming models, развивается по направлению к более общим параллельным архитектурам множественной кооперации микропроцессоров, более масштабируемой разделяемой памяти и MPA машинам, несмотря на то, что существуют решения в области создания специализированных компьютерных сетей, поддерживающие глобальную синхронизацию процессоров. В последнем случае сетевая поддержка выступает в роли барьера, который в особых точках программы переводит каждый процесс в режим ожидания до тех пор, пока остальные процессы, не достигнут заданной точки синхронизации. В действительности SIMD подход эволюционировал в SPMD (single-programm-multiple-data) подход, в котором все процессоры выполняют копии одних и тех же программ и имеют, таким образом, в большей мере схожесть с более структурированными формами разделяемой памяти и МР программирования.

В середине 1980-х возрождение SIMD data parallel machine привело к появлению других архитектурных направлений, которые были исследованы в академических институтах и промышленности, но имели меньший коммерческий успех и поэтому не получили широкого распространения, по сравнению с рассмотренными выше. Два подхода, которые развились до законченных программных систем – dataflow architectures и systolic architectures.