Лектор: Зуев Игорь Станиславович

Разделы iMCS96 (выборочно).

Изложение конспективное. Возможны неточности

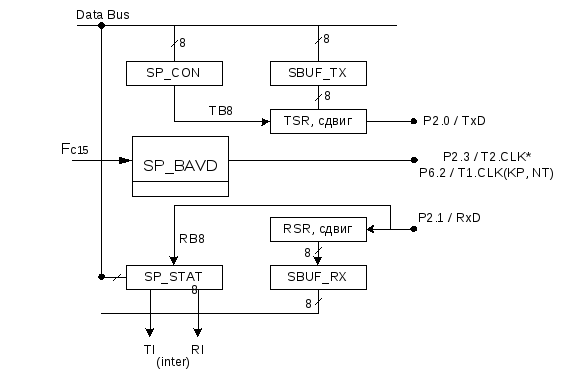

Последовательный порт

Реализует синхронный обмен и асинхронный обмен информации последовательным кодом. Асинхронный обмен выполнен по стандарту UART(UnversalAsynchronousReceiver/Transmitter). Аналогичен 51-ой серии; в дополнении реализован контроль четности / нечетности при передаче информации и блок генерации частоты обмена не использует общие таймеры Т1 и Т2, позволяя воспроизводить частоту более точно. В следующем рисунке есть неточности.

* (BH, KB, KC)

Преобразование параллельного кода в последовательный

Информация передается на вывод TxD (TransmittData), принимается на входе RxD (ReceiveData)

SBUF_TX– при записи,

SBUF_RX– при чтении два разных регистра.

Полнодуплексный режим – запись и чтение могут происходить параллельно

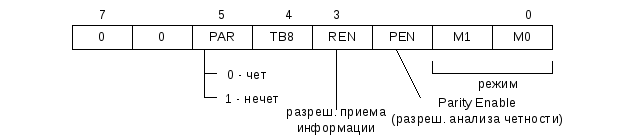

SP_CON

SP_STAT

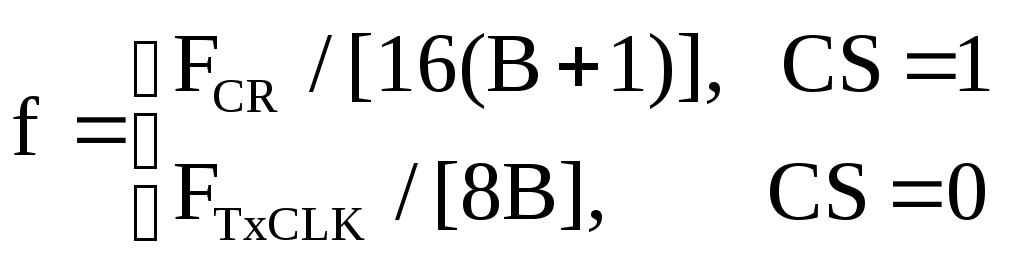

SP_BAVD– регистр частоты

15 бит содержит константу В, 16 старший содержит clockselect

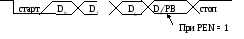

Протокол обмена

Режим «0»– синхронный обмен

Р2.0 – синхронизация, выдает тактовую частоту обмена

Р2.1 – мы имеем данные (входные – выходные; прием – передача)

Данные считаются действительными на фронте тактового сигнала

Передача:

Флаг REN= 0. передача начинается, когда записан байт в регистрSBUF_TX→TSR→P2.1 → →TI= 1 записан байт в регистрSBUF_TX– информация.

Прием:

Флаг REN= 1 иRI= 0 →RSR→SBUF_RX→RI= 1– параллельный прием в последовательном коде.

В режиме 1-3 порт функционирует как асинхронный приемо-передатчик UART.

TxD– передача;RxD– прием могут происходить одновременно. Пока на выводе 1 то, ничего не происходит; передача началась, когда происходит перепад из 1 в 0.

Режим «1»

Кадр 10 битный.

Режим «2» (11-битный кадр)

Режим «3»(11- битный кадр)

У 9го бита еще больше функций

Передача данных

SBUF_TX → TSR→P2.0 →TI= 1

Прием данных

Только если PEN= 1

RSR→SBUF_RX→RI= 1, прерывание, если

Многопроцессорная связь

Многопроцессорная связь главный процессор находится в режиме 3, подчиненные в режиме 2. Алгоритм передачи данных:

1) главный ЦП выдает адрес, при этом ТВ8 = 1.

2) следствием этого является прерывание всех подчиненных процессоров

- анализ адреса.

- перевод адресованного подчиненного процессора в режим 3

3) передача данных, ТВ8 = 0 (прерывается только адресованного подчиненного процессора)

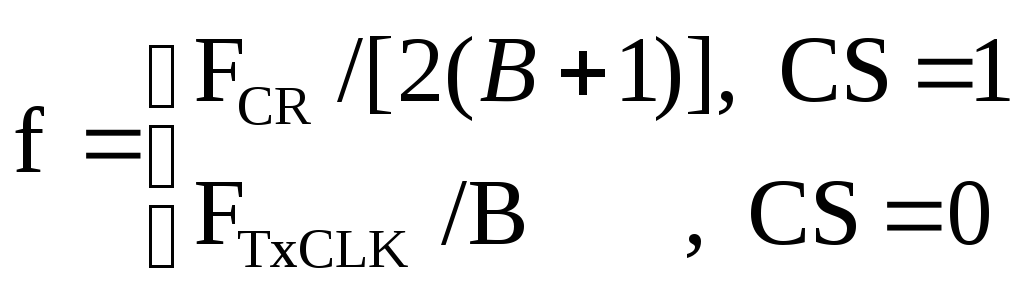

Частота обмена в режимах 1, 2, 3:

Флаги:

TxE= 1 (TxEmpty)TSRвыдан и не поступила информация вSBUF_TX– режим ожидания.

OE= 1 передачаRSR→SBUF_RXзатирает еще не прочитанную информацию.

FE= 1 – (FramingError) – ошибка кадра – возникает, когда при приеме отсутствует стоп бит в ожидаемом месте. При возникновении ошибокOEилиFEвсю информацию необходимо передавать снова.

Контроллер прерываний

Контроллер прерываний может обрабатывать прерывания без перехода к программе

Нужно просто настроить блок

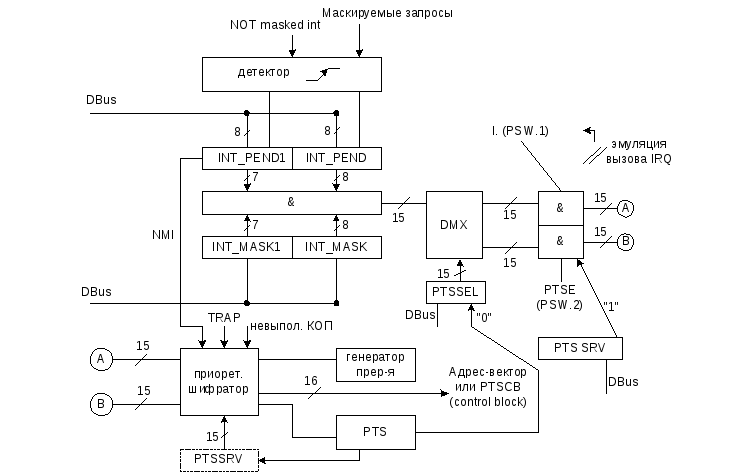

Структура контроллера прерываний

Первый раз нужно сгенерировать прерывание искусственно для этого записать единицу в соответствующий разряд регистра. Естественные прерывания сверху ловит детектор восходящий фронт.

В регистре INT_MASK-разрешение прерываний

ПШ- приоритетный шифратор

В архитектуре регистры разделены на две части, поскольку в начальной серии BH было только 8 запросов на прерывания; 15 запросов являются маскируемыми, то есть любое прерывание, чтобы оно работало, должно быть разрешено. Старший запрос – немаскируемый.

Адрес вектор – есть 16 разрядный адрес перехода на подпрограмму обработки прерываний в данном такте, либо адрес управляющего блока, если обработка прерывания происходит через PTS.

С системой прерывания связаны следующие команды:

PUSHF,POPF– добавка и извлечение флага – заносит в стек регистр -PSW,INTMASK

PUSHA,POPA– заносит в стек регистр -PSW,INTMASKи ещеINTMASK1 иWSR. После выполнения этих команд обнуляются автоматическиPSW,INTMASK,INTMASK1. Данная деталь означает, что

1) все прерывания запрещены каждое в отдельности (так как INTMASKиINTMASK1 равны 0) и запрещены все вместе (так какPSWравно 0).

2) Также позволяется программировать вложенность прерываний. Вложенность прерываний 96 серии: при входе в программу прерываний можно разрешать определенные прерывания, если это необходимо.

Запросы прерывания текущей программы могут поступать от внешних источников или формироваться внутри микроконтроллера в различных периферийных устройствах. Общее число источников запросов прерывания у микроконтроллеров разных типов может быть 21, 28 или 37.

Запросы прерывания могут маскироваться путем посылки кодов маски в соответствующие регистры специальных функций. В микроконтроллерах всех типов имеется программный контроллер прерываний (PIC). Обслуживание запроса прерывания с использованием PIC заключается в переходе от выполнения текущей программы к выполнению другой определенной программы, составленной разработчиком программного обеспечения.

Адрес первой команды каждой прерывающей программы (вектор прерывания) хранится в определенной паре ячеек ПЗУ в области памяти, отведенной для хранения специальных данных. После завершения выполнения прерывающей программы происходит возврат к прерванной программе.

Прерывающая программа в свою очередь может быть прервана при поступлении любого незамаскированного запроса прерывания вне зависимости от соотношения приоритетов запроса, вызвавшего переход к данной программе, и нового запроса прерывания.

В микроконтроллерах некоторых типов кроме программного контроллера прерываний имеется микропрограммный контроллер прерываний (PTS). Любой запрос прерывания, кроме нескольких особых запросов, может быть направлен для обслуживания или в PIC или в PTS. Прерывание обслуживается через PTS, если по соответствующему разряду регистра PTSSEL записана 1.

Обслуживание запроса прерывания с использованием PTS заключается в выполнении типовой микропрограммы, при этом выполнение операций по микропрограмме совмещается во времени с выполнением команд текущей программы или подпрограммы обработки обычного прерывания. Микропрограммы PTS охватывают, в основном, пересылки данных. Прерывания, обслуживаемые PTS, отрабатываются быстрее, чем те, которые обслуживаются обычным способом. Однако, программировать PTS непросто, а отлаживать еще сложнее.

Таблица источников прерывания (источники запросов на прерывание)

|

№ разряда |

RG |

Источники запросов |

Приоритет/адрес вектор: | |

|

IRS |

PTS(KC) | |||

|

0 |

INT_PEND, INT_MASK, PTSEL, 0-7,PTSSRV, 0-7 |

T1 переполнение таймера T2 переполнение таймера |

0/2000h |

15/2040h |

|

1 |

A/D- Аналого-цифровое преобразование завершено |

1/2002 |

16/2042 | |

|

2 |

FIFOполон ( 6 значений, 7ой в резерве) HIS_RG полон |

2/2004 |

17/2044 | |

|

3 |

Любая операция в HSO.0 |

3/2006 |

18/2046 | |

|

4 |

HSI.0 |

4/2008 |

19/2048 | |

|

5 |

Software T0,T1,T2,T3,RESETT2,началоA/D->все вызывают прерывание таймераHS0 |

5/200A |

20/204A | |

|

6 |

TI,RI-> Последовательный порт |

6/200C |

21/204C | |

|

7 |

EXTINT,ACH.7 – внешнее прерывание |

7/200E |

22/204E | |

|

0 |

INT_PEND, INT_MASK1, PTSEL, 8-14,PTSSRV, 8-14 |

TI |

8/2030h |

23/2050h |

|

1 |

RI |

9/2032h |

24/2052h | |

|

2 |

HSI.FIFO 4 |

10/2034 |

25/2054 | |

|

3 |

T2 CAPT |

11/2036 |

26/2056 | |

|

4 |

T2переполнение |

12/2038 |

27/2058 | |

|

5

|

EXTINT1 внешнее прерывание |

13/203А |

28/205А | |

|

6 |

HSI.FIFO – полон |

14/203C |

29/205C | |

|

7 |

NMI не маскированное прерывание |

30/203E |

| |

Возрастание приоритета в таблице от начала к концу!!!