- •Архитектура микроконтроллеров семейства lpc2000

- •Функциональное описание микроконтроллера lpc2148. Обзор архитектуры

- •Описание ядра

- •Режимы работы и регистровые модели arm7tdmi

- •Способы адресации и система команд

- •Типы данных

- •Режимы адресации

- •Система команд

- •Внутренние периферийные устройства

- •Таймеры

- •Задания на лабораторные работы

- •Список литературы

- •Содержание

Режимы работы и регистровые модели arm7tdmi

В состоянии ARM процессор может функционировать в одном из следующих режимов:

User (пользователя)- выполнение программ пользователя.

Supervisor (супервизора)- работа под управлением операционной системы (ОС), которая оперирует данными, недоступными программам пользователя.

System (системный) - режим выполнения системных программ, при котором ОС работает с данными пользователя. Вводить системный режим из другого привилегированного режима возможно только путем изменения бита режима в регистре текущего состояния программы (CPSR).

IRQ (прерывания) - режим обработки прерываний, в который попадает процессор при поступлении запроса прерывания низшего уровня на вход IRQ.

FIQ (Fast IRQ, быстрого прерывания) - режим быстрой реакции на прерывания, в который попадает процессор при поступлении запроса высшего уровня на вход FIQ.

Abort (аварийный) - режим, который реализуется при ошибке обращения к памяти (ошибки такого рода — обращение по несуществующему адресу, попытка записи в ПЗУ и другие, фиксируются контроллером прерываний, который выдаёт процессорному ядру запрос Abort).

Undefined (неопределенный) - режим реализуется при выборке неправильного кода команды.

Все режимы, кроме режима пользователя, совместно называются привилегированными режимами. Привилегированные режимы используются для обслуживания прерываний и исключительных ситуаций, а также для доступа к защищенным ресурсам.

Каждый регистр имеет идентификатор режима (см. табл. 2).

Таблица 2. Идентификаторы режима

|

Режим |

Идентификатор режима |

|

Режим пользователя |

usr |

|

Режим быстрого прерывания |

fiq |

|

Режим прерывания |

irq |

|

Режим супервизора |

svc |

|

Аварийный режим |

abt |

|

Системный режим |

sys |

|

Неопределенный режим |

und |

Процессор ARM7TDMI содержит всего 37 регистров:

31 32-разрядных регистра общего назначения

6 регистров статуса.

Не все регистры доступны в одно и тоже время. Доступность регистров для программиста зависит от состояния процессора и рабочего режима.

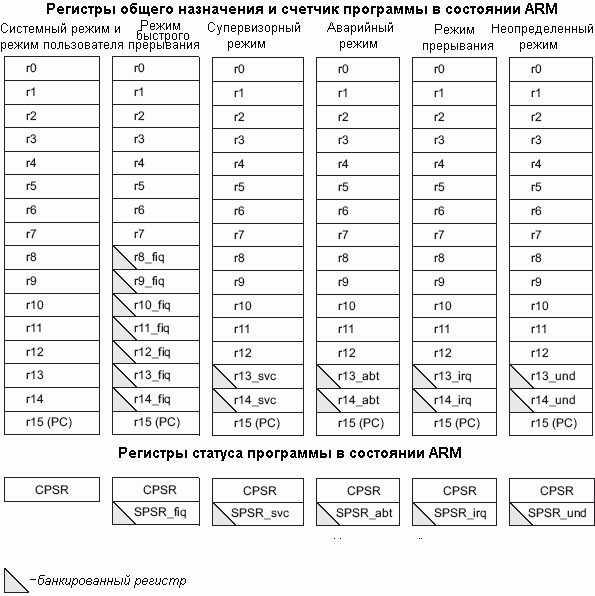

Набор регистров в состоянии ARM

В состоянии ARM доступны 16 регистров общего назначения, один или два регистра статуса. В привилегированных режимах становятся доступными специфические банки регистров. На рис. 3 демонстрируется, какие регистры доступны в каждом режиме.

В набор регистров в состоянии ARM входят 16 регистров r0...r15. Еще один регистр, CPSR (Current Programm Status Register) - регистр текущего состояния программы), содержит флаги условия кода и биты текущего режима.

Регистры r0...r12 являются регистрами общего назначения и могут использоваться как для хранения данных, так и для хранения адреса. Регистры r13 – r15 выполняют следующие специальные функции:

Регистр связи

Регистр r14 используется как регистр связи (LR – Link Register) подпрограммы: r14 принимает копию регистра r15 при выполнении инструкции переход по ссылке.

Во всех остальных случаях регистр r14 может использоваться как регистр общего назначения. Соответствующие банкированные регистры (т.е. регистры, которые имееют свои копиии во всех режимах работы микроконторллера, см. рис. 3) r14_svc, r14_irq, r14_fiq, r14_abt и r14_und аналогичным образом используются для запоминания значений возврата r15 при возникновении прерываний и исключительных ситуаций или при выполнении инструкции BL внутри процедур обработки прерываний или исключительных ситуаций.

Счетчик программы

Регистр 15 хранит значение PC (Programm Counter).

В состоянии ARM биты [1:0] регистра r15 имеют неопределенное значение и должны игнорироваться. Биты [31:2] содержат значение PC.

В состоянии Thumb бит [0] имеет неопределенное значение и должен игнорироваться. Биты [31:1] содержат значение PC.

Регистр r13 iиспользуется в качестве указателя стека (SP).

В привилегированных режимах доступен еще один регистр - регистр хранения статуса программы (SPSR – Saved Programm Status Register). Он содержит флаги кода условия и биты режима, являющиеся результатом исключительной ситуации, которое вызвало вхождение в текущий режим.

Банки регистров - дискретные физические регистры в ядре, которые находятся в позициях доступных регистров в зависимости от текущего рабочего режима процессора. Содержимое банкированного регистра запоминается при изменениях рабочих режимов.

В режиме FIQ имеется семь банкированных регистров в позициях r8-r14 (r8_fiq-r14_fiq).

В состоянии ARM несколько обработчиков быстрых прерываний (FIQ) не должны выполнять запись в какой-либо регистр.

В режимах пользователя, IRQ, супервизорном, аварийном и неопределенном имеется два банкированных регистра в позиции r13 и r14, позволяя хранить собственное значение SP и LR в каждом режиме.

В системном режиме используются те же регистры, что и в режиме пользователя.

Рис. 3. Регистровые модели процессора в состоянии ARM

В базовом режиме User, в котором процессор работает основную часть времени, используются 32-разрядные регистры R0-R15 и регистр состояния CPSR. Регистр R15 выполняет функции программного счётчика PC. Регистр R14 (LR - Link Register) используется при вызовах подпрограмм как регистр связи, в котором сохраняется текущее содержимое PC для возвращения к основной программе. Для организации стека рекомендуется использовать регистр R13 (SP - Stack Pointer) в качестве указателя стека.

Все регистры имеют дополнительные имена, определённые стандартом фирмы ARM [2]. Этот документ регламентирует использование регистров при вызове подпрограмм и организации передачи данных между ними и предназначен, главным образом, для разработчиков компиляторов:

Регистры a1 - a4 (argument 1 – 4) используются для передачи параметров подпрограммам.

Регистры v1 - v8 (variable 1 - 8) используются для хранения локальных переменных.

Регистр IP (Intra-Procedure-call scratch register) - служит для хранения промежуточных данных между вызовами процедур.

Набор регистров в состоянии Thumb является поднабором по отношению к набору регистров в состоянии ARM. Программист имеет доступ к:

8 регистрам общего назначения r0-r7

Счетчику программ PC

Указателю стека SP

Регистру связи LR

Регистру текущего состояния программы CPSR.

В каждом привилегированном режиме имеются банкированные регистры SP, LR и SPSR

Соотношение между регистрами в состояниях ARM и Thumb

Регистры в состоянии Thumb связаны с регистрами в состоянии ARM следующим образом (рис. 4):

Регистры r0-r7 в состоянии Thumb и регистры r0-r7 в состоянии ARM идентичны

Регистры CPSR и SPSR в состоянии Thumb и регистры CPSR и SPSR в состоянии ARM идентичны

Указатель стека SP в режиме Thumb совпадает с позицией r13 в состоянии ARM

Регистр связи LR в режиме Thumb совпадает с позицией r14 в состоянии ARM

Счетчика программы PC в режиме Thumb совпадает с положением счетчика программы PC в состоянии ARM (r15).

Рис.

4. Расположение регистров в состояниях

Thumb и ARM

Рис.

4. Расположение регистров в состояниях

Thumb и ARM

Доступ к старшим регистрам в состоянии Thumb

В состоянии Thumb старшие регистры r8-r15 не являются частью стандартного набора регистров. Программисту на языке Ассемблер ограничивается доступ к ним, но их можно использовать для кратковременного хранения.

Можно использовать специальные варианты инструкции MOV для передачи значений из младших регистров r0-r7 в старшие и, наоборот, из старших регистров в младшие. Инструкция CMP позволяет сравнивать значения старших регистров со значениями младших регистров, а инструкция ADD позволяет сложить значения старших регистров со значениями младших регистров.

Регистр состояния CPSR

Рис.

5 Формат регистра CPSR

Рис.

5 Формат регистра CPSR

M4-0 - определяют режим работы процессора в соответствии с табл. 2;

T - задаёт состояние процессора: ARM (при T = 0) или THUMB (при T = 1);

I, F - маскируют (запрещают обработку) прерываний IRQ и FIQ;

N, Z, C, V - являются признаками знака (N), нуля (Z), переноса (С) и переполнения (V), значения которых устанавливаются в соответствии с результатом очередной операции.

Таблица 3. Режимы процессора

|

M4-0 |

Режим |

|

1 0 0 0 0 |

User |

|

1 0 0 0 1 |

FIQ |

|

1 0 0 1 0 |

IRQ |

|

1 0 0 1 1 |

Supervisor |

|

1 0 1 1 1 |

Abort |

|

1 1 0 1 1 |

Undefined |

|

1 1 1 1 1 |

System |

Запись нового содержимого в регистр CPSR возможна во всех режимах, кроме User. Эти режимы называются привилегированными.

При запуске процессор начинает работу в режиме Supervisor. Переход в режим User реализуется путём записи в регистр CSPR содержимого, в котором биты M4-0 = 10000. Обратное переключение из режима User в Supervisor производится только при поступлении команды программного прерывания SWI. Таким образом обеспечивается доступ пользователя к ресурсам операционной системы. Программа Supervisor получает доступ ко всем регистрам модели User, если выполнит переход в режим System, записав в регистр СPSR значение битов M4-0 = 11111. Переход в режимы IRQ, FIQ, Abort, Undefinied осуществляется автоматически при поступлении соответствующих запросов или событий.

При переходе в другой режим текущее содержимое регистра CPSR (слово состояния) переписывается в регистр SPSR, соответствующий наступившему режиму. При возвращении к исходному режиму содержимое CPSR восстанавливается.

Для каждого режима имеются отдельные регистры R13 (SP), R14 (LR). Поэтому при переключении режимов сохраняется текущее содержимое указателя стека и регистра связи. Таким образом при возвращении к данному режиму обеспечивается обращение к вершине стека и возможность возврата к основной программе, если производился вызов подпрограммы.

При переходе в режим FIQ (поступление запроса прерывания на вход FIQ) сохраняется текущее содержимое регистров R8-R12, вместо которых в этом режиме используются регистры R8_fiq - R12_fiq (рис. 3). Поэтому при обработке данного прерывания нет необходимости сохранять содержимое этих регистров в стеке. В ряде случаев это обеспечивает более быстрый переход к обработчику прерываний и возврат из него.