- •Команды (директивы) управления программой «Монитор»

- •Директивы работы с памятью

- •Директивы работы с регистрами

- •Способы адресации

- •Выполнение на ассемблере последовательных алгоритмов с различными способами адресации при выполнении арифметических операций

- •Реализация ветвящихся процессов. Команды условных переходов

- •Команды для переходов учебного компьютера

- •Синтаксис команд безусловного перехода

- •Реализация на ассемблере циклических программ

- •Анализ и синтез комбинационных схем

- •Понятие основных (базовых) и базисных функций двух переменных

- •Построение одноразрядного полного сумматора

- •Формальный синтез полного одноразрядного сумматора на основе булевой алгебры

- •Разорванные группы

- •Формы представления чисел

- •Примеры представления чисел с фиксированной точкой в формате sfix()

- •Достоинства и недостатки представления чисел с фиксированной точкой

- •Представление данных в форме с плавающей точкой

- •Видоизменённая (современная) форма представления чисел с плавающей точкой

- •Особенности микроконтроллеров семейства avr atmel

- •Адресное пространство мк avr (распределение памяти)

- •Регистр состояния, регистр флагов.

- •Системы команд процессоров atmel

Видоизменённая (современная) форма представления чисел с плавающей точкой

Fixed Point Block Set (FPBS) поддерживает IEEE стандарт представления чисел с плавающей точкой.

IEEE стандарт используют практически все процессоры и арифметические сопроцессоры, а также высокоуровневые сигнальные процессоры (DSP)/

Отличительная особенность IEEE стандарта от формы (9) заключается в следующем: число в памяти хранится всегда с нормализованной мантиссой. По этой причине старшую единицу мантиссы можно и не хранить. Это экономит 1 бит и, следовательно, увеличивает диапазон представимых чисел. Эта единица присутствует неявно и называется неявной единицей (implicit). Отбрасывание старшей цифры мантиссы выполняется для двух форматов: single и double. Такая форма представления мантиссы обозначается 1.f.

Порядок

числа

![]() хранится «сдвинутым», то есть к нему

прибавляется фиксированное число (биас)

так, чтобы порядок всегда был

неотрицательным. Для чисел форматаsingle

прибавляется 127. Для чисел формата double

1023.

Всегда неотрицальный порядок избавляет

от необходимости выделять 1 бит для

хранения знака порядка и упрощает

выполнение операций сравнения порядков

и арифметических операций над ними.

хранится «сдвинутым», то есть к нему

прибавляется фиксированное число (биас)

так, чтобы порядок всегда был

неотрицательным. Для чисел форматаsingle

прибавляется 127. Для чисел формата double

1023.

Всегда неотрицальный порядок избавляет

от необходимости выделять 1 бит для

хранения знака порядка и упрощает

выполнение операций сравнения порядков

и арифметических операций над ними.

Распределение разрядов машинного слова в формате single IEEE.

-

sign

…

…

знак мантиссы

порядок

мантисса (без неявной единицы)

Истинное значение соответствующее формату single будет представлено в виде:

![]() ,

,

![]()

Пример

1. Задано

число

![]()

![]() (11

– 3 в двоичной форме)

(11

– 3 в двоичной форме)

Учитывая отбрасывание неявной единицы и сдвиг порядка, получаем внутреннее представление числа.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Пример

2. Задано

число

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Пример

3. Задано

число

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

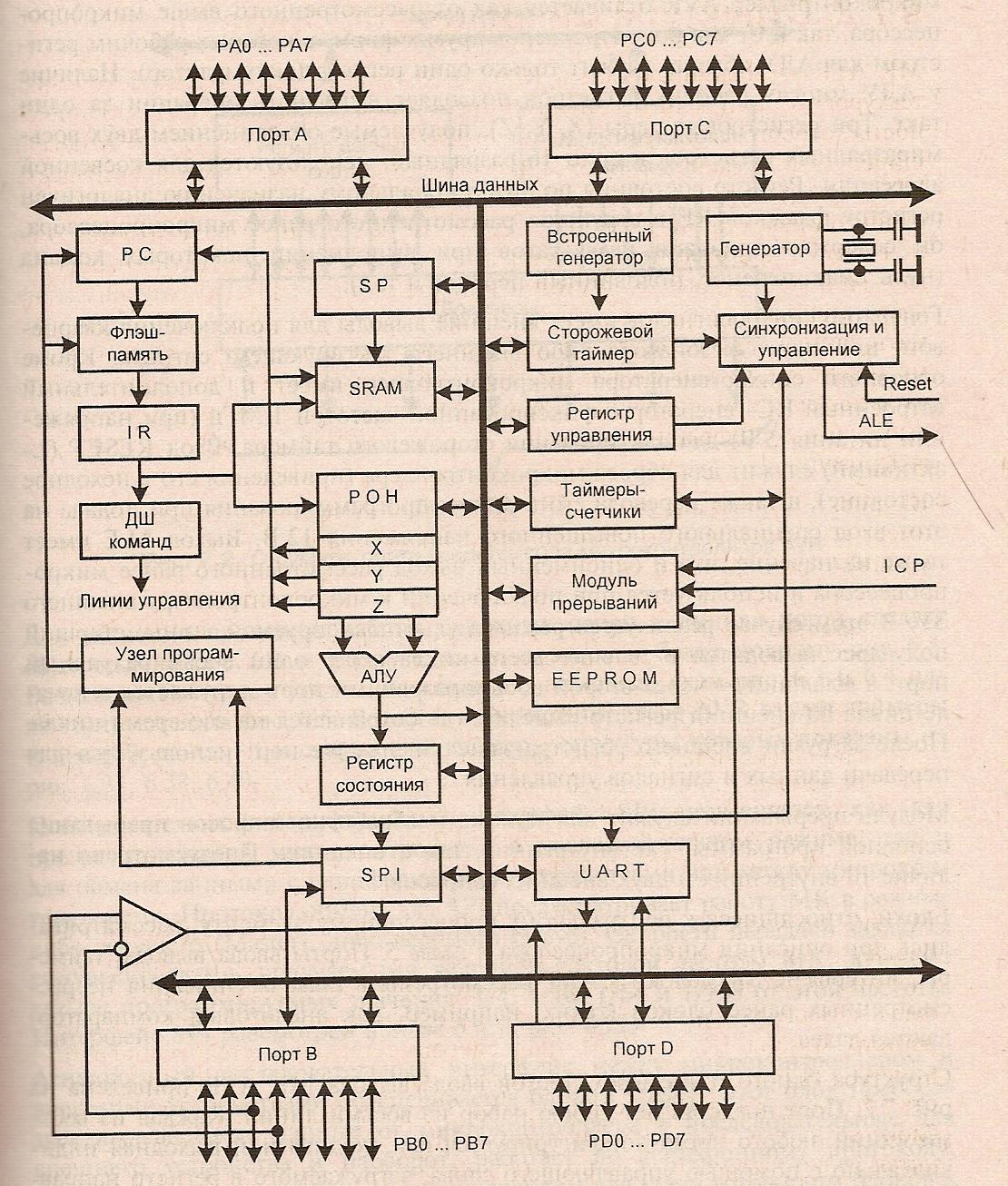

Особенности микроконтроллеров семейства avr atmel

Микроконтроллеры (МК) AVR представляют собой восьмиразрядную однокристальную микро-ЭВМ с упрощенной (сокращённой) системой команд RISC (Restricted (Reduced) Instruction Set Computer). Большинство команд, входящих в систему команд, выбирается из памяти программ и выполняются за один такт работы МК. При выполнении последовательности команд выборка из памяти очередной команды совмещается во времени с исполнением ранее выбранной команды. В состав семейства AVR входят МК трёх серий: ATiny, ATmega, AClassic.

Рассмотрим структурную схему МК семейства AVR.

PC – программный счётчик, хранит адрес текущей команды.

IR – регистр команд для хранения текущей команды.

ДШ – дешифратор.

SP – указатель стека (регистр специального назначения).

SRAM – оперативная память (статическая).

POH – регистр общего назначения.

EEEROM – электрическая перепрограммируемая память.

ALE – сигнал разрешения прерывания.

UART – универсальный асинхронный приёмо-передатчик.

Адресное пространство мк avr (распределение памяти)

Адресное пространство можно разделить на 2 части: память данных и память программ.

Регистр состояния, регистр флагов.

При выполнении арифметических и логических операций, кроме кода результата, формируются значения признаков результата.

Замечание. Команды пересылок (в учебном компьютере MOV и MOV1) не влияют на значения битов регистра состояния.

При выполнении операций сравнения (=, ≠, .>, < и др.) формируются только значения признаков результата (положительный, отрицательный, равный нулю, не равный нулю и др.)

Значения признаков результата представлены состоянием шести разрядов регистра состояния (SREG).

-

H

S

V

N

Z

С

SREG.0 – Carry flag (флаг переноса)

SREG.1 – Zero flag (флаг нуля)

SREG.2 – Negative flag (отображает значение старшего разряда результата выполнения арифметической или логической операции. Когда не возникает переполнение разрядной сетки: N=0 – положительное число, N=1 - отрицательное число).

SREG.3 – Overflow flag (фиксирует переполнение значения полученного результата).

SREG.4

– Sign

flag (![]() )

)

SREG.5 – Half Carry (половинный перенос)

Пример

1. Сложение

чисел без знака

![]()

-

I

T

H

S

V

N

Z

С

0

0

0

1

0

1

0

0

Пример

2. Сложение

чисел со знаком

![]()

-

I

T

H

S

V

N

Z

С

0

0

1

0

0

0

0

0

Пример

3.

Сложение знаковых чисел

![]()

-

I

T

H

S

V

N

Z

С

0

0

1

0

1

1

0

0

Пример

4. Сложение

знаковых чисел

![]()

-

I

T

H

S

V

N

Z

С

0

0

1

1

0

1

0

1