- •Микросхемное решение логических уравнений

- •Содержание работы.

- •Порядок выполнения работы.

- •Методика выполнения работы.

- •Исходные данные.

- •Упрощение вида уравнения.

- •Разработка диаграммы состояния.

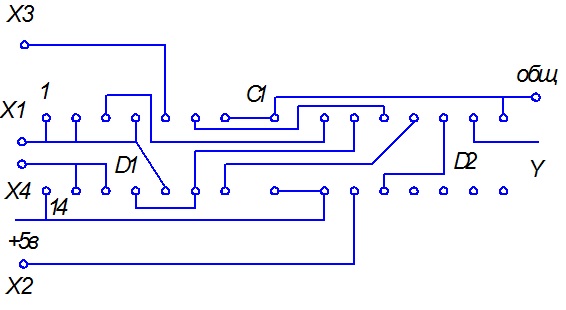

- •Разработка принципиальной схемы.

- •Проверка принципиальной схемы.

- •Разработка печатной платы.

- •Комплектация узла.

- •Проверка правильности работы схемы.

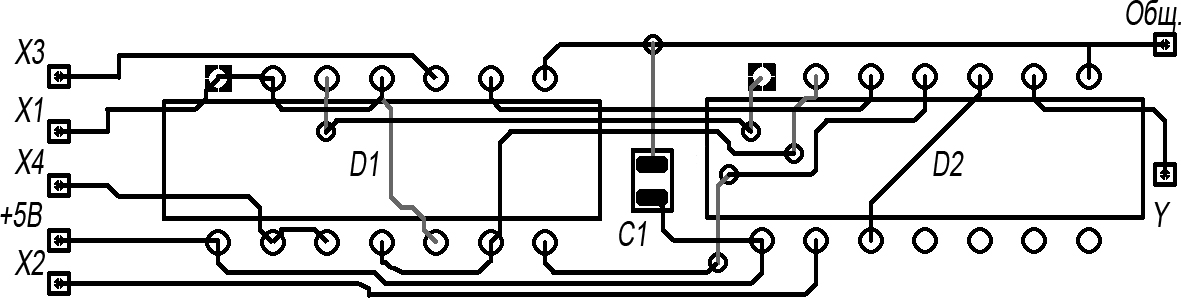

Разработка печатной платы.

Печатная плата для монтажа узла разрабатывается на ПК с использованием соответствующего программного обеспечения, например, PCAD, Ultiboard. Допускается разработка платы вручную, если количество микросхем (МС) в узле невелико, при этом необходимо придерживаться следующих основных требований:

минимальная длина соединительных проводников,

минимальное количество точек соединения,

максимально использовать все элементы, расположенные в корпусе МС,

по возможности применять односторонний печатный монтаж,

при разводке вручную выдерживать масштаб чертежа платы.

В нашем случае используется две микросхемы, следовательно, число соединений невелико, поэтому плату можно разработать вручную. Основное число соединительных проводников желательно размещать на стороне платы, противоположной стороне установки микросхем. При двустороннем печатном монтаже удобно вычерчивать рисунки обоих сторон на одном чертеже с выделением рисунка одной стороны с помощью цвета или типа линий. Рисунок печатной платы для нашего случая имеет вид:

Рис.5. Схема печатной платы.

Рис.5. Схема печатной платы, разработанная в среде Ultiboard.

В процессе разработки печатной платы допускается изменение принципиальной схемы с целью получения более простой разводки печатного монтажа, как то:

замена контактов микросхемы в пределах одного логического элемента,

замена логического элемента на однотипный в пределах данной микросхемы или другой микросхемы.

Комплектация узла.

Разработанный узел комплектуется микросхемами в соответствии с перечнем элементов по принципиальной схеме. Допускается комплектование узла демонтированными микросхемами. В этом случае микросхемы должны быть проверены на специальном стенде.

Проверка правильности работы схемы.

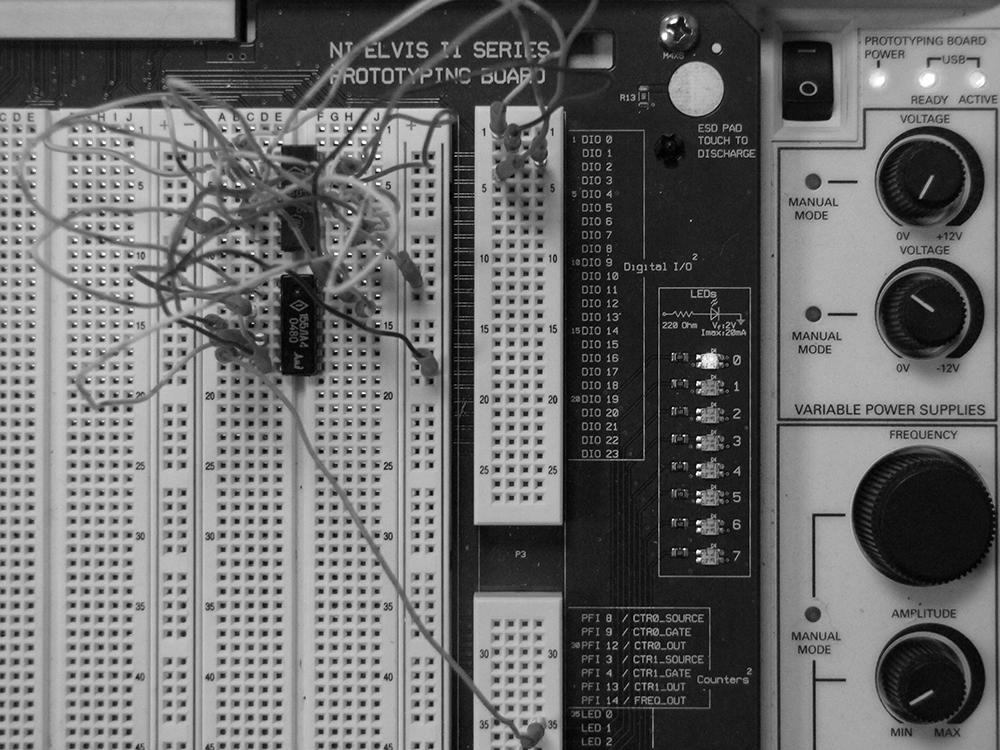

Для проверки собранной схемы ее входы X1…X4 и выход Y подключаются к специальным разъёмам на макетной плате NI ELVIS II (Рис.6).

Рис.6 Схема на макетной плате NI ELVIS II с подключенными входами и выходом.

Входы X1…X4 соединяются со специальными разъемами цифрового ввода/вывода Digital I/O <0-23> (8-битным параллельным цифровым линиям), расположенным справа сверху на макетной плате NI ELVIS II. Выход Y подключается к одному из контактных разъемов с названием User Configurable I/O LED <0-7> (разъемы зелёных светодиодов, которые могут быть использованы, как индикаторы цифровых логических состояний (горит-HI или выключен-LO)).

Примечание: Чтобы светодиод загорелся зеленым, нужно подать +5 В, если подать –5 В, то он будет гореть желтым.

Выполнив необходимые подключения входов/выхода схемы и включив питание макетной платы, снимают диаграмму состояния. Для этого с помощью устройства записи цифровых данных (Digital Writer) задают значения аргументов и по состоянию светодиода контролируют значение функции. Результаты эксперимента должны точно соответствовать таблице 3. При несоответствии диаграммы хотя бы по одной комбинации аргументов проверяется правильность сборки схемы и исправность микросхем с использование дополнительных приборов: цифрового мультиметра (DMM), осциллографа (Scope).

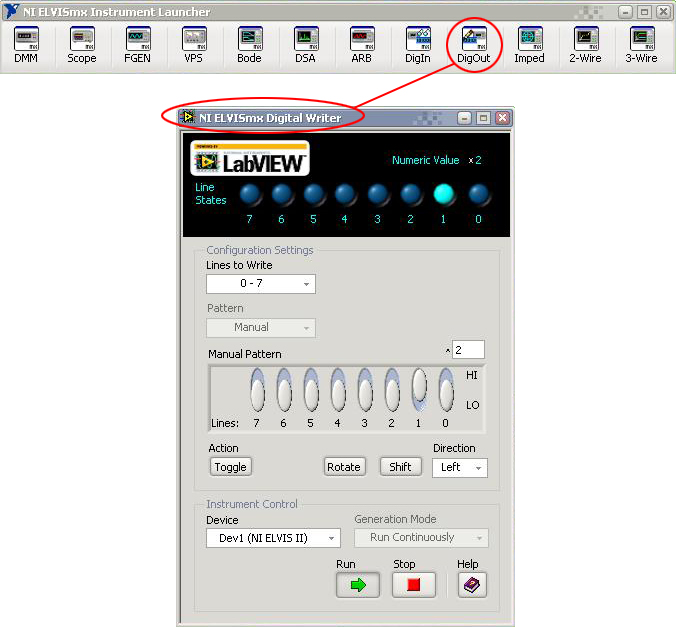

Работа с устройством записи цифровых данных (Digital Writer).

Этот прибор выдает на цифровые линии NI ELVIS II Digital I/O <0-23> определенный пользователем шаблон цифрового сигнала. Шаблон можно создать вручную, а можно выбрать из определенных ранее, таких как "пила", "шахматная доска" или тест "бегущая единица". Прибор может управлять восьмерками линий (портами <0-7>, <8-15>, <16-23>), осуществляя вывод в непрерывном или однократном режиме. Состояние выходов этого устройства не изменяются до тех пор, пока не будет подан следующий шаблон, пока не будут сконфигурированы на чтение используемые линии, или пока не будет отключено питание рабочей станции. Выходные уровни сигналов цифровых линий NI ELVIS II совместимы с уровнями ТТЛ-элементов.

Примечание: Запускается этот прибор выбором в меню Пуск»Все программы»National Instruments»NI ELVISmx»NI ELVISmx Instrument Launcher» DigOut.

Лицевая панель виртуального прибора вывода цифровых сигналов NI ELVISmx Digital Writer показана на Рис7.

Рис.7

Виртуальный прибор позволяет осуществлять диагностику цифровых линий и выставлять любой из 8-битов в положение либо логической единицы (HI), либо логического нуля (LO).

Цифровые линии (Lines) или биты, обозначенные 0-7, считываются справа налево в поле Manual Pattern. Любой бит может быть выставлен в состояние логической 1 или 0 (HI/LO) с помощью нажатия на верхнюю или нижнюю часть элемента управления в виде переключателя.

В поле выбора линии для записи (Lines to Write) в выпадающем меню можно поменять порт из 8-ми цифровых линий на другой, (порт 0: линии 0-7; порт 1: линии 8-15; порт 2: линии 16-23). В поле шаблона (Pattern) указывается последовательность логических единиц и нулей для вывода их по цифровым линиям DIO <0-7>. По умолчанию стоит ручной режим выбора последовательности (Manual).

Как только цифровой паттерн байта установлен в поле Manual Pattern, нажимайте на Run, чтобы послать этот паттерн по цифровым линиям DIO <0-7>.

Примечание: Настройки поля Generation Mode определяет способ записи созданного 8-битного значения в цифровые линии.

При использовании режима Generation Mode -> Run Continuously байт информации посылается в цифровой порт непрерывно с определённой внутренней частотой NI ELVIS II. При этом любые изменения, в том числе и логические операции, мгновенно выводятся в цифровой порт. В режиме Generation Mode -> Run Once при нажатии на кнопку Run байт информации посылается по цифровой линии один раз, после этого виртуальный прибор NI ELVISmx Digital Writer переходит в режим ожидания.

Приложение 1.

Список имеющихся в наличии микросхем для выполнения работы:

Микросхема |

Краткое описание |

Цоколевка |

Зарубежный аналог |

К155 ЛА1 |

(4И-НЕ)×2 |

|

SN7420N |

К155 ЛА2 |

(8И-НЕ)×1 |

|

SN7430N |

К155 ЛА3 |

(2И-НЕ)×4 |

|

SN7400N |

К155 ЛА4 |

(3И-НЕ)×3 |

|

SN7410N |

К155 ЛА6 |

(4И-НЕ)×2 |

|

SN7440N |

К155 ЛА7 |

(4И-НЕ)×2 |

|

SN7422N |

К155 ЛА8 |

(2И-НЕ)×4 |

|

SN7401N |

К155 ЛР1 |

2x2-2И-2ИЛИ-НЕ (один расширяемый по ИЛИ) |

|

SN7450N |

К155 ЛР3 |

2-2-2-3И-4ИЛИ-НЕ с возможностью расширения по ИЛИ |

|

SN7453N |

К155 ЛП5 |

(2искл.ИЛИ)×4 |

|

SN7486N |

К155 ЛН1 |

(НЕ)×6 |

|

SN7404N |

К155 ЛИ1 |

(2И)×4 |

|

SN7408N |

К155 ЛЕ1 |

(2ИЛИ-НЕ)×4 |

|

SN7402N |

Приложение 2.

Перечень вариантов логических уравнений: