- •1Практичне заняття № 1 Дискретні сигнали. Основні положення алгебри логіки. Логічні елементи

- •Основні теоретичні відомості

- •Завдання для самостійної підготовки

- •Завдання на практичне заняття Контрольні запитання

- •2Практичне заняття № 2 Схемотехніка логічних елементів

- •Основні теоретичні відомості

- •Завдання для самостійної підготовки

- •Завдання на практичне заняття Контрольні запитання

- •4Практичне заняття № 4 Шифратори, дешифратори, Мультиплексори і демультиплексори

- •Основні теоретичні відомості

- •Завдання для самостійної підготовки

- •Завдання на практичне заняття Контрольні запитання

- •5Практичне заняття № 5 Тригери. Регістри

- •Завдання для самостійної підготовки

- •Завдання на практичне заняття Контрольні запитання

- •6Практичне заняття № 6 Лічильники

- •Завдання для самостійної підготовки

- •Завдання на практичне заняття

- •Контрольні запитання

- •7Практичне заняття № 7 Пристрої пам’яті

- •Основні теоретичні відомості

- •Завдання для самостійної підготовки

- •Завдання на практичне заняття

- •Контрольні запитання

- •8Практичне заняття № 8 Цифро-аналогові та аналого-цифрові перетворювачі

- •Основні теоретичні відомості

- •Завдання для самостійної підготовки

- •Завдання на практичне заняття

- •Контрольні запитання

- •Перелік рекомендованих джерел

- •Додаток 1

Завдання для самостійної підготовки

Засвоїти теоретичний матеріал згідно з такими питаннями.

Цифрові сигнали та їх параметри. Види цифрових сигналів.

Основні положення булевої алгебри. Основні закони алгебри логіки.

Синтез схем цифрових пристроїв. Досконала диз’юнктивна нормальна форма і досконала кон’юнктивна нормальна форма запису формули роботи цифрового пристрою. Правила їх утворення. Методи мінімізації булевих функцій. Використання принципу двоїстості в синтезі схеми цифрового пристрою.

Логічні елементи. Реалізація схем цифрових пристроїв з використанням логічних елементів.

Завдання на практичне заняття Контрольні запитання

Які існують цифрові сигнали? Навести основні параметри цифрових сигналів.

Перерахуйте основні логічні операції булевої алгебри.

Які є формули перетворення функцій в булевій алгебрі?

В чому полягає синтез цифрових пристроїв?

Пояснити правила утворення досконалих диз’юнктивних і кон’юнктивних нормальних форм запису формули роботи цифрового пристрою.

Які існують методи мінімізації булевих функцій?

Які цифрові елементи реалізують основні логічні операції? Наведіть приклади схем цифрових пристроїв на логічних елементах.

2Практичне заняття № 2 Схемотехніка логічних елементів

МЕТА ЗАНЯТТЯ: практично засвоїти схемотехніку логічних елементів

ТРИВАЛІСТЬ ЗАНЯТТЯ: 2 ауд. год.

Основні теоретичні відомості

Логічні елементи (ЛЕ) в інтегральних мікросхемах (ІМС) виготовляють на базі напівпровідникових транзисторів і діодів. Класифікують ЛЕ в основному за типом цих елементів і зв’язків між ними. ЛЕ розподіляють на: діодні ЛЕ (ДЛ), діодно-транзисторні ЛЕ (ДТЛ), транзисторно-транзисторні ЛЕ (ТТЛ), емітерно-зв’язані ЛЕ (ЕЗЛ), ЛЕ на польових транзисторах (МДНЛ), ЛЕ з інжекційним живленням (ІЖЛ). Найбільше розповсюдження на даний час мають останні чотири типи логічних елементів. Тому розглянемо принцип побудови і роботи тільки цих ЛЕ.

Основними параметрами ЛЕ є: статична характеристика передачі, рівні напруг лог. 0 та лог. 1 на вході і виході ЛЕ, значення перепаду напруг лог. 0 та лог. 1 на виході, порогові рівні напруг лог. 0 та лог. 1, коефіцієнт об’єднання за входом, коефіцієнт розгалуження за виходом, допустима напруга статичної завади, середня затримка розповсюдження, споживана потужність, робота перемикання.

Транзисторно-транзисторні логічні елементи (рис. 2 .3) виготовляють тільки зі складним інвертором. Мета його застосування полягає в тому, щоб зробити вихідний опір елемента малим як в стані лог. 0 так й у стані лог. 1.

На вході схеми встановлено багатоемітерний транзистор VТб, розроблений спеціально для застосування в ЛЕ ТТЛ. Кількість емітерів цього транзистора визначає кількість входів ЛЕ. Складний інвертор утворюють транзистори VT1–VT3 і діод зміщення VDзм.

Розглянемо роботу елемента на рис. 2 .3. Якщо на всі входи транзистора VТб подано лог. 1, то емітерні переходи будуть закриті, а колекторний перехід — відкритий, тоді багатоемітерний транзистор працюватиме в активному інверсному режимі: емітери працюють як колектор, а колектор - як емітери. Тоді буде протікати струм по колу +Ek, резистор R0, база-колектор транзистора VТб, база-емітер транзистора VT1, резистор Rе, –Ek. Транзистори VT1 і VT3 перебувають в насиченому стані. Транзистор VT2 при цьому буде в стані відсічки. Це забезпечується наявністю діода зміщення VDзм. В такому випадку напруга на виході ЛЕ є малою і відповідає напрузі лог. 0.

Рисунок 2.3 – Схемотехніка елементів ТТЛ

Якщо на один або декілька входів ЛЕ подано лог. 0, то відповідні емітерні переходи транзистора VТб будуть відкриті. Багатоемітерний транзистор VТб тоді перебуває в режимі прямого підключення і знаходиться в стані насичення, напруга на його колекторі відносно корпусу мала і транзистори VT1 і VT3 будуть в стані відсічки. Високий потенціал колектора VT1 забезпечить переведення транзистора VT2 у стан насичення. В такому випадку напруга на виході ЛЕ є високою і відповідає напрузі лог. 1.

Описаний вище елемент є ЛЕ І-НЕ. З метою реалізації функції логічного додавання у вказаний елемент добавляють вузол розширення по АБО (елементи обведені пунктирною лінією на рис. 2 .3).

Швидкодія ЛЕ обмежується інерційністю транзисторів і процесами зарядження і розрядження ємностей навантаження і паразитних ємностей транзисторів схеми. У різних серіях ІМС швидкодія ТТЛ-елементів характеризується значенням середньої затримки розповсюдження від 10 до 50 нс.

Застосування діодів і транзисторів Шоттки в ТТЛ-елементах дозволяє підвищити швидкодію роботи цих ЛЕ без збільшення споживаної потужності або знизити споживану потужність збільшенням опору всіх резисторів без зниження швидкодії. ТТЛ-елементи з діодами і транзисторами Шоттки називають ТТЛШ-елементами.

Спрощену схему логічного елемента ЕЗЛ показано на рис. 2 .4. Схема містить перемикач струму, який складається з паралельно підключено трьох транзисторів VT1(1), VT1(2), VT1(3), на які подаються вхідні сигнали керування х1, х2, x3, а також емітерні повторювані на транзисторах VT3 і VT4.

Емітерний струм Iе протікає через ліве або праве плече перемикача і визначається в основному значенням опору Rе обраного достатньо великим. Тому значення струму Iе під час проходження його через ліве плече мало залежить від того, чи відкритий один із транзисторів VT1, два з них або всі три. Тому достатньо подати сигнал лог. 1 на один із входів, наприклад х1=1, як ліве плече відкривається, а транзистор VT2 закривається. При цьому вихідні сигнали будуть y1=0, y2=1. І тільки при х1=х2=х3=0 струм із лівого плеча перемикається в праве і на виходах буде у1=1, у2=0.

Отже, цей тривходовий ЛЕ по одному виходу виконує операцію АБО-НЕ

![]() ,

,

а по іншому — операцію АБО

![]() .

.

Рисунок 2.4 – Логічний елемент ЕЗЛ

В основі ЛЕ на польових транзисторах лежать КМДН‑транзисторні ключі, утворені двома МДН‑транзисторами різного типу провідності (рис. 2 .5).

Логічний елемент АБО-НЕ реалізується за допомогою двох КМДН-ключів шляхом паралельного вмикання n‑канальних транзисторів і послідовного вмикання p‑канальних транзисторів. На рис. 2 .5, а зображено електричну схему двовходового елемента АБО-НЕ.

Якщо на входи подано напруги низьких рівнів, тобто х1=х2=0, то транзистори VT1(1) і VT1(2) закриті, а транзистори VT2(1) і VT2(2) відкриті. Тоді напруга на виході буде високого рівня у=1.

З подачею лог. 1 хоча б на один із входів (наприклад, х1=1) транзистор VT1(1) відкривається, а транзистор VT1(2) закривається. Напруга на виході буде низького рівня у=0.

Логічний елемент І-НЕ будують аналогічно, тільки p‑канальні транзистори підключають паралельно, а n-канальні — послідовно (рис. 2 .5, б).

Якщо х1=х2=1, то транзистори VT1(1) і VT1(2) відкриті, а VT2(1) і VT2(2) закриті. Напруга на виході близька до нуля, тобто у=0. Коли хоча б на один вхід подано лог. 0, наприклад, х1=0, то транзистор VT1(1) закривається, а VT2(1) відкривається. При цьому напруга на виході буде високого рівня у=1.

а) б)

а — ЛЕ АБО-НЕ; б — ЛЕ І-НЕ

Рисунок 2.5 – ЛЕ на польових транзисторах

Головна перевага КМДН ЛЕ полягає у малій потужності споживання енергії від джерела струму в статичному режимі. Але ЛЕ КМДН належать до елементів низької швидкодії, з частотою перемикання не більше 5 МГц.

ЛЕ з інжекційним живленням (І2Л). Спрощена схема таких ЛЕ показана на рис. 2 .6.

а) б)

в) г)

а — ЛЕ АБО-НЕ, б — ЛЕ АБО, в — ЛЕ І, г — ЛЕ І-НЕ

Рисунок 2.6 – ЛЕ І2Л

Елементи І2Л відрізняються дуже малою споживаною потужністю і великою швидкодією. ІМС на базі ЛЕ І2Л виготовлюють з високим рівнем інтеграції. Тому ЛЕ І2Л переважно використовують для створення мікропроцесорів.

Завдання для самостійної підготовки

Засвоїти теоретичний матеріал згідно з такими питаннями.

Класифікація логічних елементів залежно від типу логіки.

Основні параметри логічних елементів.

Схемотехніка ЛЕ ТТЛ, ЕЗЛ, КМДН, І2Л.

Завдання на практичне заняття

Контрольні запитання

Яка класифікація ЛЕ залежно від їх схемотехніки? Коротко охарактеризуйте відмінність цих ЛЕ.

Перерахуйте основні параметри ЛЕ і поясніть їх.

Поясніть будову ЛЕ ТТЛ і принцип їх роботи.

Поясніть будову ЛЕ ЕЗЛ і принцип їх роботи.

Поясніть будову ЛЕ КМДН і принцип їх роботи.

Поясніть будову ЛЕ І2Л і принцип їх роботи.

3Практичне заняття № 3

Суматори. Компаратори

МЕТА ЗАНЯТТЯ: практично засвоїти побудову і принцип роботи суматорів і цифрових компараторів

ТРИВАЛІСТЬ ЗАНЯТТЯ: 2 ауд. год.

Основні теоретичні відомості

Суматори — це комбінаційні пристрої, призначені для додавання чисел, представлених двійковими сигналами.

Суматори класифікують за такими ознаками: способом додавання – паралельні, послідовні та паралельно-послідовні; кількістю вхідних кількість входів – напівсуматори, однорозрядні або багаторозрядні суматори; організацією зберігання результату додавання – комбінаційні, накопичувальні, комбіновані; системою числення – позиційні (двійкові, двійково-десяткові, трійкові) та непозиційні, наприклад, у системі залишкових класів; розрядністю – 8-, 16-, 32-, 64-розрядні; способом подання від’ємних чисел – в оберненому або доповнювальному кодах, а також їх модифікаціях; часом додавання – синхронні та асинхронні.

Розглянемо додавання двох однорозрядних двійкових чисел, для чого складемо операції додавання, в якій відображено значення вхідних чисел А і В, значення результату сумування S і значення переносу в старший розряд Р (табл. 3 .3).

Таблиця 3.3 – Таблиця істинності роботи півсуматора

А |

В |

Р |

S |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

Згідно табл. 3 .3 робота півсуматора, описується наступним рівнянням:

Очевидно, що по відношенню до стовпця S реалізується логічна функція "виключаюче АБО". Пристрій, який реалізує дану таблицю називається півсуматором (рис. 3 .7).

а) б)

а — схема півсуматора, б — позначеня півсуматора

Рисунок 3.7 – Півсуматор

Для побудови багаторозрядних суматорів використовують однорозрядні суматори. Побудувати однорозрядний суматор можна на ЛЕ, але простішим способом побудови є використання півсуматорів згідно рис. 3 .8. Побудову багаторозрядних суматорів з використанням однорозрядних суматорів представлена на рис. 3 .9.

а) б)

Рисунок 3.8 – Схема однорозрядного суматора виконаного на півсуматорах

Рисунок 3.9 – Схема багаторозрядного суматора

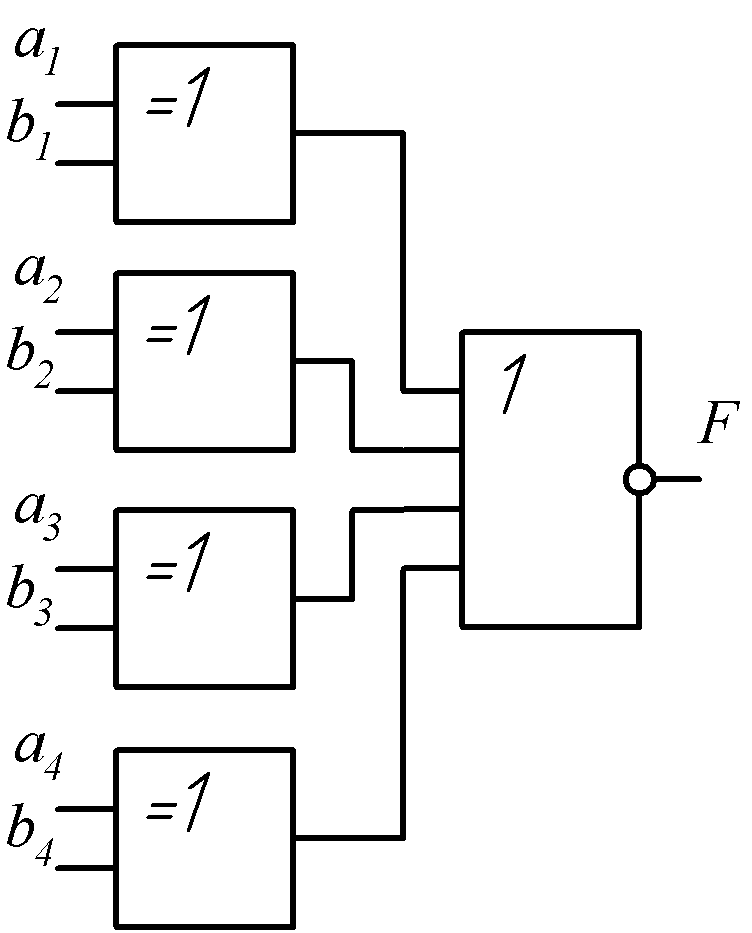

Вузол порівняння (цифровий компаратор) — це цифровий пристрій, призначений для порівняння двох багаторозрядних двійкових чисел. В найпростішому випадку потрібно встановлювати тільки рівність двох чисел A і B. Схема такого компаратора представлена на рис. 3 .10. Принцип роботи цієї схеми полягає в наступному: при рівності чисел A і B на виходах всіх ЛЕ ВИКЛЮЧАЮЧЕ‑АБО присутній сигнал лог. 0 і на виході ЛЕ АБО-НЕ буде сигнал лог. 1, якщо хоча б один із відповідних розрядів чисел A і B відрізняються, то на один із входів ЛЕ АБО-НЕ надходить сигнал лог. 1 і на його виході з’являється сигнал лог. 0.

Рисунок 3.10 – Схема порівняння багаторозрядних чисел

Компаратори, які порівнюють числа із визначенням знаку нерівності мають набагато складнішу будову і як правило їх виготовлюють у вигляді інтегральних мікросхем. Прикладом такого компаратора є мікросхема 564ИП2 (рис. 3 .11). Особливістю цієї мікросхеми є можливість нарощування розрядності чисел для порівняння.

а) б)

а — умовне графічне позначення компаратора 564ИП2, б — схема збільшення розрядності чисел для порівняння

Рисунок 3.11 – Вузол порівняння багаторозрядних чисел