Санкт-Петербургский Государственный Электротехнический Университет

«ЛЭТИ»

кафедра ВТ

Пояснительная записка

к курсовой работе по дисциплине:

«Конструкционно-техническое обеспечение производства ЭВМ»

|

Выполнил: |

Гладилин Г.А. Гречухин М.Н. Хамаганова М.М. |

|

Группа: Вариант: |

3371 7 |

|

Проверил: |

Зуев И.С. |

Санкт-Петербург

2006

0. Задание

|

# |

Фрагмент |

№ рис. |

Внешние условия включения |

F 4 min |

мкм |

||

|

на входе |

на выходе |

||||||

|

|

|

ОФ |

|||||

|

7 |

СМ |

5; 7 |

|

|

|

|

262 |

-

Техническое задание

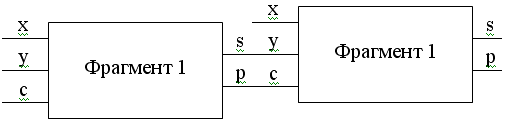

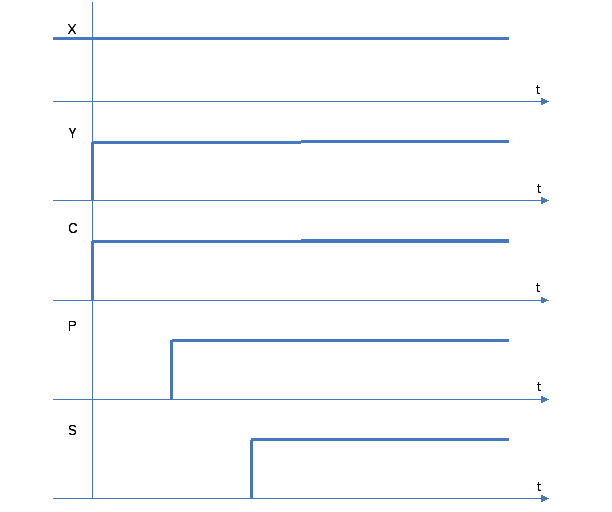

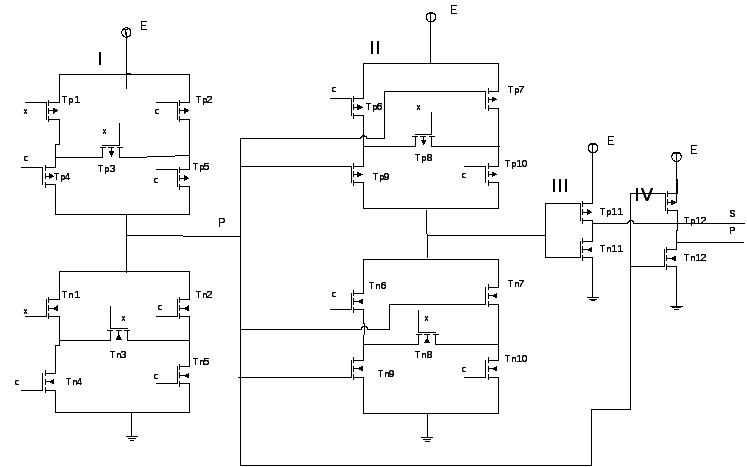

Блок схема внешних условий включения фрагмента в БИС приведена на рис. 1.1, а временная диаграмм его функционирования на рис. 1.2.

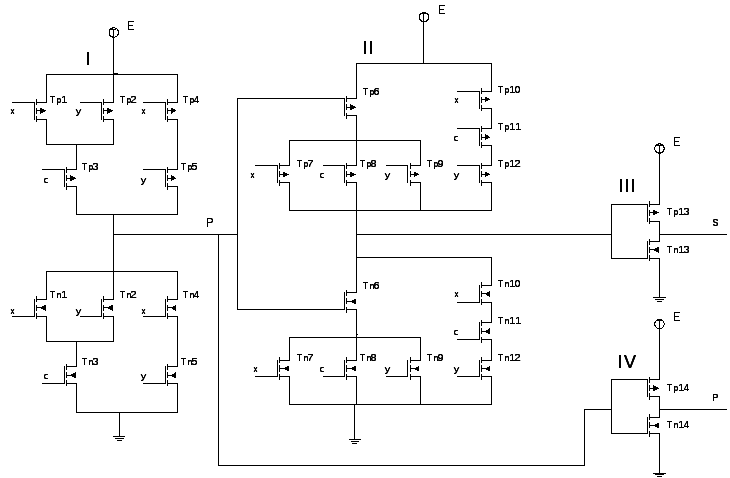

Рис. 1.1. Блок-схема внешних условий включения фрагмента в БИС

Рис. 1.2. Временная диаграмма работы фрагмента БИС

Фрагмент реализует следующие логические функции:

![]()

Для варианта схемы фрагмента изображены на рис. 1.3. и 1.4.

Времени задержки фрагмента рассчитывается для набора входных сигналов, исходя из следующих внешних условий включения:

-

Входной сигнал

является предварительно установленным,

т.е. все переходные процессы под

воздействием этого сигнала в схеме

фрагмента уже произошли к моменту

прихода остальных сигналов.

является предварительно установленным,

т.е. все переходные процессы под

воздействием этого сигнала в схеме

фрагмента уже произошли к моменту

прихода остальных сигналов. -

Сигналы

поступают

на входы фрагмента с некоторых каскадов,

выраженных эквивалентными инверторами,

и имеют конечное время формирования.

поступают

на входы фрагмента с некоторых каскадов,

выраженных эквивалентными инверторами,

и имеют конечное время формирования. -

Выходы схемы

и

и

подключены к выходам

подключены к выходам

и

и

соответственно

следующего фрагмента.

соответственно

следующего фрагмента.

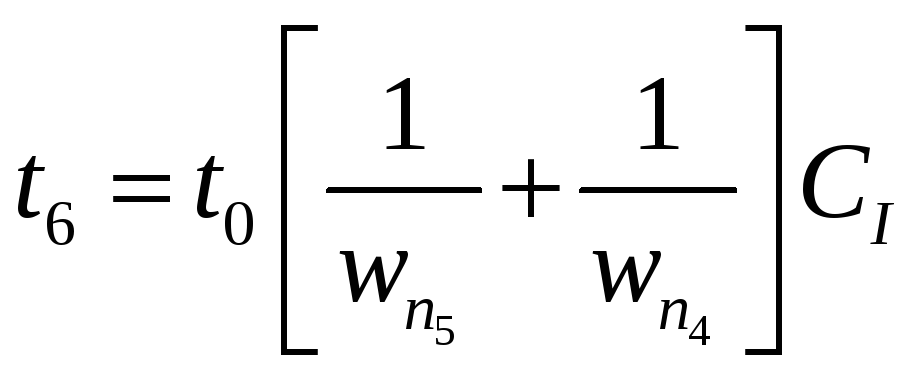

Целевой

функцией условной задачи минимизации

является функция

![]() ,

где

,

где

![]() -- время формирования выходного сигнала

-- время формирования выходного сигнала

![]() ,

а

,

а

![]() --

время формирования выходного сигнала

--

время формирования выходного сигнала

![]() .

.

Максимальное

значение суммы ширин каналов транзисторов

схемы

![]() равно 262.

равно 262.

Рис. 1.4. Сумматор, схема 1.

Рис. 1.3. Сумматор, схема 2.

2. Расчет схемы и оптимизация

-

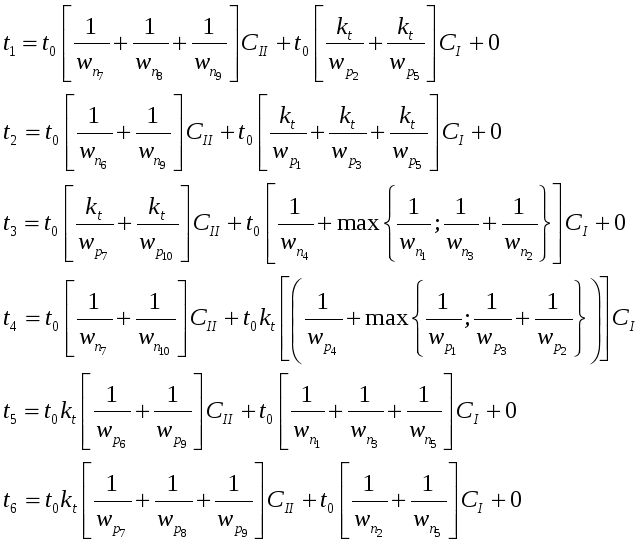

Вывод формул времен задержек схем фрагмента

Для расчета времен задержек схемы составлены таблицы их переключений – табл. 2.1. и 2.2. для схемы 1 и 2 соответственно, в которых представлены все возможные варианты переключения каскадов, принимающих участие в формировании выходных сигналов, наборы входных сигналов, транзисторы, образующие путь тока перезаряда нагрузочной емкости каскада и перечислены транзисторы, образующие эту емкость.

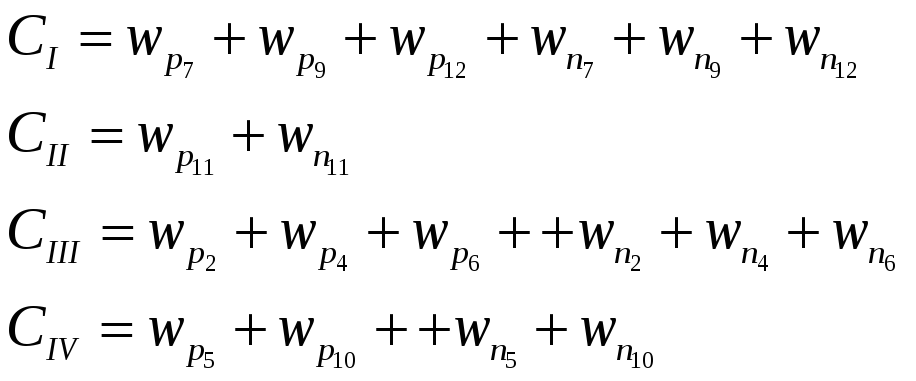

Обозначив

через

![]() нагрузочная емкость

нагрузочная емкость

![]() -того

каскада схемы, запишем выражения для

нагрузочных емкостей каскадов:

-того

каскада схемы, запишем выражения для

нагрузочных емкостей каскадов:

-

для первой схемы:

-

для второй схемы:

Внимательно рассмотрим обе схемы:

1. Схема №1 (рис. 1.3):

Очевидно,

что для I-го

каскада:

![]() ,

т.к.

мостовое соединение всегда имеет меньшее

R,

чем какое-либо другое соединение.

,

т.к.

мостовое соединение всегда имеет меньшее

R,

чем какое-либо другое соединение.

Очевидно,

для II-го

каскада:

![]() ,

поскольку переключение происходит

через транзисторы:

,

поскольку переключение происходит

через транзисторы:

![]() и

не зависит от времени переключения I-го

каскада.

и

не зависит от времени переключения I-го

каскада.

Тогда

нам необходимы времена:

![]() для обоих каскадов.

для обоих каскадов.

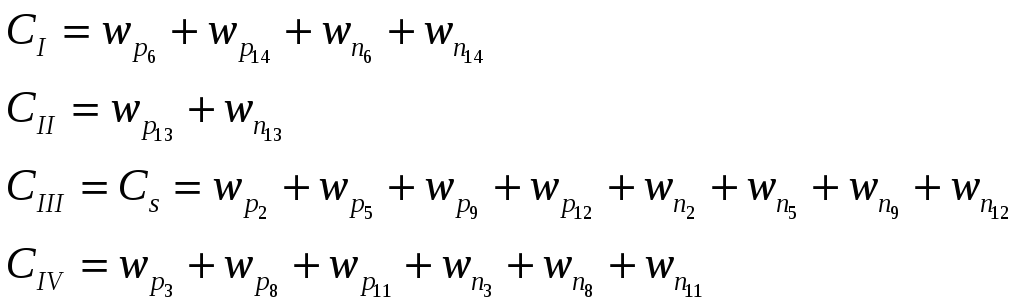

Запишем времена задержек:

I-ый каскад:

Таблица 2.1.

Переключение фрагмента БИС (схема 1)

|

## |

Сигнал |

I |

II |

III |

IV |

||

|

c |

y |

x |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

------- |

------- |

------- |

------- |

|

1 |

0 |

0 |

1 |

|

|

|

|

|

2 |

0 |

1 |

0 |

|

|

|

|

|

3 |

0 |

1 |

1 |

|

|

|

|

|

4 |

1 |

0 |

0 |

|

|

|

|

|

5 |

1 |

0 |

1 |

|

|

|

|

|

6 |

1 |

1 |

0 |

|

|

|

|

|

7 |

1 |

1 |

1 |

------- |

------- |

-------- |

-------- |

|

## |

Сигнал |

I |

II |

III |

IV |

||

|

c |

y |

x |

|||||

|

0 |

0 |

0 |

0 |

|

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

|

2 |

0 |

1 |

0 |

|

|

|

|

|

3 |

0 |

1 |

1 |

|

|

|

|

|

4 |

1 |

0 |

0 |

|

|

|

|

|

5 |

1 |

0 |

1 |

|

|

|

|

|

6 |

1 |

1 |

0 |

|

|

|

|

|

7 |

1 |

1 |

1 |

|

|

|

|

Переключение фрагмента БИС (схема 2)

II-ой каскад:

2. Схема №2 (рис. 1.4):

Очевидно, что для I-го каскада:

![]() ,

т.к.

параллельно-последовательное соединение

в случаях

,

т.к.

параллельно-последовательное соединение

в случаях

![]() имеет меньше R,

чем в случае

имеет меньше R,

чем в случае

![]() .

.

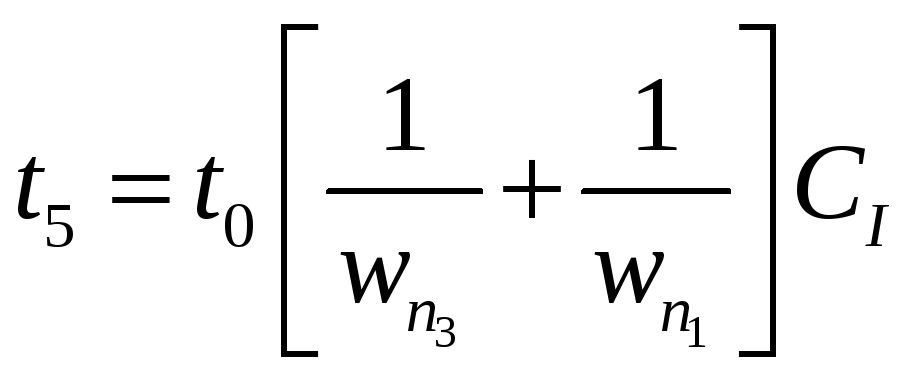

Для II-го каскада:

![]() ,

т.к. в

,

т.к. в

![]() не участвует I-ый

каскад, и переключение идет только за

счет трёх транзисторов.

не участвует I-ый

каскад, и переключение идет только за

счет трёх транзисторов.

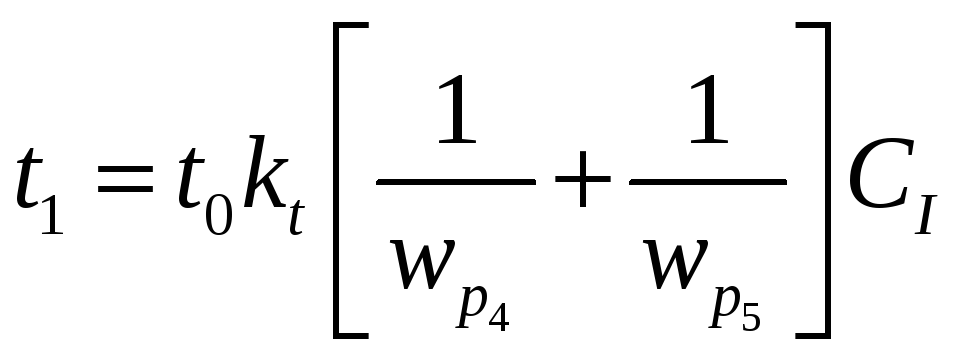

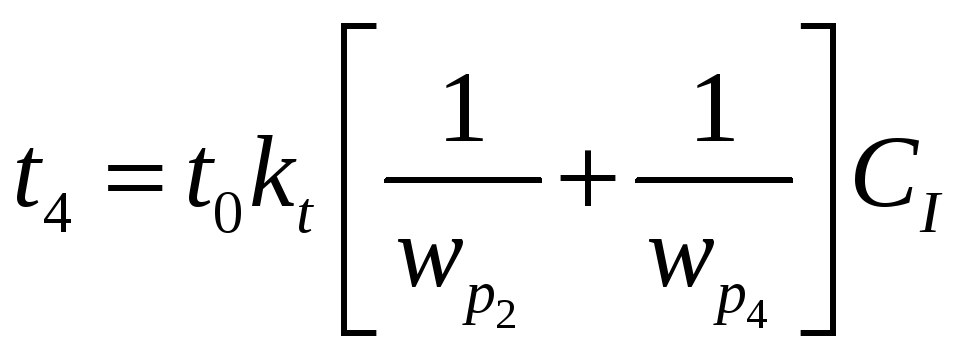

Таким

образом, для двух каскадов имеем:

![]()

I-ый каскад:

II-ой каскад: