- •Федеральное агентство железнодорожного транспорта

- •Электронная техника и преобразователи Учебное пособие

- •Часть 1

- •Контрольные вопросы

- •Параметры тиристоров

- •Контрольные вопросы

- •Контрольные вопросы

- •Контрольные вопросы

- •Контрольные вопросы

- •Контрольные вопросы

- •Контрольные вопросы

- •Контрольные вопросы

- •Логические элементы на полевых транзисторах моп–структуры. Ключи на моп–транзисторах.

- •Контрольные вопросы

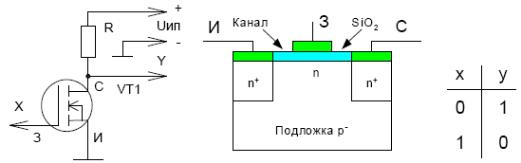

Логические элементы на полевых транзисторах моп–структуры. Ключи на моп–транзисторах.

Рис. 10.3. Ключ на МОП–транзисторе

Недостатком данных ключей является наличие резисторов, которые занимают в подложке значительно больше места, чем транзистор. Поэтому наиболее широко применяются ИМС, у которых вместо резистора также применяется МОП – транзистор, но с каналом другого типа проводимости. Такие взаимодополняющие структуры получили название МОП – пар.

Комплементарная МОП – пара (КМОП)

Если на затвор (Рис 10.4) подать сигнал логического нуля, то в транзисторе VT2 (c каналом n–типа проводимости) канал будет отсутствовать, а в транзисторе VT1 с каналом p–типа канал будет индуцирован, т. к. на затворе относительно истока будет действовать отрицательное напряжение. Через этот канал выход Y соединяется с плюсом ИП, и на выходе будет высокий уровень логической единицы. При подаче на вход логической единицы канал в транзисторе VT1 исчезает, а в VT2 канал индуцируется и через этот канал соединяется с нулевым потенциалом общего провода, следовательно, на выходе будет логический ноль.

Рис. 10.4. Пара КМОП

Достоинства комплементарной МОП–пары – отсутствие резисторов, что позволяет повысить степень интеграции; очень малое потребление тока от ИП, так как между плюсом и минусом ИП всегда оказывается транзистор, у которого нет канала. Недостаток комплементарной МОП–пары – низкое быстродействие.

Реализация функции И-НЕ в КМОП–логике

Если хотя бы на одном из входов имеется сигнал логического нуля, в соответствующем транзисторе с каналом p–типа – VT1 или VT2 – будет индуцирован канал, через который выход Y соединяется с плюсом ИП, и на выходе будет логическая единица. При подаче на оба входа логических единиц в VT1 и в VT2 каналы исчезают, а в транзисторах VT3 и VT4 каналы индуцируются, и через эти каналы выход Y соединяется с общим проводом, следовательно, на выходе будет логический ноль.

Эмиттерно–связная логика (ЭСЛ)

ЭСЛ является самой быстродействующей из всех типов логики. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения или отсечки. Основой ЭСЛ является дифференциальный эмиттерный каскад, изображённый на рисунке 10.5.

Рис. 10.5. Дифференциальный эмиттерный каскад

Особенность ЭСЛ: разница уровней логической единицы и нуля очень мала, следовательно, помехоустойчивость плохая. Чтобы повысить помехоустойчивость, в ЭСЛ используется схема, при которой в цепи коллектора – соединение с общим проводом, а в цепь эмиттера подаётся минус напряжения ИП. Это приводит к тому, что все уровни напряжения отрицательны и ЭСЛ плохо согласуются с другими типами логики.

Интегральные триггеры

Широкое распространение получили цифровые ИМС релейного типа, имеющие два устойчивых состояния и называемых триггерами. Переход триггера из одного устойчивого состояния в другое происходит под воздействием сигнала управления и сопровождается скачкообразным изменением выходных токов и напряжений. В настоящее время выпускаются серии различных триггеров в виде самостоятельных ИМС.

В отличие от комбинационных логических схем, триггеры – это последовательностные схемы, т.е. устройства с памятью. Их выходные сигналы зависят не только от сигналов на входах в данный момент времени, но и от ранее воздействовавших сигналов.

Типы триггеров в зависимости от способов управления:

1. Асинхронные или не тактируемые.

2. Синхронные или тактируемые.

Изменение состояние асинхронного триггера происходит сразу же после изменения сигналов на его управляющих входах. У синхронного триггера изменение состояния под действием управляющих сигналов возможно только при присутствии сигнала на специальном тактовом входе. Тактирование может осуществляться импульсом (т.е. потенциалом) или фронтом импульса (т.е. перепадом потенциала). Поэтому различают триггеры со статическим и динамическим управлением. Существуют также универсальные триггеры, которые могут работать как в тактируемом, так и в не тактируемом режиме. Чаще всего применяются синхронные триггеры, которые обладают большой помехоустойчивостью.

Типы триггеров в зависимости от функционального назначения:

1) RS–триггеры; 2) D–триггеры; 3) JK–триггеры; 4) T–триггеры.

На основе триггеров строятся счетчики, регистры, элементы памяти, которые составляют основу ЦВМ.

Наиболее простой симметричный триггер может быть выполнен на основе двух элементов И–НЕ или двух элементов ИЛИ–НЕ (рис. 10.6).

Рис. 10.6. Простейший триггер: а) – на элементах ИЛИ-НЕ, б) – на элементах И-НЕ

Асинхронный RS–триггер

Закон функционирования RS–триггера поясняется таблицей истинности. S и R – информационные сигналы на входах триггера. Сокращения даны от слов S ( set – установка) и R( reset – сброс). Qn – выходной логический сигнал до поступления входных сигналов, Qn+1 – то же после воздействия входных сигналов.

Таблица истинности R–S триггера

S |

R |

Qn+1 |

0 |

0 |

Qn |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

Неопределённость |

При подаче сигнала 1 на вход S триггер переходит в состояние Qn+1=1. При поступлении 1 на вход R устанавливается Qn+1= 0. Следовательно, триггер является аналогом реле. Наряду с этим он служит элементом памяти, т.е. сохраняет информацию о последней из поступивших команд и при отсутствии новых команд на входах. При S=R=0 состояние триггера не меняется. Совпадение команд S=R=1 ("включить" – "отключить") недопустимо. При таком сочетании входных сигналов состояние выхода неопределенно и это сочетание не используется.

Рис. 10.7. RS–триггер

На рисунке 10.7 приведено обозначение RS–триггера, временные диаграммы, иллюстрирующие его работу и реализация RS–триггера на логических элементах И–НЕ. Особенностью триггера являются обратные связи, позволяющие учитывать предыдущее состояние.

RS–триггер может

иметь инверсные входы

![]() и S. Такой триггер запускается переходом

информационного сигнала от 1 к 0 (низкий

активный уровень). В ряде серий ЦИМС

имеются готовые схемы RS триггеров.

и S. Такой триггер запускается переходом

информационного сигнала от 1 к 0 (низкий

активный уровень). В ряде серий ЦИМС

имеются готовые схемы RS триггеров.

Синхронный JК–триггер

В отличие от асинхронного триггера, который переключается мгновенно при изменении входного сигнала, синхронный триггер воспринимает информацию только при положительном (от 0 к 1) переходе импульсов на тактовом входе и переходит в новое устойчивое состояние в момент среза тактового импульса (триггер является двухступенчатым). Такая особенность позволяет синхронизировать во времени изменение состояния многих ячеек одного устройства тем самым исключая его непредусмотренные состояния. Назначение входов К и J аналогичны R и S (сброс и установка). Микросхема К155ТВ1 представляет собой синхронный JК–триггер с дополнительными асинхронными установочными инверсными входами R и S. Схема и временные диаграммы триггера представлена на рис. 10.8.

В таблице истинности

Н – неопределенное (любое) состояние.

Информацию можно загружать от входов

J и К или задерживать ее только при

![]() =

=![]() =1.

Если

=

=0

состояние

=1.

Если

=

=0

состояние

![]() и

и

![]() неопределенное. Из временной диаграммы

видно, что на при отсутствии тактового

импульса (

неопределенное. Из временной диаграммы

видно, что на при отсутствии тактового

импульса (![]() )

информация по входам J и К не воспринимается

и состояние триггера не меняется.

)

информация по входам J и К не воспринимается

и состояние триггера не меняется.

Рис. 10.8. JK-триггер

Таблица истинности JК–триггера К155ТВ1

Режим работы |

Вход |

Выход |

|||||

|

|

|

|

|

|

|

|

Асинхронная установка |

0 |

1 |

H |

H |

H |

1 |

0 |

Асинхронный сброс |

1 |

0 |

H |

H |

H |

0 |

1 |

Неопределенность |

0 |

0 |

H |

H |

H |

1 |

1 |

|

1 |

1 |

|

1 |

1 |

n-1 |

n-1 |

Загрузка 1 (установка) |

1 |

1 |

|

0 |

1 |

1 |

0 |

Загрузка 0 ( сброс) |

1 |

1 |

|

1 |

0 |

0 |

1 |

Хранение (нет изменений) |

1 |

1 |

|

0 |

0 |

n-1 |

n-1 |

Счетный Т–триггер

Рис. 10.9. Т-триггер

Этот триггер получается из JК–триггера путем присоединения J и К входов к потенциалу, соответствующему логической 1 (можно оставить их "висящими в воздухе"). Таким образом остался только один тактовый вход – Т. В момент среза тактового импульса триггер переключается на противоположное состояние. Обозначение и временные диаграммы Т–триггера приведено на рис. 10.9. Из диаграммы видно, что частота повторения сигнала Q в 2 раза меньше, чем сигнала Т, т.е. Т–триггер делит частоту импульсов на 2. Т–триггер широко применяется в делителях частоты, счетчиках и др.

D–триггер

D–триггер или

триггер задержки (delay) передает на выход

информацию, поступающую на вход при

появлении тактового импульса, поэтому

момент смены выходной информации

несколько задерживается относительно

момента смены входной информации. Логика

работы D–триггера определяется уравнением

Q![]() +1=D.

D–триггер помимо тактового входа имеет

только один вход D=J=

+1=D.

D–триггер помимо тактового входа имеет

только один вход D=J=![]() .

Сигнал на входе D запоминается в момент

тактового импульса и хранится до

следующего тактового импульса. Поэтому

D–триггер является элементом памяти,

находит широкое применение в регистрах.

.

Сигнал на входе D запоминается в момент

тактового импульса и хранится до

следующего тактового импульса. Поэтому

D–триггер является элементом памяти,

находит широкое применение в регистрах.

Рис. 10.10. D–триггер

Микросхема К155ТМ2 содержит в корпусе два D–триггера. Обозначение и временная диаграмма приведены на рисунке 1.10.

Входы и – асинхронные установочные с низким активным уровнем. Сбрасывают состояние триггера независимо от сигнала на тактовом входе. Если состояние = =0, состояние Q и неопределенно. Информация на выход Q и при наличии входного D и тактового С сигнала передается только при = =1. Сигнал D передается на выходы Q и по фронту тактового импульса.

Основные параметры логических ТТЛ, ТТЛШ элементов

1. Напряжение питания Uпит = +5В±(5 – 10)%.

2. Быстродействие. Характеризуется временем переключения (изменение состояния на противоположное), составляет 5 – 50 нс.

3. Помехоустойчивость. Определяется тем уровнем помех на полезном сигнале, который не приводит к ложному изменению состояния элемента. У большинства ТТЛ–элементов порогом срабатывания их является напряжение Uпор=1,4В, то есть напряжение от 0 до 1,4В воспринимается как 0, а 1,4В и больше воспринимается как 1.

4. Потребляемая мощность.

5. Нагрузочная способность. Составляет несколько миллиампер.

6. Выходные параметры ТТЛ, ТТЛШ: Логической 1 соответствует Uвых>2,4В, логическому 0 соответствует Uвых<0,4В.

Переключение

Переключение