- •Санкт-петербургский государственный электротехнический университет "лэти" имени в.И. Ульянова (ленина)

- •Архитектура внешних выводов

- •Выбор форматов данных

- •Определение модели памяти и структуры регистровой памяти

- •5.1. Модель памяти

- •5.2. Виртуальная память Страничное преобразование

- •Свопинг

- •5.3. Структура регистровой памяти

- •Форматы команд

- •6.1. Способы адресации

- •6.2. Форматы команд

- •Система команд

- •Внутренняя организация

- •8.1. Структурно-функциональная схема процессора

- •9. Основные алгоритмы функционирования

- •9.1 Чтение команды из озу

- •9.2 Декодирование команды

- •9.3 Обработка регистровой команды (rg-rg)

- •9.4 Обработка команды типа регистр – память (rg-озу)

- •9.5 Обработка условного ввода / вывода (в/в)

- •9.6 Обработка безусловных переходов (б/п)

- •9.7 Обработка условных переходов (у/п)

- •9.8 Обработка прерываний

- •10. Алгоритмы выполнения отдельных операций

- •10.1. Выборка команды

- •10.2. Арифметические и логические операции

- •10.3. Передача управления

- •11. Основные операции на шине

- •11.1 Чтение слова из зу и запись слова в зу .

- •11.2 Обработка прерывания.

- •11.3 Обработка захвата шины.

- •13. Вывод

- •14. Список использованной литературы.

10. Алгоритмы выполнения отдельных операций

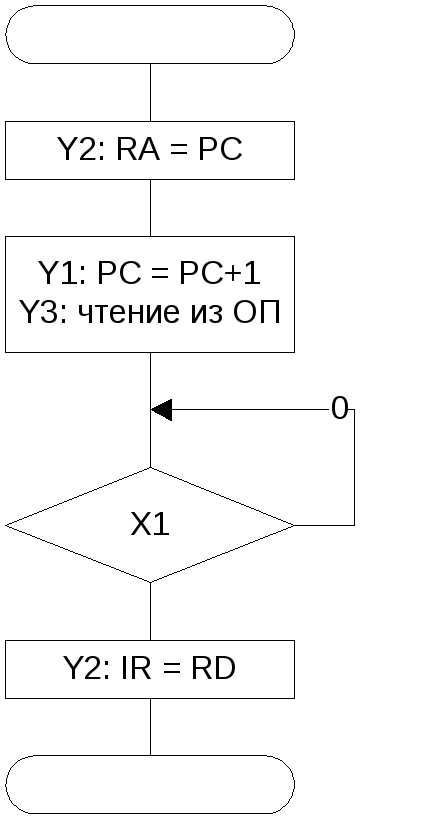

10.1. Выборка команды

Фрагмент структуры процессора, относящийся к выборке команды

Соответствующая ей микропрограмма.

У разрабатываемого процессора разрядность команды и разрядность ячейки памяти, в которой она хранится, совпадают, поэтому при выборке требуется только одно обращение к памяти команд. Исходными данными является адрес размещения команды в памяти ЭВМ, который хранится в счётчике адреса команд PC. Содержимое PC передаётся в регистр адреса RA оперативной памяти, осуществляется чтение из оперативной памяти хранящейся в ней информации в регистр даных RD. После чтения из ОП, требуемая команда будет находиться в регистре RD. Далее осуществляется передача содержимого RD на IR.

10.2. Арифметические и логические операции

Фрагмент структуры процессора, относящийся к выполнению операций

Соответствующая ей микропрограмма.

В регистре команд уже находится очередная считанная команда. В регистр адреса помещается адрес второго операнда. После этого операнд считывается из оперативной памяти. Первый операнд находится в регистре общего назначения. Специальным сигналом запускается АЛУ и результат записывается в регистр, указанный в команде.

10.3. Передача управления

1. Безусловный переход

|

|

|

В счётчик адресов команд просто записывается адресная часть команды перехода.

2. Условный переход

|

|

|

Адрес, указанный в команде, записывается в счётчик команд, только если выполняется заданное условие. Условие задаётся кодом команды. Если условие не выполняется, то просто происходит переход к следующей команде.

11. Основные операции на шине

11.1 Чтение слова из зу и запись слова в зу .

В начале первого такта Т1 выдается 32-х разрядный адрес, который по сигналу ALE фиксируется в регистре. В начале второго такта Т2 выдается сигнал RD по которому начинается процесс чтения из памяти. Если память медленная, то выдается сигнал READY, который заставляет процессор вставлять холостые такты TW. В последнем такте Tw снимается сигнал READY, и процессор запоминает данные с шины данных в течение такта Т3. В конце этого такта снимается сигнал RD и цикл обмена завершается.

Запись слова осуществляется аналогичным образом. В начале первого такта выдается адрес, который по сигналу ALE фиксируется регистре. В начале второго такта Т2 выдается слово на шину данных и сигнал записи WR. Если устройство медленное, то оно выдает сигнал READY, который обеспечивает добавление тактов задержки TW. В последнем такте Tw снимается сигнал READY. В конце такта Т3 снимается сигнал записи WR и запись прекращается.

11.2 Обработка прерывания.

Процессор имеет встроенный контроллер приоритетного прерывания. При прерывании устройство выставляет сигнал INT на шину. Процессор заканчивает текущую операцию и выставляет сигнал INTA, сигнализирующий о том, что прерывание принято и далее начинается обработка прерывания (обычно она связана с передачей или приемом данных от устройства, вызвавшего прерывание). Циклы, входящие в обработку прерывания выполняются обычным способом.

11.3 Обработка захвата шины.

Если устройство хочет захватить шину, то оно выставляет сигнал HLD.

Реакцией процессора на HLD является только выдача сигнала HLDA и отключение от шины: процессор заканчивает текущий цикл обмена (период Т1) и передает управление устройству потребовавшему шину. Устройство начинает обмен, с любым другим устройством (или с памятью) причем оно является ведущим и соответственно само выставляет все необходимые сигналы (период Т2).