- •1. Значення курсового проекту при вивченні дисципліни «мікропроцесорна техніка»

- •Основні етапі віконання курсового проекту

- •2.1. Тематика курсового проекту

- •2.2. Структура і зміст курсового проекту

- •Указівки з виконання курсового проекту

- •Рекомендації щодо проектування мікропроцесорних контролерів.

- •3.1. Вимоги до тмпк

- •3.2. Функціональна схема тмпк

- •Елементна база технологічного мікропроцесорного контролера

- •4.1. Супервізори живлення і охоронні таймери

- •4.2. Функціональні характеристики таймерів реального часу

- •4.3. Мікросхеми ram для технологічних контролерів

- •4.4. Послідовні інтерфейси технологічних контролерів

- •4.5. Регістри введення-виведення технологічних контролерів

- •4.6. Модифікатори адреси

- •4.7. Оптично розв'язані вузли

- •4.8. Інтерфейс lcd-індикаторів

- •4.9. Диспетчери пам'яті технологічних контролерів

- •4.10. Аналого-цифрові перетворювачі

- •4.11. Цифроаналогові перетворювачі

- •4.12. Аналіз відібраних мікросхем послідовних dac

- •4.13. Варіанти принципових схем підсистеми цифроаналогових перетворювачів

- •Розрахункова частина

- •5.1. Розрахунок числа розрядів ацп

- •5.2. Розрахунок частоти дискретизації

- •Варіанти завдання на курсовий проект

- •2. Розрахункова частина.

- •КурсовИй проект

- •КурсовИй проект

- •Пояснювальна записка

3.2. Функціональна схема тмпк

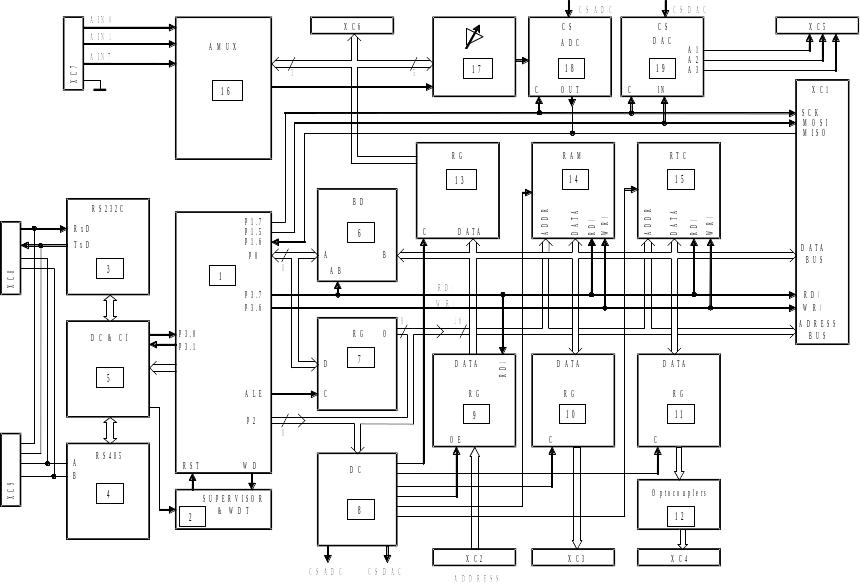

Функціональна схема (рис. 3.1) містить наступні основні вузли:

|

Рис. 3.1 – Узагальнена функціональна схема мікроконтролерного модуля

|

Сокети для установки одного з наступних мікроконтролерів: АТ89с51/52/53/55/8252 і AT90S4414/8515 в корпусі DIP40 або АТ89с1051/2051/4051 і AT90S2313 в корпусі DIP20.

Супервізор живлення з схемою захисту від зависань WDT. Вихід супервізора сполучений з входом RST мікроконтролера. Слід зазначити, що полярність сигналів RST різна для мікроконтролерів серій х51 і AVR, отже, супервізор повинен забезпечувати видачу сигналів скидання обох полярностей і можливість вибору однієї з них. Один з входів супервізора сполучено з інтерфейсом RS232C з метою забезпечення можливості скидання ядра по цьому інтерфейсу. На вхід WDT повинні періодично подаватися імпульси запуску від мікроконтролера.

Інтерфейс RS232C.

Інтерфейс RS485.

Логіка управління інтерфейсами з оптичною ізоляцією одного або обох з них. Вона пов'язана з інтерфейсами 3 і 4 і мікроконтролером 1. Кількість зв'язків з мікроконтролером повинна бути мінімальною, при цьому функціональні можливості управління інтерфейсами бажано мати максимальними.

Шинний формувач даних магістралі.

Регістр-защіпка молодшого байта адреси.

Дешифратор адреси.

Регістр введення значень модифікатора Хс2. Модифікатор Хс2 (і решта всіх роз'ємів, окрім Хс1) повинен бути виконаний у вигляді штирьового роз'єму типу PLD. Це дозволяє встановлювати на нього перемички для установки адреси, а якщо модифікатор адреси не використовується або використовується не повністю, на роз'єм може встановлюватися плаский кабель і входи роз'єму можуть використовуватися для інших цілей.

Регістр виведення даних через штирьовий роз'єм ХС3.

Регістр виведення даних через штирьовий роз'єм Хс4 або оптично ізольованих даних через вузол оптронів 12 і штирьовий роз'єм Хс4. На парні контакти штирьового роз'єму Хс4 дані надходять безпосередньо з виходів регістра 11, на непарні — через вузол оптронів 12. Таке рішення дозволяє з потреби вибирати довільну комбінацію ізольованих і неізольованих сигналів.

Вузол оптронів.

Регістр управління функціями вхідного аналогового комутатора 16 і операційного підсилювача 17, коефіцієнт підсилювання якого можна змінювати.

Швидкодіюча оперативна пам'ять з паралельним доступом.

Таймер реального часу з паралельним доступом і вбудованою незалежною оперативною пам'яттю.

Вхідний аналоговий мультиплексор для комутації вхідних сигналів аналого-цифрового перетворювача ADC (18).

Операційний підсилювач з можливістю вибору полярності сигналу і коефіцієнта підсилення.

Аналого-цифровий перетворювач ADC з розрядністю 12—16 двійкових розрядів і зв'язком по послідовному каналу SPI.

Здвоєний або вбудований цифроаналоговий перетворювач DAC з розрядністю 10—8 двійкових розрядів і зв'язком по послідовному каналу SPІ.

Окрім перерахованих функціональних вузлів на функціональній схемі показано роз'єми: Хс1 — роз'єм магістралі (може бути в метричному Снп59/96 або дюймового виконання С96); Хс2 — штирьовий роз'єм PLD-16, що використовується як модифікатор адреси або для подачі зовнішніх вхідних сигналів; ХСЗ — штирьовий роз'єм PLD-16, що використовується для видачі вихідних сигналів; Хс4 — штирьовий роз'єм PLD-20, що використовується для видачі вихідних оптично не розв'язаних або розв'язаних сигналів; Хс5 — штирьовий роз'єм PLD-6, що використовується для видачі вихідних аналогових сигналів з DAC (19); Хс6 — штирьовий роз'єм PLD-16, що використовується для видачі вихідних сигналів регістра 13 у випадку, якщо мультиплексори 16 і операційний підсилювач 17 не використовуються; Хс7 — штирьовий роз'єм PLD-16 для подачі вхідних аналогових сигналів на ADC (18) через мультиплексор 16 і операційний підсилювач 17; Хс8 і Хс9 — два паралельно сполучених штирьових роз'єми PLD-10, для підключення до інтерфейсів RS232C і RS485.

Слід зазначити, що ряд сигналів управління на узагальненій схемі не вказано, оскільки їх остаточне призначення і джерело їх видачі буде визначено після вибору типів і схем включення всіх вузлів функціональної схеми (наприклад, не вказані оптично розв'язані входи, входи переривань, сигнали управління інтерфейсами, тощо).