- •// Регистр

- •// Регистр

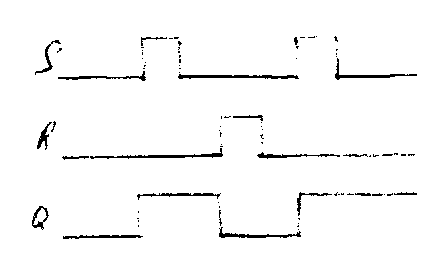

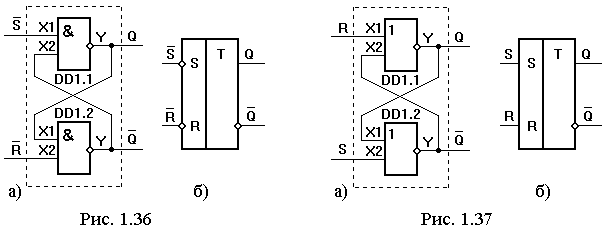

- •Синхронный rs-триггер:

- •Р аботает по тому же принципу как и суммирующий, только информация снимается с инверсного выхода

- •Р аботает по тому же принципу как и суммирующий, только информация снимается с инверсного выхода

- •Сумматор параллельного действия с параллельной передачей переноса:

- •Сумматор параллельного действия с параллельной передачей переноса:

Регистр – устройство предназначенное для кратковрем. хранения и преобраз-я многоразрядных двоичных чисел.

А синхр.

RS-триггер с прям. входами

RS-

триггер с прямыми входами можно получить,

имея в наличии два логических элемента

2ИЛИ-НЕ.

синхр.

RS-триггер с прям. входами

RS-

триггер с прямыми входами можно получить,

имея в наличии два логических элемента

2ИЛИ-НЕ.

R |

S |

Qn |

Qn+1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

H/O |

1 |

1 |

1 |

H/O |

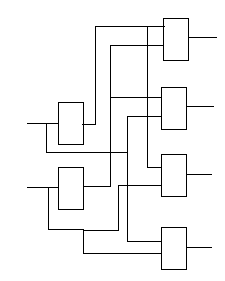

// Регистр

Основными

видами регистров являются параллельные

и последовательные (сдвигающие).

В

параллельном

регистре

на тактируемых D-триггерах рисунок 1 код

запоминаемого числа подается на

информационные входы всех триггеров и

записывается в регистр с приходом

тактового импульса. Выходная информация

изменяется с подачей нового входного

слова и приходом следующего синхроимпульса.

Такие регистры и спользуют

в системах оперативной памяти. Число

триггеров в них равно максимальной

разрядности хранимых слов.

спользуют

в системах оперативной памяти. Число

триггеров в них равно максимальной

разрядности хранимых слов.

a1 |

a0 |

y3 |

y2 |

y1 |

y0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

y0=a1*a0 |

y2=a1*a0 |

y1=a1*a0 |

y3=a1*a0 |

СЧЁТЧИКОМ-наз устр-во предназн-е для подсчёта числа импульсов поданных на Вх. Их можно построить последовательно соед-в Т-триггеры. Осн любого счётч явл линейка триггеров. Между триггерами могут быть введены доп-е ОС позвол-е получ любой коэффиц деления, а не только 2(в степени «n»). Микросх: К155ИЕ1(6).

Регистр – устройство предназначенное для кратковрем. хранения и преобраз-я многоразрядных двоичных чисел.

А синхр. RS-триггер с прям. входами RS- триггер с прямыми входами можно получить, имея в наличии два логических элемента 2ИЛИ-НЕ.

R |

S |

Qn |

Qn+1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

H/O |

1 |

1 |

1 |

H/O |

// Регистр

Основными видами регистров являются параллельные и последовательные (сдвигающие). В параллельном регистре на тактируемых D-триггерах рисунок 1 код запоминаемого числа подается на информационные входы всех триггеров и записывается в регистр с приходом тактового импульса. Выходная информация изменяется с подачей нового входного слова и приходом следующего синхроимпульса. Такие регистры и спользуют в системах оперативной памяти. Число триггеров в них равно максимальной разрядности хранимых слов.

a1 |

a0 |

y3 |

y2 |

y1 |

y0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

y0=a1*a0 |

y2=a1*a0 |

y1=a1*a0 |

y3=a1*a0 |

СЧЁТЧИКОМ-наз устр-во предназн-е для подсчёта числа импульсов поданных на Вх. Их можно построить последовательно соед-в Т-триггеры. Осн любого счётч явл линейка триггеров. Между триггерами могут быть введены доп-е ОС позвол-е получ любой коэффиц деления, а не только 2(в степени «n»). Микросх: К155ИЕ1(6).

ТРИГГЕР-ЛОГ-е устр-во с +ОС, котор может неограниченно долго наход в 1 из 2 уст-х сост-й удержив-сь в нём за счёт +ОС, а не Вх-х сигналов.

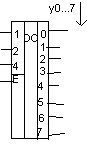

Д ЕШИФРАТОР-устр-во,

котор преобраз 2-е числа в небольш по

знач-ю 10-е числа (на вх-е 2-й код, на вых

10-й код). Их использ в схемах адрес-ии.

Вх-ы нужны для: 1подачи 2-х чмсел и обознач

весами разрядов, вых обознач-я 10-и

числами. При подаче на вх-ы 2-го числа

появл сигнал на опред вых-е № котор

соотв-т вх-у коду. (Рис+)

ЕШИФРАТОР-устр-во,

котор преобраз 2-е числа в небольш по

знач-ю 10-е числа (на вх-е 2-й код, на вых

10-й код). Их использ в схемах адрес-ии.

Вх-ы нужны для: 1подачи 2-х чмсел и обознач

весами разрядов, вых обознач-я 10-и

числами. При подаче на вх-ы 2-го числа

появл сигнал на опред вых-е № котор

соотв-т вх-у коду. (Рис+)