- •Регістри

- •4.1. Загальна характеристика регістрів

- •4.2. Установлювальні мікрооперації. Однофазний і парафазний спосіб записування інформації

- •4.3. Записування інформації від двох джерел

- •4.4. Зчитування інформації

- •4.5. Логічні мікрооперації в регістрах

- •4.6. Мікрооперації зсуву

- •3.7. Перетворення послідовного коду в паралельний і навпаки

- •Лічильники

- •5.1. Загальна характеристика лічильників

- •5.3. Двійкові реверсивні лічильники

4.6. Мікрооперації зсуву

Зсув

– це одночасне просторове переміщення

двійкового слова в розрядній сітці із

збереженням порядку слідування нулів

і одиниць. Регістри, призначені для

виконання мікрооперацій зсуву, називаються

регістрами зсуву або зсувовими.

Мікрооперації

зсуву використовують у процесі виконання

команд множення, ділення і нормалізації.

Крім того, за допомогою зсуву здійснюється

перетворення паралельного коду в

послідовний або навпаки (наприклад, при

обміні інформацією з магнітними

стрічками і дисками).

Зсув слова

може виконуватися вправо (у бік молодших

розрядів) або вліво (у бік старших

розрядів). Позначимо однорозрядні

мікрооперації зсуву вправо і вліво

символами R і L відповідно. Розрізнюють

правий і лівий арифметичний (Rа, Lа),

логічний (Rл, Lл) і циклічний (Rц, Lц)

зсуви слова.

Нехай в регістрі А

записано слово Аn An-1…A2 A1, де А1 – молодший

розряд; Аn – старший розряд. Символічно

мікрооперації зсуву записуються таким

чином:

арифметичні зсуви (знаковий

розряд не зсувається):

RGA:=Ra(A)=An 0 An-1…

A2; RGA:=La(A)=An An-2… A1 0;

логічні

зсуви (одночасно зсуваються всі

розряди):

RGA:=Rл(A)=0 An An-1… A2;

RGA:=Lл(A)= An-1 An-2… A1 0;

циклічні зсуви

(між старшим і молодшим розрядами є

кільцевий зв'язок):

RGA:=Rц(A)=А1 An An-1…

A2; RGA:=Lц(A)= An-1 An-2… A1

Аn.

Арифметичні та циклічні зсуви

переважно використовують при виконанні

команд в процесорах, а логічні зсуви

забезпечують перетворення послідовного

коду в паралельний і навпаки в пристроях

зв'язку з магнітними стрічками і

дисками.

Зсувні регістри проектують

на двоступеневих RS- (або JK-) або

D-тригерах з динамічним керуванням по

фронту . Такі тригери забезпечують

розділення під час процесів приймання

нової інформації в кожному розряді

та видачі (зсуву) старої.

Припустимо,

що в реверсивному регістрі мають

виконуватися паралельний запис слова

А за сигналом керування Yзп і зсуви

інформації вліво і вправо під впливом

керуючих сигналів Lл і Rл. Функції

збудження Sі і Rі для кожного розряду

регістра зсуву на двоступеневих

RS-тригерах мають вигляд:

Si=Yзп

AiÚRлQi+1ÚLл Qi-1; Ri=Yзп

Ú

Rл![]() Ú

Lл

Ú

Lл![]() (4.5)

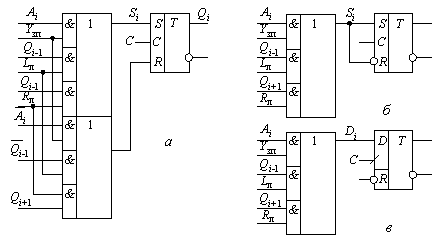

Схема одного розряду регістра

зсуву на RS-тригерах згідно з рівнянням

(3.5) показана на рис.4.6,а.

Економічна

схема розряду регістра, в якій функція

на R-входи тригера утвориться інвертуванням

сигналу Si, показана на рис.4.6, б. Однак у

цьому випадку час записування даних

збільшується за рахунок затримки

інвертора.

Для регістра зсуву на

D-тригерах функції збудження мають

вигляд:

Di=Yзп AiÚ Rл Qi+1Ú LлQi-1.

(4.6)

Схема розряду

регістра зсуву на D-тригерах згідно з

рівнянням (4.6) показана на рис.4.6,

в.

(4.5)

Схема одного розряду регістра

зсуву на RS-тригерах згідно з рівнянням

(3.5) показана на рис.4.6,а.

Економічна

схема розряду регістра, в якій функція

на R-входи тригера утвориться інвертуванням

сигналу Si, показана на рис.4.6, б. Однак у

цьому випадку час записування даних

збільшується за рахунок затримки

інвертора.

Для регістра зсуву на

D-тригерах функції збудження мають

вигляд:

Di=Yзп AiÚ Rл Qi+1Ú LлQi-1.

(4.6)

Схема розряду

регістра зсуву на D-тригерах згідно з

рівнянням (4.6) показана на рис.4.6,

в.

Рис.4.6

Схема розряду регістра зсуву: а – на

RS-тригері; б – з інвертором на вході R;

в – на D-тригері

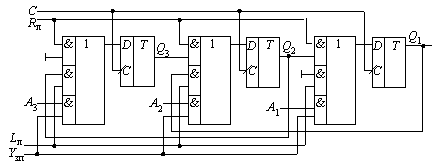

Приклад побудови

реверсивного трирозрядного регістра

зсуву на D-тригерах з динамічним керуванням

показаний на рис.4.7.

Рис.4.6

Схема розряду регістра зсуву: а – на

RS-тригері; б – з інвертором на вході R;

в – на D-тригері

Приклад побудови

реверсивного трирозрядного регістра

зсуву на D-тригерах з динамічним керуванням

показаний на рис.4.7.

Рис.4.7

Схема реверсивного регістра зсуву на

D-тригерах

Рис.4.7

Схема реверсивного регістра зсуву на

D-тригерах

Реверсивний регістр зсуву працює таким чином. При значенні сигналу Yзп=1 в регістр записується інформація паралельним однофазним кодом. При значенні сигналу Rл=1 інформація, що зберігається, одночасно зсувається у бік молодших розрядів, при цьому розряд Q3 обнуляється. При значенні сигналу Lл=1 інформація в регістрі одночасно зсувається у бік старших розрядів, при цьому розряді Q1 обнуляється. Запис і зсув інформації відбуваються по фронту синхроімпульсу.