- •Аннотация

- •Введение

- •1. Задание на проектирование узла

- •Общее задание

- •Вариант задания 2.4

- •2. Сравнительный анализ предлагаемых вариантов

- •2.1. Реализация узла на основе счетчика и дешифратора

- •2.2. Реализация узла на основе сдвигающего регистра

- •2.3. Выбор оптимальной схемы

- •3. Описание основных элементов библиотеки сапр quartus II и стандартных микросхем, необходимых для реализации узла

- •3.1. Список использованных элементов

- •3.2. Характеристики используемой интегральной схемы

- •4. Процесс синтеза Второго варианта схемы средствами Сапр Quartus II

- •5. Разработка интерфейса сопряжения схемы узла с процессорной системой, для которой проектируемый узел является внешним устройством

- •6. Список внешних контактов

- •7. Полная принципиальная электрическая схема Разработанного узла

- •7.1. Список использованных элементов

- •7.2. Внешние подключения

- •7.3. Схема узла

- •7.4. Итоговое макетирование схемы

- •Заключение

- •Список использованных источников

- •Приложение а

3. Описание основных элементов библиотеки сапр quartus II и стандартных микросхем, необходимых для реализации узла

3.1. Список использованных элементов

Для реализации узла были использованы следующие примитивы из библиотеки САПР Quartus II:

-

Входные контакты (input);

-

Выходные контакты (output);

-

8-мивходовой элемент ИЛИ (OR8).

Из настраиваемых компонентов библиотеки САПР Quartus II использовались следующие:

-

26-разрядный сдвигающий вправо регистр (lpm_shiftreg) имеет 26 информационных входов, 26 выходов, вход для синхронной параллельной загрузки, вход для синхронизации по переднему фронту, вход расширения DR (shiftn), изображен на рисунке 17;

Рисунок 17

3.2. Характеристики используемой интегральной схемы

Разрабатываемый узел проектируется с учетом возможного тестирования на интегральной микросхеме семейства Cyclone II (произведена компанией Altera). Данная микросхема обладает характеристиками, приведенными в таблице 5.

Таблица 5

|

Наименование |

EP2C5Q208C8 |

|

Количество логических блоков |

4608 |

|

Семейство ПЛИС |

Cyclone II |

|

Количество блоков логических массивов (LAB) |

288 |

|

Полное количество RAM |

117 Кбит |

|

Количество I/O |

142 |

|

Напряжение питания ядра |

1.2 В |

|

Напряжение питания I/O |

3.3 В |

|

Максимальная рабочая частота |

260 МГц |

4. Процесс синтеза Второго варианта схемы средствами Сапр Quartus II

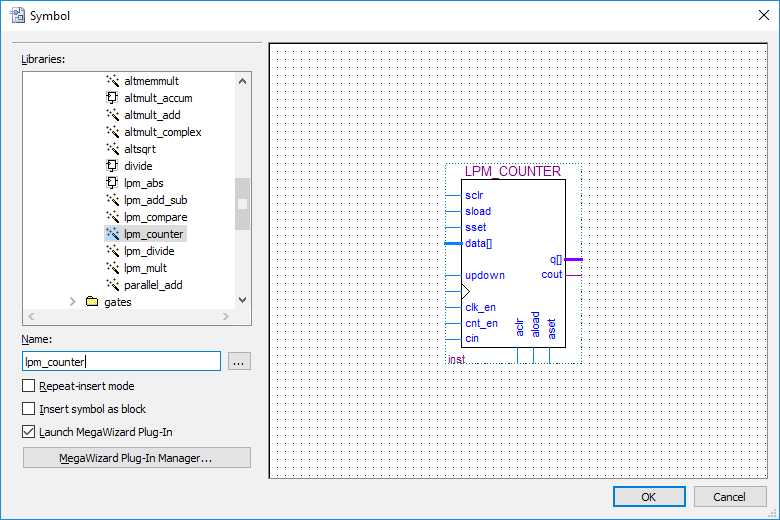

Процесс синтеза в САПР Quartus II начинается с создания нового проекта. Пользователь создает файл схемы и добавляет в него различные примитивы и блоки, предусмотренные в библиотеке САПР. Добавление элемента в файл схемы осуществляется с помощью функции Insert Symbol доступной на панели инструментов, или по двойному клику по пустой области. После этого появится окно, представленное на рисунке 18.

Рисунок 18

Пользователь выбирает в данном окне нужные элементы, добавляет их на схему, после чего соединяет между собой одноразрядными линиями и шинами. Также имеется возможность подписывать линии и шины, что позволяет не прорисовывать соединения. Итоговая схема представлена на рисунке 25.

После завершения синтеза пользователь может смоделировать работу схемы. Существует 2 режима: функциональное и временное. Временное моделирование отличается от функционального тем, что в нем учитываются временные задержки элементов, в результате чего, например, выходные сигналы комбинационных цепей формируются не сразу.

Для проведения моделирования необходимо создать Vector Waveform File и задать в нем вектор входных воздействий. После запуска симуляции появится отчет с информацией о сигналах на выходах схемы.

5. Разработка интерфейса сопряжения схемы узла с процессорной системой, для которой проектируемый узел является внешним устройством

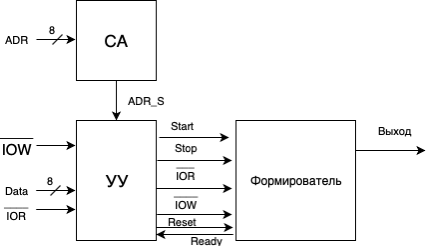

Разрабатываемый

узел подключается к процессорной системе

в качестве внешнего устройства с помощью

линии данных (Data),

поступающих от селектора адреса сигнала

соответствия (ADR_S),

сигнала записи в порт ( )

и сигнала чтения порта (

)

и сигнала чтения порта ( ).

Дальнейший механизм управления

реализуется устройством управления,

формирующим сигналы пуска (Start)

и останова (Stop),

изначально поступающие по линии данных,

линии готовности устройства (Ready)

и линии сброса (Reset).

Синхросигнал (clk),

необходимый для работы узла, должен

поступать от устройства управления, на

которое он поступает от разработанного

генератора. Схема сопряжения представлена

на рисунке 19.

).

Дальнейший механизм управления

реализуется устройством управления,

формирующим сигналы пуска (Start)

и останова (Stop),

изначально поступающие по линии данных,

линии готовности устройства (Ready)

и линии сброса (Reset).

Синхросигнал (clk),

необходимый для работы узла, должен

поступать от устройства управления, на

которое он поступает от разработанного

генератора. Схема сопряжения представлена

на рисунке 19.

Рисунок 19

Сначала

в шине данных два старших бита (7

и 6)

устанавливаются в 0

для

инициализационного сброса, процессор

выставляет строб сигнала

на линию управления и адрес устройства

на шину адреса, на формирователь приходит

сигнал Reset,

затем в два старших бита шины данных

устанавливаются в значение 01,

устройство управления передает сигнал

Start

разрешения работы формирователя. При

подаче на старшие биты шины данных 11 и

последующего сигнала

на линию управления и адрес устройства

на шину адреса, на формирователь приходит

сигнал Reset,

затем в два старших бита шины данных

устанавливаются в значение 01,

устройство управления передает сигнал

Start

разрешения работы формирователя. При

подаче на старшие биты шины данных 11 и

последующего сигнала

УУ вырабатывает сигнал останова Stop,

который останавливает формирователь

только по завершении текущего цикла

работы и выдает в УУ сигнал Ready.

Если сигнал Stop

так и не поступил, устройство само

останавливает работу по завершении 100

циклов работы и выдает сигнал Ready

для дальнейших

действий. На рисунке 23 представлена

реализация управляющего устройства

(УУ).

УУ вырабатывает сигнал останова Stop,

который останавливает формирователь

только по завершении текущего цикла

работы и выдает в УУ сигнал Ready.

Если сигнал Stop

так и не поступил, устройство само

останавливает работу по завершении 100

циклов работы и выдает сигнал Ready

для дальнейших

действий. На рисунке 23 представлена

реализация управляющего устройства

(УУ).