- •Аннотация

- •Введение

- •1. Задание на проектирование узла

- •Общее задание

- •Вариант задания 2.4

- •2. Сравнительный анализ предлагаемых вариантов

- •2.1. Реализация узла на основе счетчика и дешифратора

- •2.2. Реализация узла на основе сдвигающего регистра

- •2.3. Выбор оптимальной схемы

- •3. Описание основных элементов библиотеки сапр quartus II и стандартных микросхем, необходимых для реализации узла

- •3.1. Список использованных элементов

- •3.2. Характеристики используемой интегральной схемы

- •4. Процесс синтеза Второго варианта схемы средствами Сапр Quartus II

- •5. Разработка интерфейса сопряжения схемы узла с процессорной системой, для которой проектируемый узел является внешним устройством

- •6. Список внешних контактов

- •7. Полная принципиальная электрическая схема Разработанного узла

- •7.1. Список использованных элементов

- •7.2. Внешние подключения

- •7.3. Схема узла

- •7.4. Итоговое макетирование схемы

- •Заключение

- •Список использованных источников

- •Приложение а

МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

Курсовая РАБОТА

по дисциплине «Узлы и устройства средств вычислительной техники»

Тема: Проектирование цифровых узлов

на микросхемах программируемой логики

|

Студент гр. 6307 |

|

Лазарев С.О. |

|

Преподаватель |

|

Головина Л.К. |

Санкт-Петербург

2019

ЗАДАНИЕ

на курсовую работу

|

Студент Лазарев С.О. |

||

|

Группа 6307 |

||

|

Тема работы: проектирование цифровых узлов на микросхемах программируемой логики

|

||

|

Исходные

данные: разработать

узел, формирующий заданную

последовательность импульсов. Входные

сигналы частоты f =1/T поступают от

генератора ГТИ (генератор разрабатывается).

Выходная последовательность периодична

с периодом

|

||

|

Предполагаемый объем пояснительной записки: Не менее 20 страниц. |

||

|

Дата выдачи задания: 01.05.2019 |

||

|

Дата сдачи курсовой работы: 05.06.2019 |

||

|

Дата защиты курсовой работы: 05.06.2019 |

||

|

Студент гр. 6307 |

|

Лазарев С.О. |

|

Преподаватель |

|

Головина Л.К.. |

Аннотация

Данный

проект содержит информацию о разработке

узла, формирующего заданную

последовательность импульсов. Входные

сигналы частоты f =1/T поступают от

генератора ГТИ (генератор разрабатывается).

Выходная последовательность периодична

с периодом

.

Узел рассматривается как внешнее

устройство процессорной системы.

Сигналы пуска и останова поступают из

управляющего устройства (процессора),

количество периодов работы от пуска до

останова фиксируется счетчиком (их

максимальное число 100). Было предложено

два варианта реализации, среди них был

выбран оптимальный.

.

Узел рассматривается как внешнее

устройство процессорной системы.

Сигналы пуска и останова поступают из

управляющего устройства (процессора),

количество периодов работы от пуска до

останова фиксируется счетчиком (их

максимальное число 100). Было предложено

два варианта реализации, среди них был

выбран оптимальный.

Введение

Цель работы:

-

научиться ориентироваться в разнообразии возможностей цифровой техники при проектировании специализированных устройств и эффективно применять современную элементную базу;

-

научиться выбирать вариант реализации решений при синтезе цифровых узлов и устройств, отвечающий требованиям ТЗ и наилучший по заданным критериям качества;

-

научится пользоваться возможностями современных САПР при проектировании устройств на базе микросхем программируемой логики;

-

научиться технически грамотно описывать функционирование разрабатываемых узлов и устройств и правильно оформлять техническую документацию.

1. Задание на проектирование узла

-

Общее задание

Разработать

узел, формирующий заданную последовательность

импульсов с линейно изменяющимися

интервалами между импульсами. Входные

сигналы частоты f =1/T поступают от

генератора ГТИ (генератор разрабатывается).

Выходная последовательность периодична

с периодом

.

Узел рассматривается как внешнее

устройство процессорной системы. Сигналы

пуска и останова поступают из управляющего

устройства (процессора), количество

периодов работы от пуска до останова

фиксируется счетчиком (их максимальное

число 100).

.

Узел рассматривается как внешнее

устройство процессорной системы. Сигналы

пуска и останова поступают из управляющего

устройства (процессора), количество

периодов работы от пуска до останова

фиксируется счетчиком (их максимальное

число 100).

-

Вариант задания 2.4

Параметры узла, заданные вариантом, приведены в таблице 1.

Таблица 1

|

Tp |

Номера импульсов, проходящих на выход |

Начальный адрес |

θ |

|

25 |

0,1,3,7,12,18,25 |

30h |

4 |

Временная диаграмма сигналов показана на рисунке 1.

Рисунок 1

2. Сравнительный анализ предлагаемых вариантов

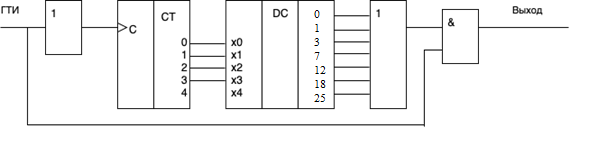

2.1. Реализация узла на основе счетчика и дешифратора

Структурная схема рассматриваемого варианта приведена на рисунке 2.

Рисунок 2

-

СА – селектор адреса;

-

РГ – регистр хранения данных;

-

УУ – устройство управления;

-

ГТИ – генератор тактовых импульсов;

-

ГЕН – тактовый генератор;

-

ША – шина адреса;

-

ШД – шина данных;

-

– сигнал

управления от процессора (запись в

порт).

– сигнал

управления от процессора (запись в

порт).

Вариант представляет собой внешнее устройство, состоящее из узлов, перечисленных выше. Селектор адреса определяет, что процессор обращается именно к заданному устройству, по шине данных в регистр РГ поступает сигнал к началу работы, устройство управления организует взаимодействие между узлами схемы, генератор задает тактовую частоту работы устройства, ГТИ формирует необходимый по заданию импульс со скважностью 4, а формирователь формирует импульсную последовательность с линейно изменяющимися интервалами между импульсами.

Структурная схема формирователя представлена на рисунке 3.

Рисунок 3

-

СЧ – счётчик;

-

ДЕШ – дешифратор;

-

ЛП – логический преобразователь.

Счётчик производит счет от 0 до 25, а дешифратор формирует 26 выходных значения из 5 входных, после чего логический преобразователь формирует результат на выход.

В таблице 2 представлена таблица истинности разрабатываемого узла для выходного сигнала, зависящего от номера такта.

Таблица 2

|

Номер такта |

Выходной сигнал |

|

|

10 сс |

2 сс |

|

|

0 |

00000 |

1 |

|

1 |

00001 |

1 |

|

2 |

00010 |

0 |

|

3 |

00011 |

1 |

|

4 |

00100 |

0 |

|

5 |

00101 |

0 |

|

6 |

00110 |

0 |

|

7 |

00111 |

1 |

|

8 |

01000 |

0 |

|

9 |

01001 |

0 |

|

10 |

01010 |

0 |

|

11 |

01011 |

0 |

|

12 |

01100 |

1 |

|

13 |

01101 |

0 |

|

14 |

01110 |

0 |

|

15 |

01111 |

0 |

|

16 |

10000 |

0 |

|

17 |

10001 |

0 |

|

18 |

10010 |

1 |

|

19 |

10011 |

0 |

|

20 |

10100 |

0 |

|

21 |

10101 |

0 |

|

22 |

10111 |

0 |

|

23 |

11000 |

0 |

|

24 |

11001 |

0 |

|

25 |

11010 |

1 |

Для определения номера такта узлу нужен счетчик, на который буде поступать сигнал от генератора. Для 26 значений достаточно счетчика на 5 разрядов (25 = 32 различных состояния), ограниченного максимальным значением 21.

Логическая функция переключения для выхода:

,

где

,

где

Функциональная схема приведена на рисунке 4.

Рисунок 4

Функциональное тестирование схемы:

Рисунок 5

.

Узел рассматривается как внешнее

устройство процессорной системы.

Сигналы пуска и останова поступают

из управляющего устройства (процессора),

причем при цикличной работе устройства

оно останавливается не мгновенно, а

по завершении текущего цикла работы,

количество периодов работы от пуска

до останова фиксируется счетчиком

(их максимальное число 100).

.

Узел рассматривается как внешнее

устройство процессорной системы.

Сигналы пуска и останова поступают

из управляющего устройства (процессора),

причем при цикличной работе устройства

оно останавливается не мгновенно, а

по завершении текущего цикла работы,

количество периодов работы от пуска

до останова фиксируется счетчиком

(их максимальное число 100).