- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

2.2 Арифметические операции над двоичными числами.

Арифметические операции над двоичными числами могут производиться по тем же правилам, что и над десятичными, однако, с целью упрощения цифровых систем для выполнения арифметических операций применяют алгоритмы, отличные от алгоритмов действий десятичной арифметики.

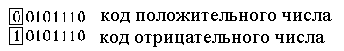

В двоичной системе счисления для представления знака числа используется дополнительный знаковый разряд (один или несколько разрядов), который располагается перед старшим числовым разрядом. Для положительных чисел значение знакового разряда Зн.р.=0, для отрицательного числа Зн.р.=1.

Операция вычитания в цифровых системах реализуется с помощью операции сложения.

Вычитаемое при этом представляется в дополнительном коде (если расчет не требует высокой точности - в обратном коде).

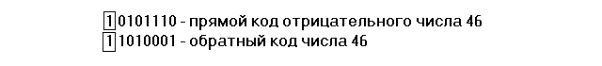

Двоичный код со знаком называют также прямым кодом. В качестве примера

рассмотрим положительное и отрицательное числа, десятичный эквивалент которых равен 4610.

Обратный код получается путем замены всех “0” на “1” и всех “1” на “0” прямого кода (двоичного числа со знаком). Причем, знаковый разряд при этом остается неизменным.

Замена “0” на единицу (“1”) называется инвертированием (также и замена “1”на “0”).

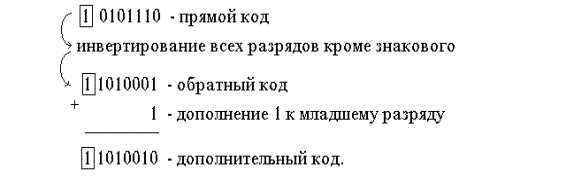

Обратный код, дополненный единицей в младшем разряде, называется дополнительным кодом. Последовательность действий при получении дополнительного кода:

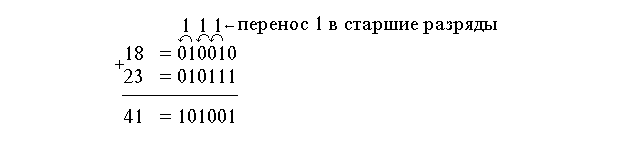

Сложение и вычитание двоичных чисел. Правила сложения двух двоичных чисел можно показать на следующем примере:

Пример сложения многоразрядных чисел. Требуется сложить два числа 1810 и 2310

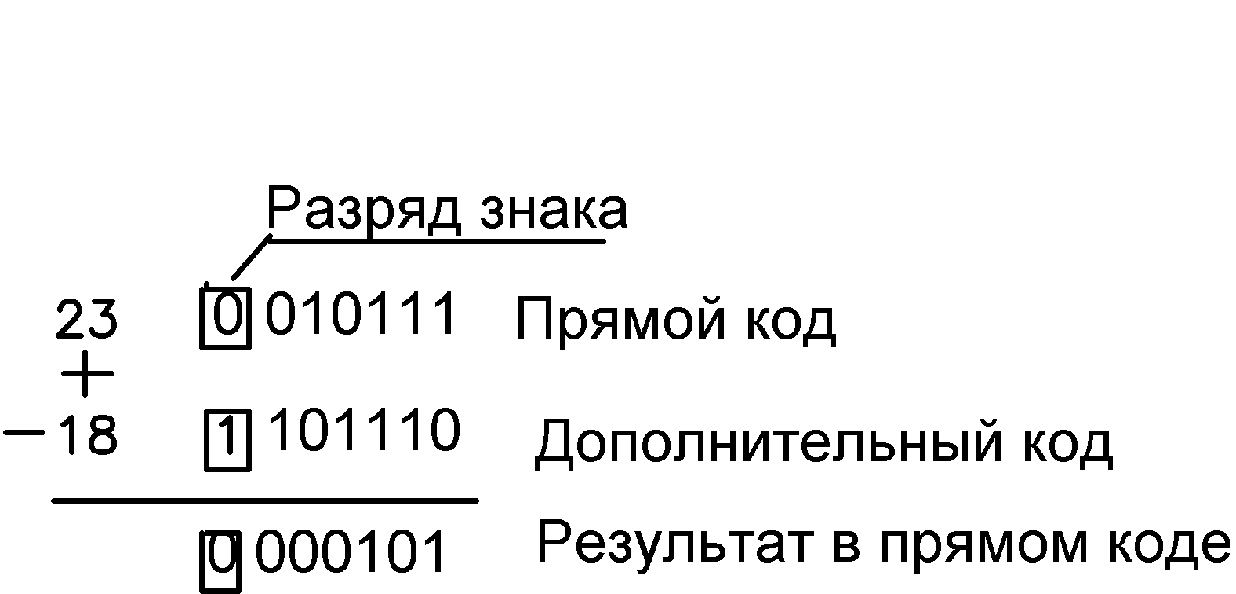

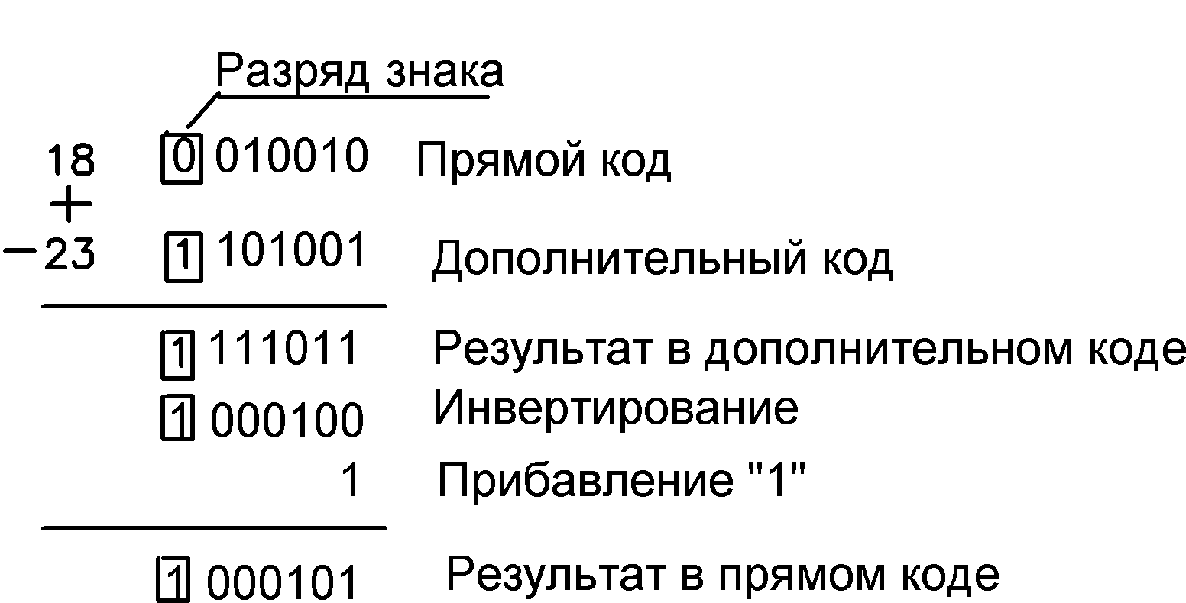

Вычитание в цифровых устройствах производится также как и сложение, только вычитающее представляется в дополнительном коде. Рассмотрим два примера, в первом требуется из числа 23 отнять число 18, а во втором из 18 отнять 23. С начала вычитающие представим в дополнительном коде:

010010 – 18 прямой код

101101 – 18 обратный код

+

1

________

101110 – 18 дополнительный код

010111 – 23 прямой код

101000 – 23 обратный код

+

1

________

101001- 23 дополнительный код

1)

Таким образом, получилось число плюс 5.

2)

Таким образом, получилось число минус 5.

Принято считать, что дополнительный код положительного числа совпадает с его прямым кодом. Операция вычитания с использованием только обратного кода (без дополнительных операций по переводу его в дополнительный код) приводит к ошибке, определяемой единицей в младшем разряде, и поэтому при точных расчетах не применяется.

Умножение двоичных чисел производится по тем же правилам, что и для десятичных с помощью таблиц двоичного умножения и сложения.

Пример. 1001![]() 101=?

101=?

Результат 1001 101=101101.

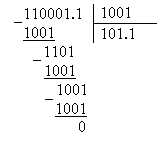

Деление двоичных чисел производится по тем же правилам, что и для десятичных. При этом используются таблицы двоичного умножения и вычитания.

Пример. 1100.011 : 10.01=?

Результат 1100.011 : 10.01=101.1.