- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

2.2. Архитектура микроконтроллеров

Понимание архитектуры микроконтроллеров является ключевым при изучении языков программирования типа ассемблер. Структура ассемблера, формат его команд, адресация операндов и т. д. полностью определяются архитектурой. Целью изучения архитектуры является:

выявление набора доступных для программирования регистров, их функционального назначения и структуры;

понимание организации оперативной памяти и порядка ее использования;

знакомство с типами данных;

изучение формата машинных команд;

выяснение организации обработки прерываний.

2.2.1. Архитектура микроконтроллеров mcs-51

Архитектура семейства MCS-51 в значительной мере предопределяется ее назначением - построение компактных и дешевых цифровых устройств. Все функции МК реализуются с помощью единственной микросхемы. В состав семейства MCS-51 входит целый ряд микросхем от самых простых микроконтроллеров до достаточно сложных. Микроконтроллеры семейства MCS-51 позволяют выполнять как задачи управления различными устройствами, так и реализовывать отдельные узлы аналоговой схемы. Все микросхемы этого семейства работают с одной и той же системой команд, большинство из них выполняется в одинаковых корпусах с совпадающей цоколевкой (нумерация выводов для корпуса). Это позволяет использовать для разработанного устройства микросхемы разных фирм - производителей (таких как Intel, Dallas, Atmel, Philips и т.д.) без переделки принципиальной схемы устройства и программы.

MCS-51 выполнен по Гарвардской архитектуре, где адресные пространства памяти программ и данных разделены.

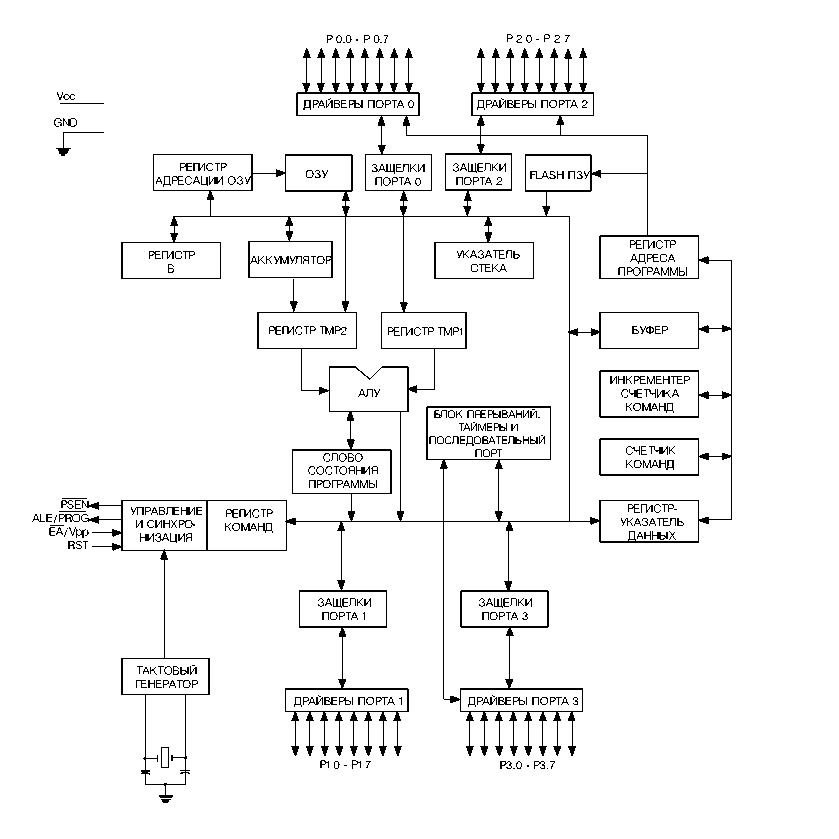

Структурная схема контроллера представлена на рис.2.3 и состоит из следующих основных функциональных узлов: блока управления, арифметико-логического устройства, блока таймеров/счетчиков, последовательного интерфейса и прерываний, программного счетчика (счетчика команд), памяти данных и памяти программ.

Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. Рассмотрим подробнее назначение каждого блока. По такой схеме построены практически все представители семейства MCS-51. Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов). Система команд всех контроллеров семейства MCS-51 содержит 111 базовых команд с форматом 1, 2 или 3 байта и не изменяется при переходе от одной микросхемы к другой. Это обеспечивает прекрасную переносимость программ с одной микросхемы на другую.

Блок управления и синхронизации (Timing and Control) предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков ОЭВМ во всех допустимых режимах ее работы. В состав блока управления входят:

устройство формирования временных интервалов,

комбинационная схема ввода-вывода,

регистр команд,

дешифратор команд.

Входные и выходные сигналы блока управления и синхронизации:

PSEN – разрешение программной памяти;

ALE – выходной сигнал разрешения фиксации адреса;

PROG – сигнал программирования;

EA – блокировка работы с внутренней памятью;

VPP – напряжение программирования;

RST – сигнал общего сброса.

Устройство формирования временных интервалов необходимо для синхронизации последовательности состояний ЦП, образующих машинный цикл, а также для правильной работы всех внутреннихзащелок и выходных буферов портов. Машинный цикл состоит из шести последовательныхсостояний (States) от S1 до S6, каждое из которых, в свою очередь, подразделяется на две фазы:

фазу 1 (Phase 1 - P1) и фазу 2 (Phase 2 - P2). Таким образом, машинный цикл может быть определен как последовательность временных интервалов S1P1, S1P2, S2P1,....,S6P2. Длительность фазы равна периоду следования тактовых импульсов, поэтому машинный цикл занимает 12 тактовых периодов.

Количество машинных циклов определяет продолжительность выполнения команд. Практически все команды выполняются за один или два машинных цикла, кроме команд умножения и деления, продолжительность выполнения которых составляет четыре машинных цикла. Логика ввода - вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода вывода Р0-Р3.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью дешифратора команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды.

Рис

2.3. Структурная схема однокристального

микроконтроллера Intel

8051

Рис

2.3. Структурная схема однокристального

микроконтроллера Intel

8051

(семейство MCS-51)

Арифметико-логическое устройство (ALU) представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛУ состоит из:

регистров временного хранения -TMP1 и TMP2,

ПЗУ констант,

сумматора,

дополнительного регистра - регистра В,

аккумулятора - ACC,

регистра слова состояния программ (регистр флагов)- PSW .

Регистры временного хранения TMP1, TMP2 - восьмиразрядные регистры, предназначенные для приема и хранения операндов на время выполнения операций над ними. Эти регистры программно не доступны.

ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.

Параллельный восьмиразрядный сумматор представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций сложения, умножения, неравнозначности и тождественности.

Регистр B - восьмиразрядный регистр, используемый во время операций умножения и деления. Для других инструкций он может рассматриваться как дополнительный сверхоперативный регистр.

Аккумулятор - восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига.

Регистр состояния программ PSW (Programm Status Word) предназначен для хранения слова состояния выполняемых команд. При выполнении многих команд в ALU формируется ряд признаков операции (флагов), которые фиксируются в регистре слова состояния программы (PSW). В табл. 1 приводится перечень флагов PSW, даются их символические имена и описываются условия их формирования.

Блок прерываний и последовательного интерфейса - UART(Universal Asynchronous Receiver/Transmitter) предназначен для организации ввода - вывода последовательных потоков информации и организации системы прерывания программ.

По определению прерывание означает временное прекращение основного процесса вычислений для выполнения некоторых запланированных или незапланированных действий, вызываемых работой аппаратуры или программы.

Эти действия могут носить сервисный характер, быть запросами со стороны программы пользователя на выполнение обслуживания либо быть реакцией на нештатные ситуации.

Табл. 1

Символ |

Разряд |

Имя и назначение |

|

CY |

PSW.7 |

Флаг переноса. Устанавливается и сбрасывается аппаратно или программно при выполнении арифметических и логических операций |

|

AC |

PSW.6 |

Флаг вспомогательного переноса. Устанавливается и сбрасывается только аппаратно при выполнении команд сложения и вычитания и сигнализирует о переносе или займе в бите 3 |

|

F0 |

PSW.5

|

Флаг 0. Может быть установлен, сброшен или проверен программой как флаг, специфицируемый пользователем |

|

RS1 |

PSW.4

|

Выбор банка регистров. Устанавливается и сбрасывается программно для выбора рабочего банка регистров |

|

RS0 |

PSW.0 |

||

OV |

PSW.2 |

Флаг переполнения. Устанавливается и сбрасывается аппаратно при выполнении арифметических операций |

|

– |

PSW.1 |

Не используется |

|

P |

PSW.0 |

Флаг паритета. Устанавливается и сбрасывается аппаратно в каждом цикле и фиксирует нечетное/четное число единичных битов в аккумуляторе, т.е. выполняет контроль по четности |

|

В состав блока входят:

логика управления,

регистр управления,

буфер передатчика,

буфер приемника,

приемопередатчик последовательного порта,

регистр приоритетов прерываний,

регистр разрешения прерываний,

логика обработки флагов прерываний и схема выработки вектора.

Счетчик команд (Program Counter) предназначен для формирования текущего 16-разрядного адреса внутренней памяти программ и 8/16-разрядного адреса внешней памяти программ. В состав счетчика команд входят 16-разрядные буфер РС, регистр РС и схема инкремента (увеличения содержимого на 1).

Память данных ОЗУ (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы.

Память программ (EPROM) предназначена для хранения программ и представляет собой постоянное запоминающее устройство (ПЗУ). В разных микросхемах применяются масочные, стираемые ультрафиолетовым излучением или FLASH ПЗУ.

Регистр указателя данных (DPTR) предназначен для хранения 16 - разрядного адреса внешней памяти данных.

Указатель стека (SP) представляет собой восьмиразрядный регистр, предназначенный для организации особой области памяти данных (стека), в которой можно временно сохранить любую ячейку памяти.

Порты P0, P1, P2, P3 являются квазидвунаправленными портами ввода - вывода и предназначены для обеспечения обмена информацией ОЭВМ с внешними устройствами, образуя 32 линии ввода- вывода.

Они предназначены для ввода или вывода информации побайтно. Каждый порт содержит управляемые регистр-защелку, входной буфер и выходной драйвер.

Выходные драйверы портов P0 и P2, а также входной буфер порта P0 используются при обращении к внешней памяти. При этом через порт P0 в режиме временного мультиплексирования сначала выводится младший байт адреса, а затем выдается или принимается байт данных. Через порт P2 выводится старший байт адреса в тех случаях, когда разрядность адреса равна 16 бит.

Все выводы порта P3 могут быть использованы для реализации альтернативных функций, перечисленных в табл. 2 . Эти функции могут быть задействованы путем записи 1 в соответствующие биты регистра-защелки (P3.0 – P3.7) порта P3.

Р0 является двунаправленным, а Р1 –Р3 квазидвунаправленными. Каждая линия портов может быть использована независимо для ввода или вывода.

По сигналу RST в регистры-защелки всех портов автоматически записываются единицы, настраивающие их тем самым на режим ввода.

Все порты могут быть использованы для организации ввода/вывода информации по двунаправленным линиям передачи. Однако порты P0 и P2 не могут быть использованы для этой цели в случае, если система имеет внешнюю память, связь с которой организуется через общую разделяемую шину адреса/данных, работающую в режиме временного мультиплексирования.

Табл. 2