- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

2. Архитектура микроконтроллера

2.1 Основные характеристики микроконтроллера

Микроконтроллер (МК) характеризуется:

1) тактовой частотой, определяющей максимальное время выполнения переключения элементов в ЭВМ;

2) разрядностью, т.е. максимальным числом одновременно обрабатываемых двоичных разрядов. Разрядностъ МК обозначается m/n/k/ и включает:

m -разрядность внутренних регистров, определяет принадлежность к тому или иному классу процессоров;

n - разрядность шины данных, определяет скорость передачи информации;

к - разрядность шины адреса, определяет размер адресного пространства.

Например, МП i8088 характеризуется значениями m/n/k=16/8/20;

3) архитектурой. Понятие архитектуры МК включает в себя систему команд и способы адресации, возможность совмещения выполнения команд во времени, наличие дополнительных устройств в составе микропроцессора, принципы и режимы его работы.

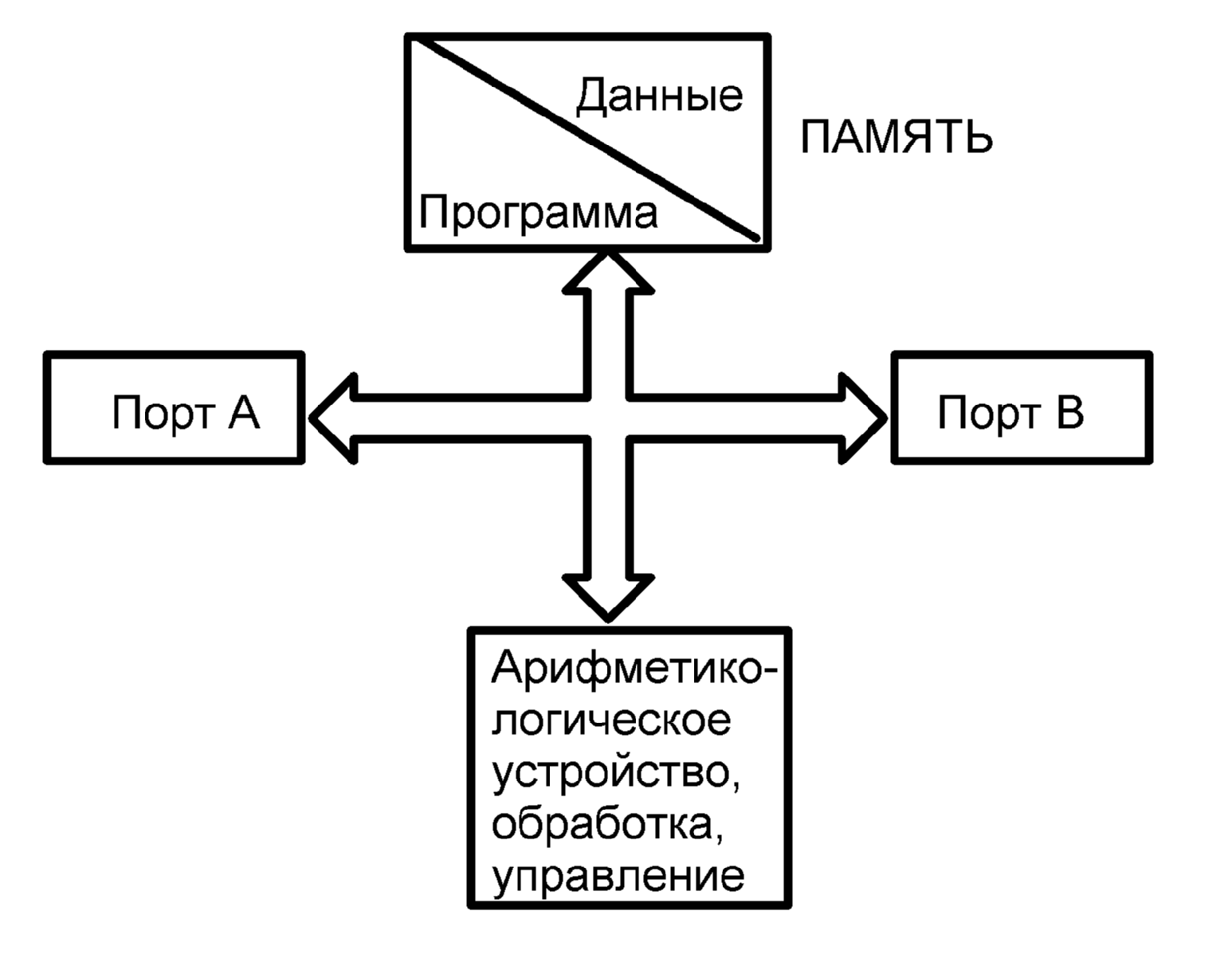

В процессе развития архитектура МК претерпела существенные изменения. Первые МК строились по так называемой Принстонской архитектуре (архитектуре фон Неймана) рис. 2.1, в которой память для команд и данных является общей. Эта архитектура имеет свои достоинства – простоту, возможность оперативного перераспределения памяти между областями хранения команд и данных и др. Недостаток – последовательная во времени выборка из памяти команд и данных, передаваемых по одной и той же системной шине, что ограничивает производительность МК. Тем не менее в силу своих достоинств Принстонская архитектура не только длительное время доминировала в микропроцессорной технике, но и сохранила свои позиции до настоящего времени.

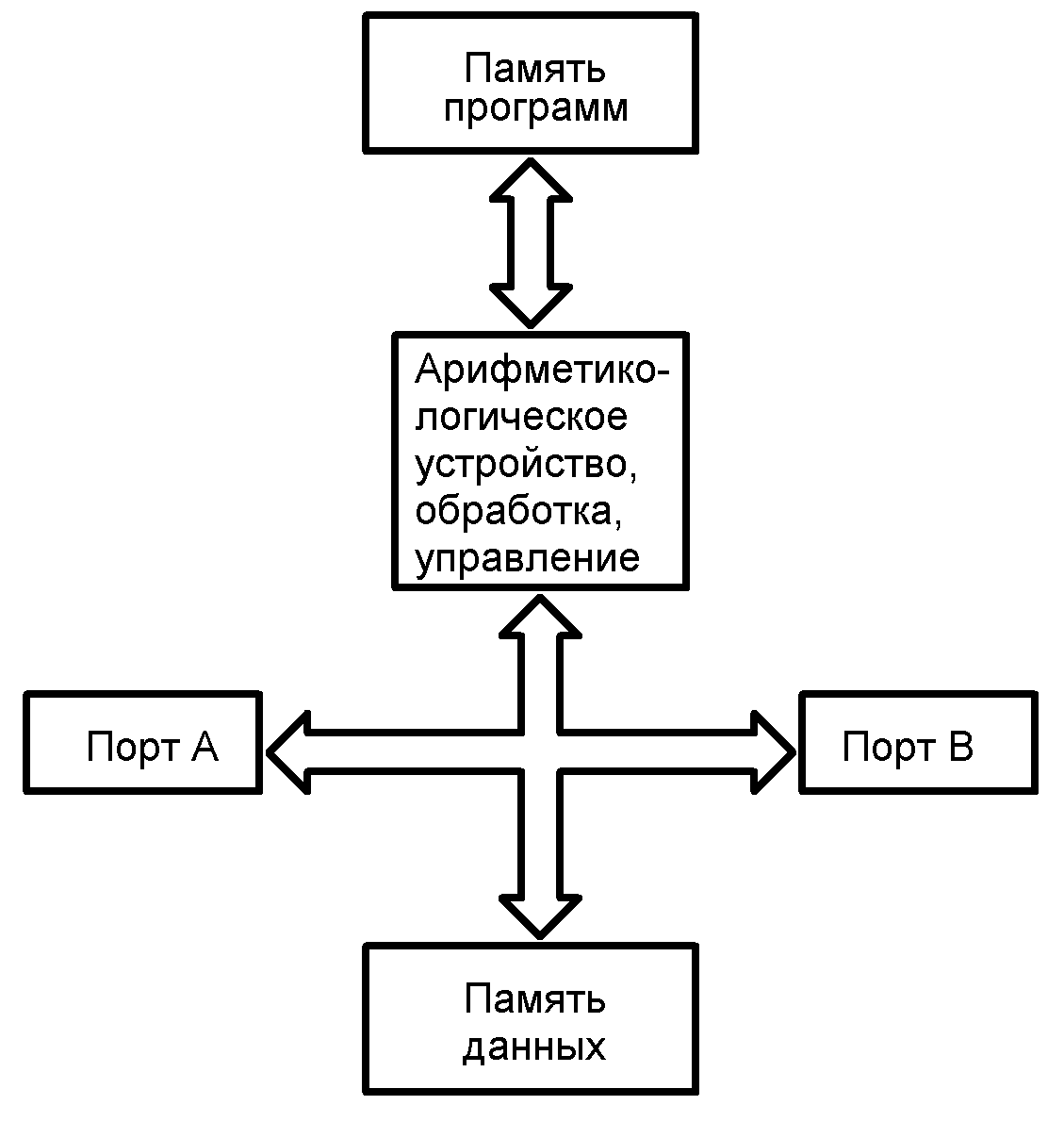

В Гарвардской архитектуре (рис. 2.2) память команд и память данных разделены, причем каждая из них имеет собственную шину для общения с процессором.

Рис.2.1. Фон-Неймановская архитектура МК

При этом во время передач данных для выполнения текущей команды можно производить выборку и расшифровку следующей, что повышает производительность МК системы. Реализация системы по сравнению с Принстонской усложняется (в системе больше шин), ниже коэффициент использования памяти. Но в в МК системах высокой производительности и внутренних структурах высокопроизводительных МК Гарвардская архитектура находит широкое применение.

По другому архитектурному признаку, связанному с характером системы команд, МК делятся на:

- CISC - процессоры;

- RISC - процессоры;

- VLIW - процессоры.

МК CISC имеют так называемую полную систему команд (Complex Instruction Set Computer), т. е. большой набор разно форматных команд при использовании многих способов адресации. Архитектура CISC присуща классическим процессорам, она в силу многообразия команд (общее число команд составляет 100…200) позволяет применять эффективные методы решения задач, но, в тоже время, усложняет схему процессора и увеличивает его стоимость и в общем случае не обеспечивает

максимального быстродействия. Они характеризуются следующими особенностями:

Нефиксированным значением длины команды.

Исполнение операций, таких как загрузка в память, арифметические действия кодируется в одной инструкции.

Небольшим числом регистров, каждый из которых выполняет строго определенную функцию.

Рис. 2.2. Гарвардская архитектура МП

МК RISC имеют сокращенную систему команд (Reduse Instruction Set Computer), из которой исключены редко применяемые команды. Общее число команд находится в пределах 50…100. Первые RISС-процессоры были разработаны в начале 1980-х годов в Стэнфордском и Калифорнийском университетах США. Простая архитектура позволяет как удешевить МК, так и поднять тактовую частоту.

Характерные особенности МК RISC:

Фиксированная длина машинных инструкций (например, 32 бита) и простой формат команды.

Одна инструкция выполняет только одну операцию с памятью — чтение или запись. Операции вида «прочитать-изменить-записать» отсутствуют.

Большое количество регистров общего назначения (32 и более).

Многие ранние RISC-МК даже не имели команд умножения и деления.

Форматы команд, по крайней мере подавляющее их большинство, идентичны (например, все команды имеют длину 4 байта), резко уменьшено число используемых способов адресации. Данные, как правило, обрабатываются только с регистровой или непосредственной адресацией. Значительно увеличено число регистров процессора, что позволяет редко обращаться к внешней памяти, а это повышает быстродействие. Идентичность временных циклов выполнения команд позволяет проще организовывать конвеерные методы обработки информации.

Существуют промежуточные решения между CISC и RISC – процессорами, например МК AVR фирмы Atmel, являющихся очень популярными у разработчиков в настоящее время. Они имеют Гарвардскую архитектуру и достаточно развитую, хотя и усеченную систему команд. В частности в их арсенале насчитывается до 133 инструкций, что соответствует CISC. С другой стороны большинство инструкций выполняются за один такт, в отличие от CISC МК с Принстонской архитектурой, где на выполнение одной инструкции требуется минимум 12 тактов. Поэтому, если считать что для исполнения некоторых CISC инструкций потребуется выполнение до 3 команд RISC, быстродействие МК AVR более чем в 4 раза превышает быстродействие классических МК с Принстонской архитектурой. Фактически микропроцессоры AVR стали индустриальным стандартом.

Последними по времени (менее 10 лет назад) появились VLIW - процессоры (Very Long Instruction Word), особенность которых состоит в использовании очень длинных команд (16 байт и более). Отдельные поля длинной команды определяют несколько подлежащих реализации микроопераций, которые могу выполняться параллельно во времени в нескольких операционных устройствах процессора. Таким образом, длинная команда определяет сразу группу микроопераций. VLIW процессоры считаются перспективными для высокопроизводительных систем.

Большое многообразие производимых МК не позволяет рассмотреть их все в рамках данного курса. Поэтому ограничимся рассмотрением наиболее популярных микропроцессоров фирмы Atmel с CISC архитектурой MCS-51 и RISC архитектурой AVR.