- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

6.2. Формирователи сигналов

При работе с цифровыми устройствами достаточно часто требуется формировать импульсы определённой длительности. Эту задачу выполняют специальные устройства - формирователи импульсов.

6.2.1. Укорачивающие формирователи

Рассмотрим схему, приведённую на рис. 6.8.

Рис. 6.8. Схема укорачивающего формирователя.

Временные диаграммы сигналов на входе и выходе инвертора, а также на выходе схемы "И" приведены на рис. 6.9.

Как видно из этих временных диаграмм, формирователь, схема которого приведена на рис. 6.8, вырабатывает одиночный импульс по фронту входного сигнала. Длительность

Рис. 6.9. Временные диаграммы укорачивающего формиователя.

импульса на выходе такой схемы будет равна времени задержки инвертора.

Если требуется длительность выходного импульса, большая времени задержки одиночного инвертора, то можно применить дополнительные элементы задержки на пассивных RC элементах. Пример подобной схемы приведён на рис. 6.10, а временные диаграммы этой схемы - на рис. 6.11.

Рис. 6.11. Схема укорачивающего формирователя с использованием RC элементов задержки.

Длительность

выработанного формирователем импульса

можно вычислить исходя из условия

разряда конденсатора С1. Действительно,

пока конденсатор С1 разряжается до

уровня порогового напряжения Uпор на

его выходе поддерживается уровень

логического нуля. С течением времени

напряжение на конденсаторе C1 становится

равным Uпор

и на выходе элемента И-НЕ появится

уровень логической единицы. Если считать,

что напряжение до начала разряда на

конденсаторе было равно напряжению

уровня уровень логической единицы

![]() ,

то изменение напряжения

,

то изменение напряжения

![]() с течением времени можно представить

как:

с течением времени можно представить

как:

![]() ,

,

следовательно

.

.

Длительность импульса равна времени разряда конденсатора до порогового значения Uпор будет равна:

Рис. 6.12. Временные диаграммы укорачивающего формирователя с использованием RC элементов задержки.

6.2.2. Расширяющие одновибраторы

В расширяющих одновибраторах (заторможенных мультивибраторах) длительность входного (запускающего) импульса должна быть короче длительности формируемого импульса.

Схема расширяющего одновибратора приведена на рис. 6.13. Он выполнен на двух логических элементах. Схема охвачена положительной обратной связью, так как выход второго элемента соединен с входом первого.

Рис. 6.13. Схема расширяющего одновибратора.

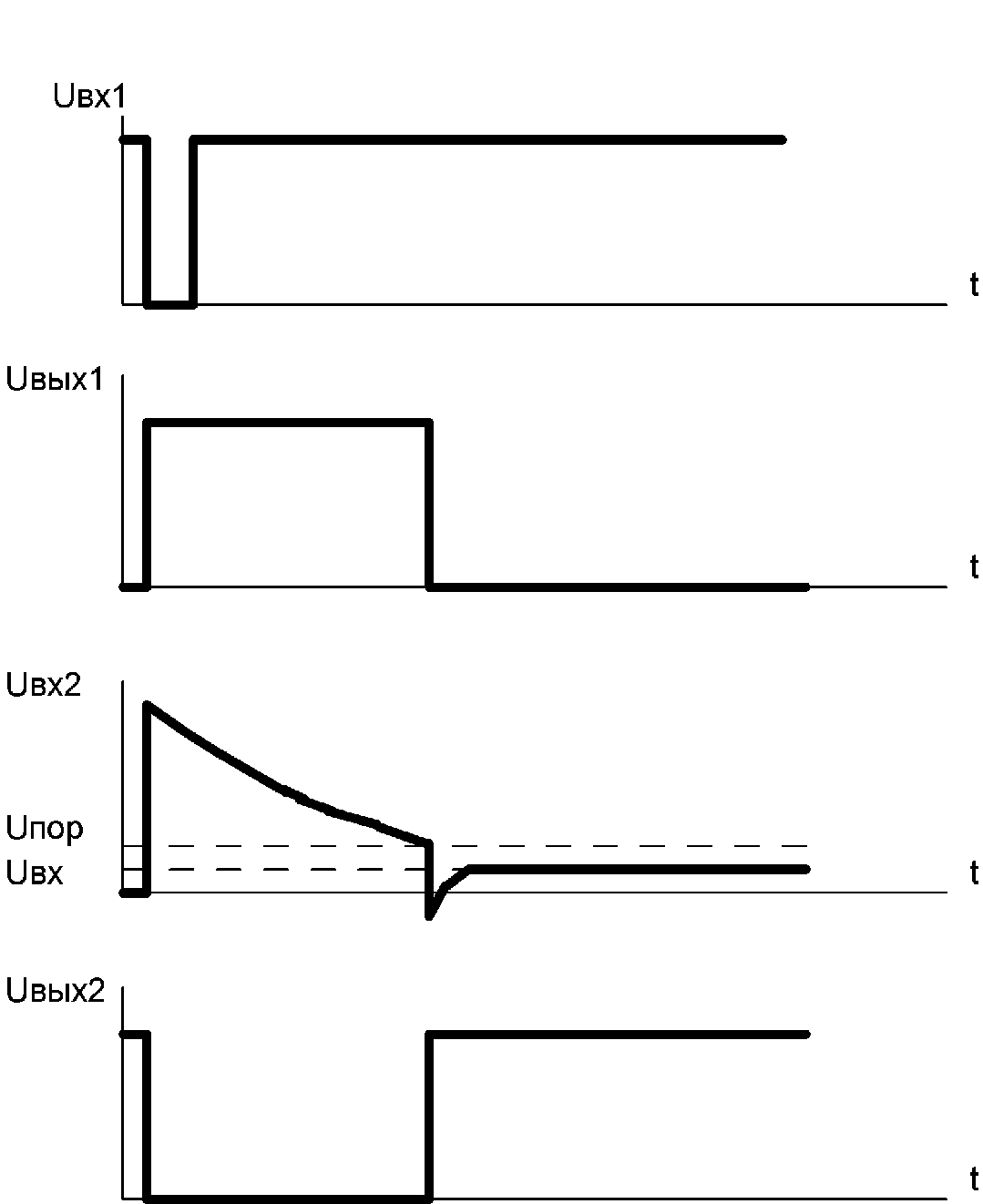

В исходном состоянии на выходе элемента DA2 (рис. 6.14) имеется уровень логической единицы, а на выходе элемента DA1 - уровень логического нуля, так как на обоих его входах присутствуют логические единицы.

Рис. 6.14. Временные диаграммы работы расширяющего одновибратора

При поступлении на вход запускающего импульса с нулевым потенциалом на выходе первого элемента появится уровень логической единицы, который через конденсатор С1 поступит на вход второго элемента. Элемент DA2 инвертирует этот сигнал и уровень “0” по цепи обратной связи подается на второй вход элемента DA1. Теперь даже если на входе снова появится уровень логической единицы, на выходе элемента DA1 будет сохраняться высокое напряжение.

На выходе элемента DA2 уровень логического нуля будет присутствовать до тех пор, пока конденсатор C1 не зарядится до уровня Uc = U1 - Uпор, а напряжение на резисторе R1 не достигнет порогового уровня Uпор .

Длительность выходного импульса одновибратора может быть определена с помощью выражения

где Rвых - выходное сопротивление первого элемента. Uпор - пороговое напряжение логического элемента. Сопротивление резистора R1 выбирается из условия:

Основными недостатками рассмотренных схем являются ограничения, накладываемые на длительность входного сигнала. В частности, как следует из описания, длительность входного сигнала не может быть больше расчетной длительности выходного. Поэтому были разработаны и выпускаются промышленностью мультивибраторы у которых на длительность входного сигнала не накладывается ограничений (К555АГ1, К555АГ3). Их принцип действия подобен рассмотренному. Отличие заключается в наличии в составе схемы R-S триггера, обеспечивающего дополнительные возможности.