- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

5.4. Перепрограммируемые постоянные запоминающие устройства

В EPROM (РПЗУ-УФ) - информация стирается ультрафиолетовыми лучами, а в E2PROM (РПЗУ-ЭС) - электрическими сигналами.

Запоминающими элементами (современных) РПЗУ являются транзисторы типов МНОП (метал-нитрид-окисел-полупроводник) и ЛИЗМОП (лавинная инжекция заряда). Упрощенное устройство МНОП транзистора приведено на рис. 5.14.

Рис. 5.14. Устройство МНОП транзистора

Над каналом расположен тонкий слой оксида кремния Si02 (<5 нм), далее идет толстый слой нитрида кремния Si3N4 и А1 затвор. Благодаря туннельному эффекту носители заряда могут проходить через тонкую пленкуSi02. Они скапливаются на границе раздела Si02-Si3N4, где возникают центры захвата заряда. Этот заряд и является носителем информации, хранимой МНОП-транзистором. Заряд записывают созданием под затвором напряженности электрического поля, достаточной для возникновения туннельного эффекта. Наличие заряда влияет на пороговое напряжение транзистора. Для него отрицательный заряд увеличивает пороговое напряжение (транзистор закрыт), а положительный заряд уменьшает пороговое напряжение (транзистор открыт). Заряды создаются при приложении напряжения на затвор (±U3) (+U3 создает отрицательные заряды, a -U, - положительные). Одно из состояний МНОП-транзистора принимается за «0», другое-за «1».

При программировании

используется напряжение около 20В.

После 104...

10![]() перезаписей МНОП-транзистор перестает

устойчиво хранить заряд.

перезаписей МНОП-транзистор перестает

устойчиво хранить заряд.

РПЗУ на МНОП-транзисторах энергонезависимы и могут хранить информацию десятками лет. Старая информация стирается записью нулей во все ЯП с помощью ультрафиолетового излучения (УФ).

Дальнейшее совершенствование РПЗУ привело к появлению РПЗУ на МОП-транзисторах с плавающим затвором (ЛИЗМОП-транзистор). Устройство такого транзистора приведено на рис. 5.15.

Рис. 5.15. Упрощенное устройство ЛИЗМОП-транзистора

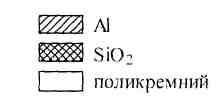

Транзисторы имеют плавающий затвор из поликремния. На рис. он является вторым, дополнительным к управляющему затвору.

Такие транзисторы используются в РПЗУ с УФ и электрическим стиранием (Flash memory).

Принцип работы: в плавающий затвор вводится заряд, влияющий на величину порогового напряжения. Он сохраняется там, в течении длительного времени.

При подаче напряжения на управляющий затвор, сток и исток импульса положительного напряжения 20...25 В в p-n-переходах возникает лавинный пробой, область которого насыщается электронами. Часть электронов с высокой энергией проникает через потенциальный барьер в плавающий затвор, где и сохраняется многие годы.

Отрицательный заряд плавающего затвора увеличивает пороговое напряжение настолько, что транзистор всегда закрыт.

При отсутствии заряда транзистор работает в обычном ключевом режиме.

Для стирания информации УФ лучами в корпусе делают окошко. УФ лучи вызывают фототоки и тепловые токи и заряды покидают плавающий затвор. Время стирания -десятки минут. Число циклов- 10... 100.

При электронном

стирании (ЭС) на затвор подается ноль

Вольт, а на сток и исток - высокое

напряжение. Число циклов

![]() .

.

ЭС стирание вытесняет УФ стирание. В настоящее время ведутся интенсивные исследования с целью увеличения объема памяти. Сейчас выпускаются микросхемы с объемом память несколько Гбайт.

Среди отечественных РПЗУ-УФ известна серия К573, а среди РПЗУ-ЭС -серии КР558 (n-МОП) и К1609, К1624, К1626 на ЛИЗМОП.