- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

5.1. Статические озу

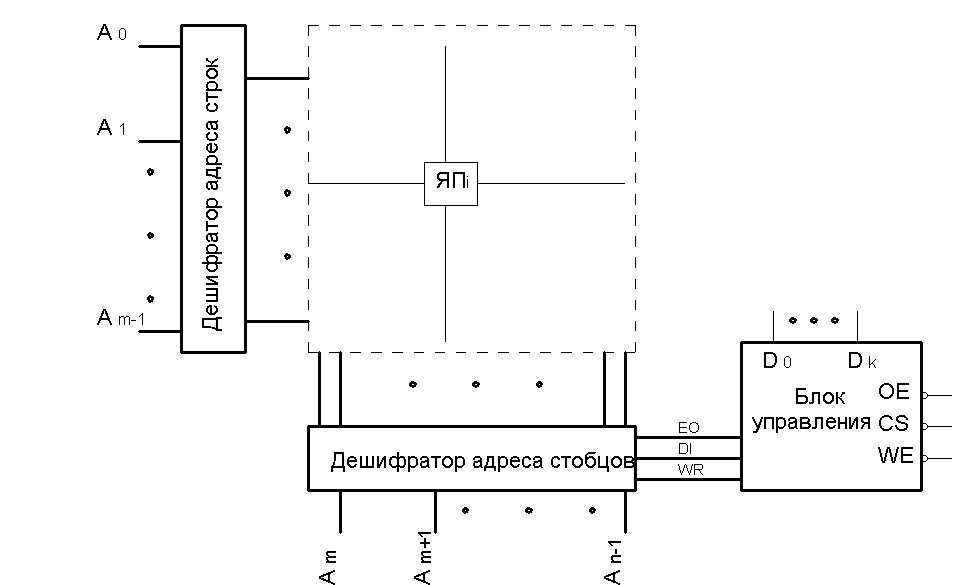

Типичный вариант структурного построения микросхемы статического ОЗУ приведен на рис. 5.1.

Рис.5.1. Структурная схема статического ЗУ 3D.

На рис. 5.1 приняты следующие обозначения:

-

![]() -

n

адресных

входов,

-

n

адресных

входов,

-

![]() -

вход разрешения считывания данных,

-

вход разрешения считывания данных,

-

![]() - вход выбора микросхемы,

- вход выбора микросхемы,

-

![]() - вход разрешения записи,

- вход разрешения записи,

-

![]() - вход/выход данных.

- вход/выход данных.

EO, DI, WR – внутренние сигналы, вырабатываемые блоком управления.

Доступ к ЯП матрицы накопителя осуществляется с помощью двух дешифратор адреса столбцов и строк.

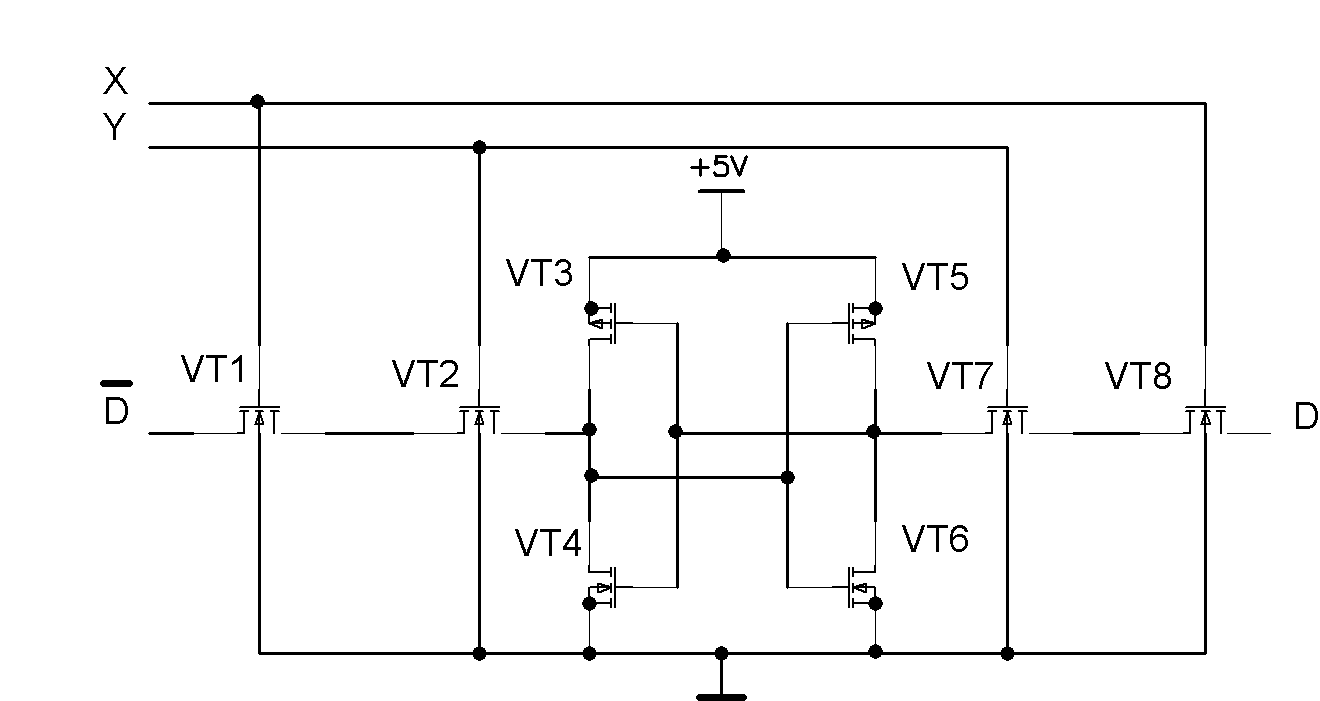

Упрощенная структурная схема элемента ЯП представлена на рис. 5.2.

Комплементарные транзисторы VT3…VT6 образуют триггер. Последовательно включенные транзисторы VT1, VT2 и VT7, VT8 образуют элементы И. В случае, если данная ячейка не выбрана (на обеих шинах X и Y или на одной из них установлен низкий уровень), ЯП находится в режиме хранения информации. При одновременном

появлении высокого уровня на обеих шинах X и Y данная ячейка оказывается выбранной и в зависимости от состояния входов , , производится запись

Рис. 5.2. Упрощенная структурная схема элемента ЯП статического ОЗУ

или считывание

лог. состояния ячейки. В частности, если

сигналы

(chip

select)

– выбор микросхемы низкого уровня ,

(output

enabled)

или RD

(read

data)

– переключения вход\выход - высокого

уровня,

(written

enabled)

или WR

(written

read)

– разрешения

записи низкого уровня, логический

уровень, установленный на информационном

входе D

микросхемы через специальные внутренние

буферные усилители записи блока

управления поступает на входы\выходы

![]() элемента ЯП. При этом, если состояние

триггера элемента ЯП не соответствует

приходящим сигналам, на его плечах на

короткое время устанавливается

напряжение равное примерно половине

напряжения питания, что не достаточно

для поддержания нижнего транзистора

одного из плеч в открытом состоянии,

этот транзистор закрывается и триггер

устанавливается в состояние соответствующее

приходящим сигналам.

элемента ЯП. При этом, если состояние

триггера элемента ЯП не соответствует

приходящим сигналам, на его плечах на

короткое время устанавливается

напряжение равное примерно половине

напряжения питания, что не достаточно

для поддержания нижнего транзистора

одного из плеч в открытом состоянии,

этот транзистор закрывается и триггер

устанавливается в состояние соответствующее

приходящим сигналам.

В случае необходимости считывания информации сигнал устанавливается низкого уровня, а сигнал - высокого уровня. При этом внутренние буферные усилители выходных сигналов внутри блока из третьего состояния переходят в активное состояние, а к входам\выходам элемента ЯП подключаются входы этих усилителей. Выходы внутренних буферных усилителей записи находятся при этом в третьем состоянии. И состояние триггера элемента ЯП передается на соответствующий вывод D микросхемы. В одной ЯП содержится k таких элементов.

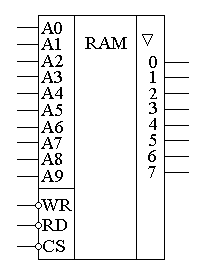

Пример условного обозначения ОЗУ на схемах электрических принципиальных приведен на рис. 5.3.

Рис. 5.3. Пример условного обозначения ОЗУ статического типа

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Статические ОЗУ применяются для построения микроконтроллерных схем из-за простоты построения принципиальной схемы и возможности работать на сколь угодно низких частотах, вплоть до постоянного тока. Кроме того, они применяются для построения КЭШ-памяти в универсальных компьютерах из-за высокого быстродействия статического ОЗУ.