- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

Дешифраторы

преобразуют двоичный код на входах

устройства в активный сигнал на том

выходе, номер которого равен десятичному

эквиваленту двоичного кода на входах.

В полном дешифраторе количество выходов

равно

![]() ,

где n

– число входов. В неполном дешифраторе

,

где n

– число входов. В неполном дешифраторе

![]() .

На схемах дешифраторы обозначаются DC

(от англ.

decoder).

Для целей расширения микросхемы

дешифратора обычно имеют дополнительный

вход EA(VA).

Так, например, таблица истинности для

полного двух разрядного (n=2)

дешифратора таблица истинности имеет

вид:

.

На схемах дешифраторы обозначаются DC

(от англ.

decoder).

Для целей расширения микросхемы

дешифратора обычно имеют дополнительный

вход EA(VA).

Так, например, таблица истинности для

полного двух разрядного (n=2)

дешифратора таблица истинности имеет

вид:

Таблица 4.2.

DEC число |

А1 |

А0 |

EA |

Y0 |

Y1 |

Y2 |

Y3 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

2 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

3 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

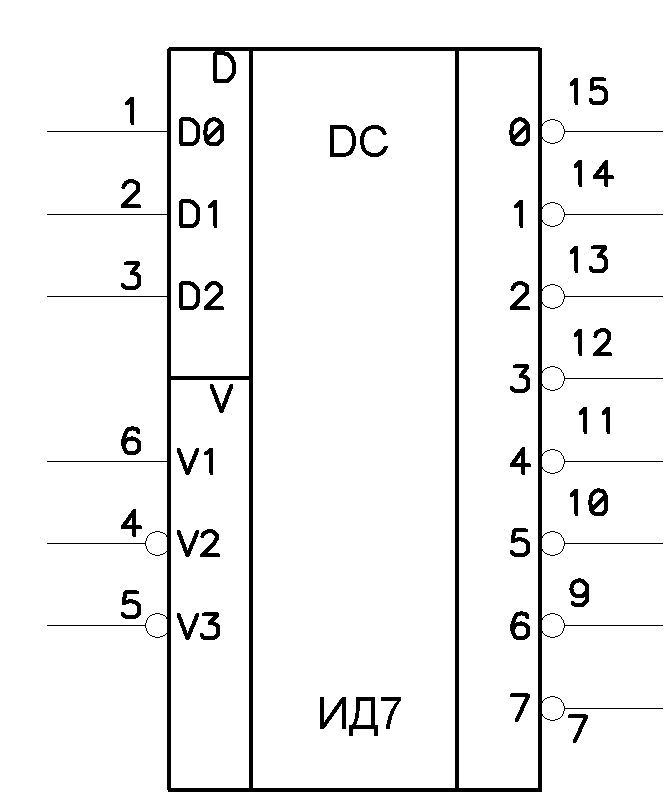

Пример условного обозначения трехразрядного дешифратора К555ИД7 приведен на рис. 4.21.

На этом обозначении

информационным входам А0…А2 соответствуют

вводы D0…D2,

а входу ОЕ – три входа

![]() .

Причем разрешающим состоянием входов

разрешения является одновременное

наличие лог. «1» на входе

.

Причем разрешающим состоянием входов

разрешения является одновременное

наличие лог. «1» на входе

![]() и лог. «0» на входах

и лог. «0» на входах

![]() .

Такое устройство микросхемы позволяет

без использования дополнительных

логических элементов производить

наращивание числа разрядов логического

устройства.

.

Такое устройство микросхемы позволяет

без использования дополнительных

логических элементов производить

наращивание числа разрядов логического

устройства.

Рис. 4.21. Пример условного обозначения на схемах электрических принципиальных дешифратора К555ИД7.

Как видно по своей структуре дешифраторы очень похожи на демультиплексоры, разница заключается в отсутствии в дешифраторах специального информационного входа. Поэтому, при использования дешифраторов в качестве демультиплексоров, информационным обычно служит один из входов разрешения.

Применяются также и неполные дешифраторы, например, для дешифрования тетрад двоично-десятичного кода, где число выходов равно десяти. Такое решение позволяет размещать устройства в корпусах с меньшим числом выводов.

Шифраторы выполняют

функцию обратную дешифраторам. Различают

неприоритетные и приоритетные шифраторы.

Например, для неприоритетного шифратора

![]() верна таблица истинности табл. 4.3.

верна таблица истинности табл. 4.3.

Таблица 4.3

№ |

X3 |

X2 |

X1 |

X0 |

Y1 |

Y0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

1 |

3 |

0 |

1 |

0 |

0 |

1 |

0 |

4 |

1 |

0 |

0 |

0 |

1 |

1 |

При этом остальные комбинации Х0…Х3 запрещены.

В приоритетном шифраторе производится преобразование максимального десятичного номера в двоичный код:

Таблица 4.4

№ |

X3 |

X2 |

X1 |

X0 |

Y1 |

Y0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

2 |

0 |

0 |

1 |

Х |

0 |

1 |

3 |

0 |

1 |

Х |

Х |

1 |

0 |

4 |

1 |

Х |

Х |

Х |

1 |

1 |

Знак Х в таблице 3.4 означает, что данная переменная может принимать как значение лог. «0» так и лог. «1».

Шифраторы применяются при формировании данных с клавиатур, в контроллерах прерывания микропроцессоров, параллельных аналого-цифровых преобразователях и т. п.

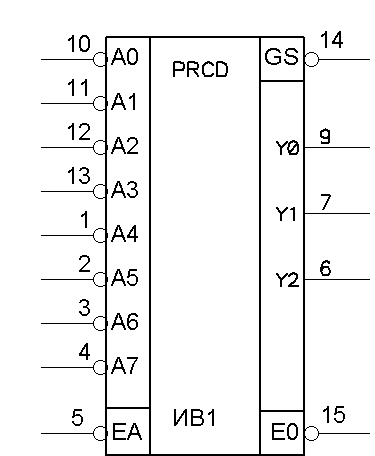

Пример условного обозначения приоритетного шифратора К155ИВ1 приведен на рис.4.22.

Рис. 4.22. Шифратор К155ИВ1.

В этой микросхеме кроме входа выбора ЕА имеются два выхода GS, E0, предназначенные для расширения шифратора на большее число разрядов. Сигнал лог. «0» на выходе GS появляется при одновременном наличии лог. «0» на входе ЕА и хотя бы на одном из входов А0…А7. Сигнал лог. «0» на выходе E0 появляется при одновременном наличии лог. «0» на входе ЕА и наличии лог. «1» на всех входах А0…А7.