- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

4.4.2. Мультиплексоры и демультиплексоры

Мультиплексором

называется логическое устройство,

которое имеет

![]() входов и один выход, где m-

число адресных входов, а 2

входов и один выход, где m-

число адресных входов, а 2![]() -

число информационных входов мультиплексора.

В

условных

графических изображениях мультиплексоры

обозначаются буквами MS,

MX,

MUX.

Условное графическое обозначение

сдвоенного четырех канального

мультиплексора К155КП2 приведено на рис.

4.16.

-

число информационных входов мультиплексора.

В

условных

графических изображениях мультиплексоры

обозначаются буквами MS,

MX,

MUX.

Условное графическое обозначение

сдвоенного четырех канального

мультиплексора К155КП2 приведено на рис.

4.16.

Рис. 4.16. Условное графическое изображение сдвоенного четырех канального мультиплексора К155КП2

Логическое уравнение для выхода Y будет иметь вид:

![]() .

(30)

.

(30)

Входы VA, VB используются при необходимости увеличения числа коммутируемых входов как показано на рис. 4.17.

Рис. 4.17. Пример схемы электрической принципиальной сдвоенного мультиплексора на 8 каналов на микросхемах К155КП2.

Входы VA, VB могут использоваться также и для других целей, например в качестве стробирующих для устранения эффекта гонок.

Демультиплексоры

выполняют функцию обратную

мультиплексированию, т. е. производят

коммутацию одного входного сигнала на

![]() выходов, где m

число адресных входов. Демультиплексоры

описываются системой логических

уравнений:

выходов, где m

число адресных входов. Демультиплексоры

описываются системой логических

уравнений:

![]() ;

;

![]() ,

,

где

![]() -

минтермы переменных,

-

минтермы переменных,

например, для n=2

и адресных входах

![]() :

:

В условных обозначениях демультиплексор обозначается буквами DMX, DM.

Основное назначение демультиплексоров – разделение последовательных потоков данных, например при использовании в системах с временным уплотнением каналов, цифровых АТС и т. п.. Условное графическое изображение демультиплексора приведено на рис. 4.18.

Рис.4.18. Условное графическое изображение четырехканального демультиплексора.

Следует отметить, что микросхемы демультиплексоров применяются редко, а наиболее часто в качестве демультиплексоров используются микросхемы дешифраторов – демультиплексоров, рассмотренные далее.

Мультиплексоры находят широкое применение и при создании СБИС, например для сокращения числа выводов микропроцессоров. Кроме основного назначения мультиплексоры могут использоваться для синтеза комбинационных схем.

Рассмотрим пример синтеза комбинационного автомата с использованием восьми канального мультиплексора. Пусть автомат выполняет логическую функцию, заданную таблицей истинности табл. 4.1.

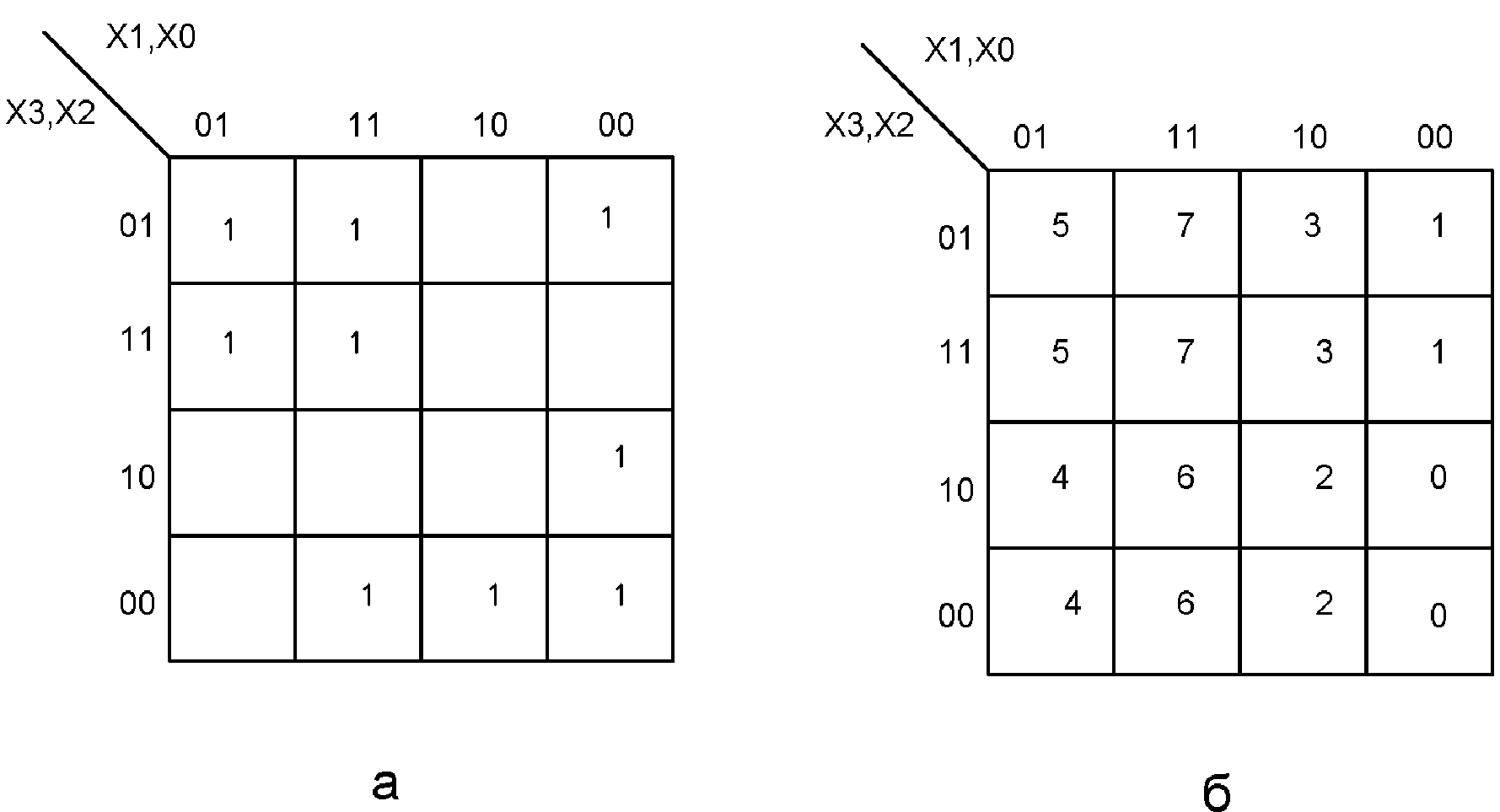

По этой таблице построена карта Карно рис. 4.19а. Правило выбора адресных переменных устанавливается из соображений, что для наиболее рационального использования адресных входов мультиплексора, им необходимо присваивать значения тех переменных, которые входят в ДНФ наибольшее число раз. Из таблицы Карно следует, что ДНФ функции Y имеет вид:

![]() ,

,

В этой формуле

наиболее часто встречаются

![]() ,

поэтому на адресный вход S3

подаем

,

поэтому на адресный вход S3

подаем

![]() ,

на адресный вход S2

подаем

,

на адресный вход S2

подаем

![]() и на адресный вход S1

можно подать как

и на адресный вход S1

можно подать как

![]() так и

.

Подадим на S3

.

Адреса, соответствующие такому выбору

указаны на карте рис. 4.19,б.

так и

.

Подадим на S3

.

Адреса, соответствующие такому выбору

указаны на карте рис. 4.19,б.

Таблица 4.1.

№ |

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

1 |

0 |

1 |

4 |

0 |

0 |

1 |

1 |

1 |

5 |

0 |

1 |

0 |

0 |

1 |

6 |

0 |

1 |

0 |

1 |

1 |

7 |

0 |

1 |

1 |

0 |

0 |

8 |

0 |

1 |

1 |

1 |

1 |

9 |

1 |

0 |

0 |

0 |

1 |

10 |

1 |

0 |

0 |

1 |

0 |

11 |

1 |

0 |

1 |

0 |

0 |

12 |

1 |

0 |

1 |

1 |

0 |

13 |

1 |

1 |

0 |

0 |

0 |

14 |

1 |

1 |

0 |

1 |

1 |

15 |

1 |

1 |

1 |

0 |

0 |

16 |

1 |

1 |

1 |

1 |

1 |

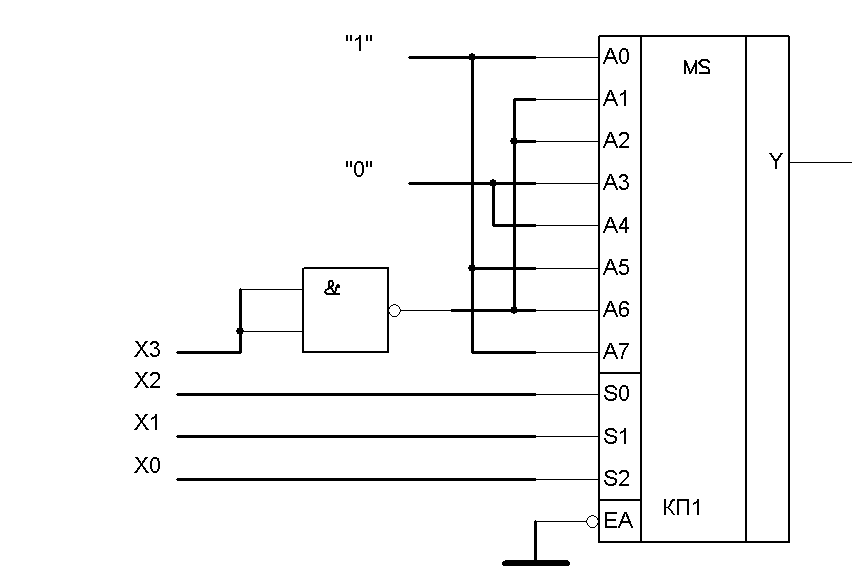

Сигналы, подаваемые на входы А0…А7 мультиплексора определим на основании рис.4.19 следующим образом:

- номерам входов соответствуют цифры, записанные в ячейках рис. 23б;

- на вход соответствующий адресу i подается лог. «1», если в обеих ячейках с адресом i в карте Карно записана «1».;

- на вход соответствующий адресу i подается лог. «0», если обе ячейки с адресом i в карте Карно пусты.;

- на вход соответствующий адресу i подается логический сигнал , если в ячейке с адресом i и соответствующей = 1 в карте Карно записана «1», а в ячейке с адресом i и соответствующей = 0 в карте Карно пустая ячейка;

- на вход

соответствующий адресу i

подается

логический сигнал

![]() ,

если в ячейке с адресом i

и соответствующей

=

0 в карте Карно записана «1», а в ячейке

с адресом i

и соответствующей

=

1 в карте Карно пустая ячейка;

,

если в ячейке с адресом i

и соответствующей

=

0 в карте Карно записана «1», а в ячейке

с адресом i

и соответствующей

=

1 в карте Карно пустая ячейка;

Рис. 4.19. Карта Карно и карта адресов комбинационного автомата.

На основании этих правил разработана схема автомата рис. 4.20.

В случае если комбинационный автомат одновременно реализует несколько логических функций, синтез производится аналогичным образом. Для каждой функции строятся карты Карно и ДНФ, затем путем сравнения ДНФ находятся наиболее часто встречающиеся переменные, которые подаются на адресные входы, причем каждой функции соответствует свой мультиплексор, а адресные входы мультиплексоров объединяются.

Рис.4.20. Схема комбинационного автомата с использованием восьми канального мультиплексора.