- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

4.3.5. Схемные особенности логических элементов

Рассмотренные логические элементы могут иметь некоторые схемотехнические особенности построения выходных каскадов. Рассмотрим основные из них на примере ТТЛ элементов, учитывая при этом, что подобные решения применяются и для логических элементов, выполненных с использованием других технологий. Наряду с базовым элементом И-НЕ, рассмотренным ранее, там, где не требуется высокого быстродействия, широко используются элементы И-НЕ с «открытым коллектором». Упрощенное схемное изображение этого элемента представлено на рис. 4.13.

Рис. 4.13. Упрощенная схема элемента 2И-НЕ с открытым коллектором

Этот элемент требует подключения внешней нагрузки, в качестве которой могут использоваться резистор, исполнительные устройства (реле, двигатели и т. п.), элементы индикации. Элементы с открытым коллектором допускают, в отличие от основной схемы параллельное соединение выходов с целью получения «монтажного ИЛИ».

Кроме элементов с открытым коллектором иногда используются логические элементы с «открытым эмиттером». Они обозначаются

знаком

![]() .

.

Вместе с элементами с двумя логическими состояниями используются элементы, имеющие третье (нейтральное) состояние. При переходе элемента в третье состояние, его выходное сопротивление становится очень большим и выход элемента не оказывает влияния на соединенные параллельно с ним входы и выходы других элементов. Такие элементы носят название тристабильных.

Упрощенная схема тристабильного элемента 2И-НЕ приведена на рис. 18.

Рис. 4.14. Упрощенная схема тристабильного элемента 2И-НЕ

Если сигнал ОЕ (Output Enable) низкого уровня, дополнительный транзистор закрыт и включенные встречно диоды не оказывают влияния на работу выходного каскада. Если сигнал ОЕ высокого уровня, дополнительный транзистор входит в состояние насыщения, закрывая транзисторы выходного каскада и логический элемент переходит в третье состояние.

Такие элементы используются там, где необходима передача информации по одной линии от нескольких источников к одному или нескольким приемникам (многоканальные системы уплотнения с временным уплотнением сигналов), а также при разработке микросхем сложных логических устройств, где один вывод микросхемы реализует несколько функций.

4.4. Сложные комбинационные цифровые автоматы

При разработке сложных логических устройств необходимо выполнять логические операции И, ИЛИ, НЕ над большим числом переменных. При этом использование простых логических элементов базовой логики, рассмотренных ранее ведет к значительному усложнению печатных плат, увеличению массогабаритных характеристик, снижению надежности. Поэтому для упрощения технической реализации, уменьшения числа внешних соединений были разработаны и производятся сложные комбинационные логические элементы. Некоторые из них, наиболее часто используемые, рассмотрены в этом разделе.

4.4.1. Сумматор по модулю два

Операция «сумма

по модулю 2» (исключающее ИЛИ, логическая

неравнозначность) обозначается символом

![]() и определяется соотношением:

и определяется соотношением:

![]() =

=![]()

![]() +

+![]() =(

+

=(

+![]() )

)![]() ,

(24)

,

(24)

Операция «сумма по модулю 2» коммутативна, ассоциативна и дистрибутивна относительно конъюнкции, т. е.

=![]() ,

(25)

,

(25)

![]() (26)

(26)

![]() (27)

(27)

Для операции «сумма по модулю 2» справедливы тождества:

![]()

![]()

![]() ,

,

![]() ,

(28)

,

(28)

![]() =

=![]() ,

(29)

,

(29)

Операция называется операцией исключающее ИЛИ-НЕ.

Логические элементы, выполняющие операцию исключающее ИЛИ и исключающее ИЛИ-НЕ, всегда имеют только два входа, т. е. операция выполняется только для двух переменных.

Таблица истинности для элемента исключающее ИЛИ выглядит следующим образом:

|

|

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Описание на языке VHDL имеет следующий вид:

Y<= (X1 xor X2)

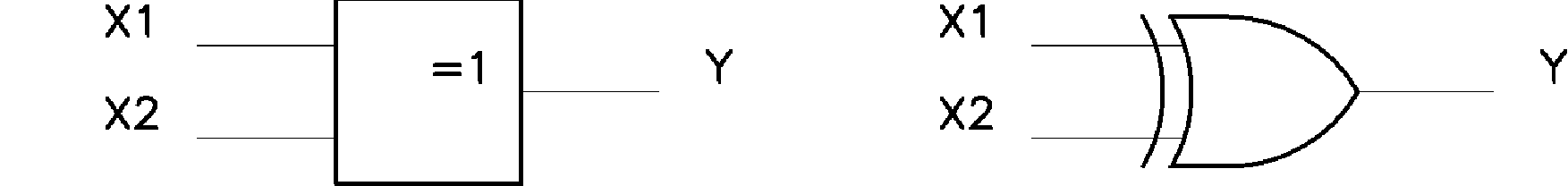

На рис. 4.15 показано условное графическое изображение элемента исключающее ИЛИ.

Рис.4.15 Условное графическое изображение элемента исключающее ИЛИ