- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

Цифровые микросхемы эмиттерно-связанной логики ЭТСЛ представляют собой транзисторные переключательные схемы с объединенными эмиттерами и обладают наибольшими по-сравнению с другими типами микросхем быстродействием и большой потребляемой мощностью. Большое быстродействие обусловлено тем, что в этих ключах биполярные транзисторы работают в ненасыщенном (линейном) режиме. На выходах ключей установлены эмиттерные повторители, ускоряющие процесс перезаряда емкости нагрузки. Уменьшение времени задержки достигается также и за счет уменьшения разности напряжений между лог. «0» и лог. «1», что, однако приводит к снижению помехоустойчивости.

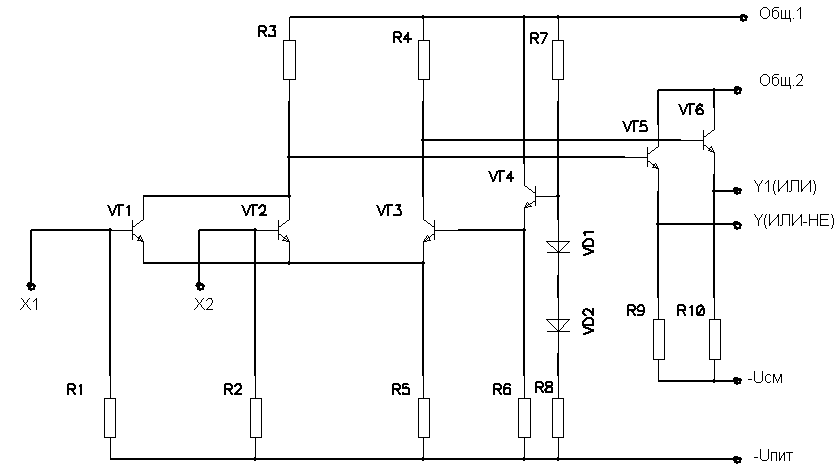

Рассмотрим принцип работы ЭТСЛ на примере базового логического элемента, выполняющего одновременно функции ИЛИ-НЕ и ИЛИ (рис. 4.9).

Схема состоит из

дифференциального усилителя на

транзисторах VT1…VT3.

В этом усилителе при подаче логических

уровней на входы Х1,

Х2 ток может

протекать либо через транзистор VT3

(когда на обеих входах установлено

напряжение логического «0» (U![]() =-1,65

В), либо через транзисторы VT1

или VT2

или оба вместе при подаче на

=-1,65

В), либо через транзисторы VT1

или VT2

или оба вместе при подаче на

один или оба входа

напряжения лог. «1» (U![]() =-0,96

В). Выходные эмиттерные повторители

VT5,VT6

подключаются к источнику смещения -2 В

через внешние резисторы 50 Ом. Когда

закрыт VT3

на выходе Y1

устанавливается напряжение

=-0,96

В). Выходные эмиттерные повторители

VT5,VT6

подключаются к источнику смещения -2 В

через внешние резисторы 50 Ом. Когда

закрыт VT3

на выходе Y1

устанавливается напряжение

-0,96 В, соответствующее лог. «1», а на выходе Y – напряжение -1,85 В,

Рис. 4.9. Схема электрическая принципиальная ЭТСЛ элемента ИЛИ-НЕ / ИЛИ

соответствующее лог. «0». Когда VT3 открыт, на выходе Y устанавливается напряжение -0,96 В, соответствующее лог. «1», а на выходе Y1 – напряжение -1,85 В, соответствующее лог. «0». Микросхемы ЭТСЛ при использовании совместно с ТТЛ, или КМОП микросхемами требуют применения специальных преобразователей уровня. Достаточно высокое входное сопротивление ЭТСЛ (~ 50 кОм), и низкое выходное, обуславливают высокий коэффициент разветвления (более 15).

Большая потребляемая мощность, наличие большого числа компонентов в логических элементах ограничивают применение ЭТСЛ в БИС и СБИС.

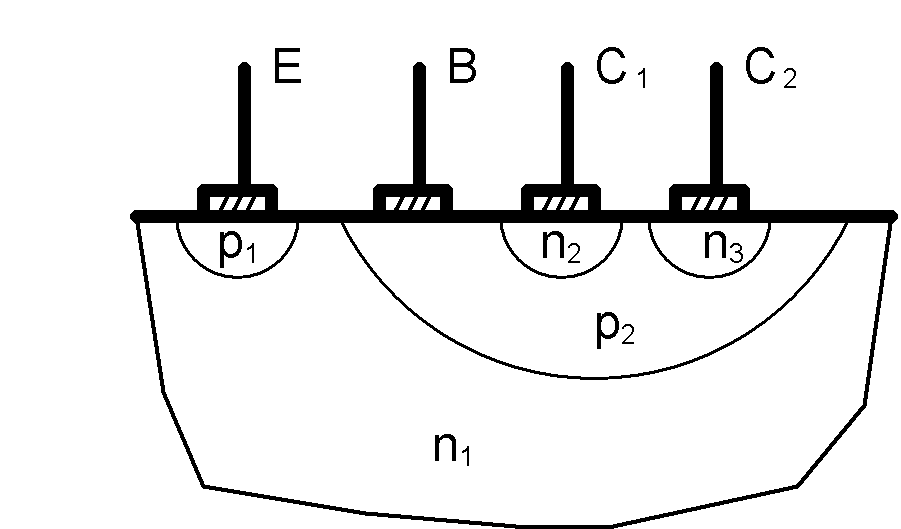

4.3.4. Инжекционные интегральные логические схемы (и2л)

Для повышения технологичности изготовления желательно при разработке ИС применять схемотехнические решения, использующие только однотипные элементы, например транзисторы. Этот путь, как было показано ранее, реализован в ИС МДП, что наряду с другими достоинствами является причиной их широкого распространения. Однако, как уже отмечалось, ключ на биполярных транзисторах на сегодняшний день обладает лучшими как ключевыми, так и частотными свойствами. Это является предпосылкой к постоянному поиску новых схемотехнических решений для реализации биполярных ИС. Такой поиск привел к почти одновременной разработке фирмами Philips и IBM элемента интегральной инжекционной логики (И2Л).

В основе И2Л схем лежат дна принципа схемотехники и технологии биполярных схем: 1) совмещение электрически связанных однородных областей полупроводника в кристалле ИС, что приводит к увеличению степени интеграции;

2) отказ от традиционного способа питания цепи базы и коллектора ключевых транзисторов через резисторы.

На рис. 4.10 показана инжекционная структура с дополнительным р — n-переходом. Если база (область р2) переключающего вертикального транзистора n2 — р2 — n1 -типа расположена вблизи прямосмещенного перехода р1—n1, то часть инжектированных данным переходом дырок попадает в область базы р2. В результате нарушения электронейтральности базы этого транзистора через переход база — эмиттер начинает протекать ток, смещающий этот переход в прямом направлении. Область р1, введенную для инжекции избыточных носителей, называют инжектором Е. Питание инжектора осуществляется от внешнего генератора тока или от источника напряжения через резистор (один внешний резистор).

Рис. 4.10. Упрощенная топология элемента И Л

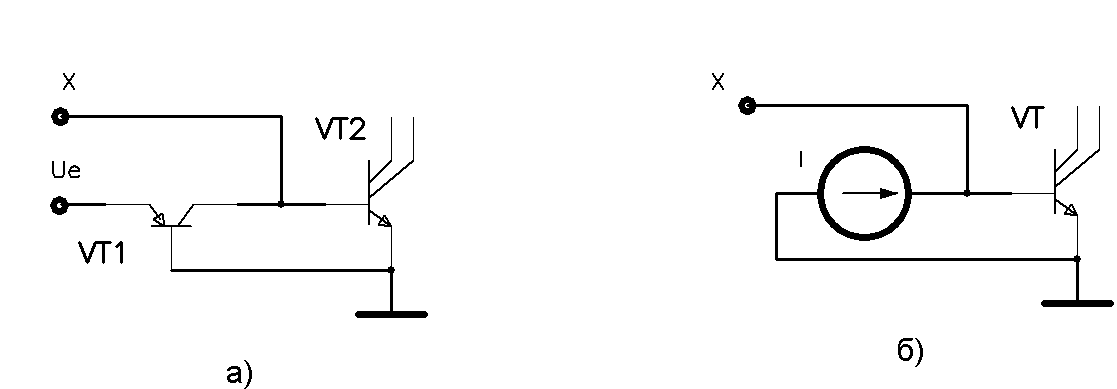

Рис. 4.11. Эквивалентная схема элемента И Л

Данную инжекционную структуру можно представить в виде схемы, содержащей два транзистора: токозадающий горизонтальный р1—n1—р2-типа (включен по схеме с общей базой) и переключающий вертикальный n2 — p2—n1-типа (рис. 4.11, а). Упрощенная эквивалентная схема состоит из транзистора n — p — n-типа и генератора тока I в цепи его базы (рис. 4.11,б). Обычно транзистор n — p — n-типа выполняется с несколькими коллекторами (область n3 на рис. 4.10).

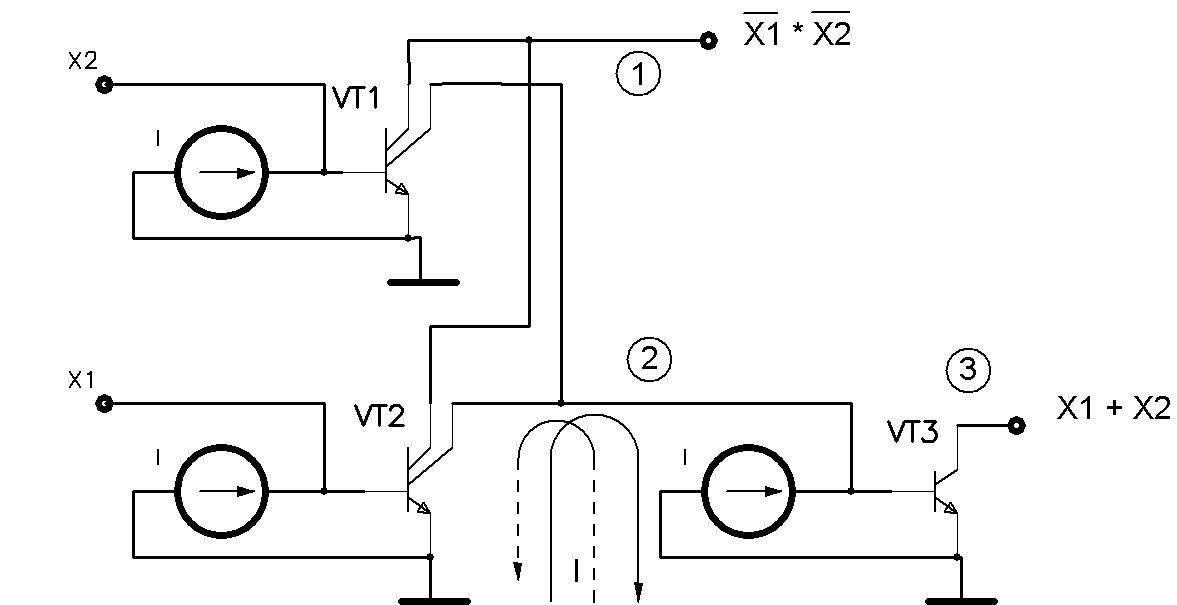

Когда транзисторы VT1 и VT2 закрыты, транзистор VT3 открыт током инжектора I (сплошная линия прохождения тока на рис. 4.12) и напряжение в узле 2 И2Л

U

=U![]() =0,75

В (лог. «1»)

=0,75

В (лог. «1»)

Рис. 4.12. Эквивалентная схема структуры И Л

что соответствует уровню логической 1. Если транзистор VT2 откроется, то ток инжектора VT3 переключится в цепь коллектора VT2 (пунктирная линия на рис. 4.12) и транзистор VT3 закроется. В узле 2 будет напряжение насыщения коллектора VT2:

U =U =0,05 В (лог. «0»).

Площадь, приходящаяся на один ЛЭ в схемах в И2Л, приблизительно в 10 раз меньше, чем в схемах ТТЛ. Применение диодов Шотки в схемах И2Л позволяет без увеличения потребляемой мощности получить еще более высокое быстродействие.

Высокое быстродействие элементов И2Л при малой потребляемой мощности объясняется незначительными паразитными емкостями, отсутствием накопления заряда и очень небольшой разницей логических уровней. Типичное время задержки составляет 10 нс, а использование структур И Л с диодами Шотки позволяет получить время задержки менее 0,1 нс.