- •Цифровые устройства

- •Введение.

- •1. Основные принципы цифровой электроники.

- •1.1. Аналоговые и цифровые сигналы

- •1.2. Модели и уровни представления цифровых устройств

- •1.3. Входы и выходы цифровых микросхем

- •1.4. Основные обозначения на схемах

- •1.5. Серии цифровых микросхем

- •1.6. Корпуса цифровых микросхем

- •2.1. Системы счисления.

- •2.2 Арифметические операции над двоичными числами.

- •2.3. Машинное представление информации

- •2.3.1 Формы представления чисел.

- •2.3.2. Буквенно-цифровой код

- •2.3.3 Восьмисегментный код

- •3. Логические основы цифровой техники

- •3.1 Основные законы алгебры логики

- •3.2 Формы описания логических функций и их использование для синтеза логических схем

- •3.3. Синтез комбинационных схем с несколькими выходами

- •3.4. Понятие логического базиса

- •4. Логические элементы цифровых устройств

- •4.1 Общие характеристики элементов цифровых устройств

- •4.2. Переходные процессы в логических схемах

- •4.3. Описание основных схемотехнических решений базовых логических элементов.

- •4.3.1. Интегральные схемы ттл и ттлш

- •4.3.2. Интегральные микросхемы на моп-структурах

- •4.3.3. Микросхемы эмиттерно-связанной транзисторной логики

- •4.3.4. Инжекционные интегральные логические схемы (и2л)

- •4.3.5. Схемные особенности логических элементов

- •4.4. Сложные комбинационные цифровые автоматы

- •4.4.1. Сумматор по модулю два

- •4.4.2. Мультиплексоры и демультиплексоры

- •4.4.3. Дешифраторы, дешифраторы-демультиплексоры, шифраторы

- •4.4.4. Преобразователи кодов

- •4.4.5. Сумматоры

- •4.5. Последовательностные схемы цифровых автоматов

- •4.5.1. Асинхронный r-s триггер

- •4.5.2. Синхронный r-s триггер

- •4.5.3. Синхронный d - триггер со статическим управлением

- •4.5.3. Синхронный d - триггер с динамическим управлением

- •4.5.4. Универсальный j-k триггер

- •4.5.6. Регистры

- •4.5.7. Счетчики

- •Полупроводниковые запоминающие устройства

- •5.1. Статические озу

- •5.2. Динамические озу

- •5.3. Однократно программируемые постоянные запоминающие устройства

- •5.4. Перепрограммируемые постоянные запоминающие устройства

- •Специальные элементы цифровых устройств

- •6.1. Автоколебательные генераторы на логических элементах

- •6.2. Формирователи сигналов

- •6.2.1. Укорачивающие формирователи

- •6.2.2. Расширяющие одновибраторы

- •6.2.3. Триггер Шмитта

- •6.2.4. Аналоговый компаратор

- •Преобразователи сигналов

- •7.1. Цифроаналоговые преобразователи

- •7.1.1. Цап с матрицей r-2r

- •7.1.2. Цап с матрицей звездообразного типа

- •7.2. Аналого-цифровые преобразователи

- •Ацп двойного интегрирования (интегрирующий ацп).

- •Сигма-дельта ацп.

- •Преобразователи напряжение-частота

- •8. Элементы цифровой индикации

- •Малогабаритные лампочки накаливания

- •Светодиодные индикаторы.

- •Жидкокристаллические индикаторы

- •Дисплеи на основе органических пленок (oled)

- •Динамическая индикация

- •Микропроцессоры Введение

- •1. Классификация микропроцессоров

- •2. Архитектура микроконтроллера

- •2.1 Основные характеристики микроконтроллера

- •2.2. Архитектура микроконтроллеров

- •2.2.1. Архитектура микроконтроллеров mcs-51

- •Альтернативные функции порта p3

- •2.2.2. Архитектура avr микроконтроллеров

- •3. Программирование микроконтроллеров

- •3.1 Языки программирования для микроконтроллеров

- •3.2. Виды компиляторов

- •3.3.1 Форматы и способы адресации данных

- •3.3.2. Форматы и способы адресации команд

- •3.3.3. Команды пересылки информации

- •3.3.4. Команды поразрядной обработки информации

- •3.3.5. Команды арифметических операций

- •3.3.6. Управляющие команды

- •3.3.7. Порядок выполнения прерываний в микроконтроллерах семейства mcs51.

- •3.3.8. Применение подпрограмм при программировании.

- •3.3.9. Директивы ассемблера для микроконтроллеров семейства mcs-51

- •3.3.10. Применение комментариев

- •3.3.11. Многофайловые программы.

- •3.3.12. Отладка программ.

- •3.3.13. Способы отладки программ.

- •Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы

- •4.1. Программируемые логические матрицы и программируема матричная логика

- •4.3. Базовые матричные кристаллы

- •4.4. Бис/сбис с программируемыми структурами (cpld, fpga, смешанные структуры)

- •Список использованной литературы

3.4. Понятие логического базиса

Любую сколь угодно сложную логическую функцию можно реализовать с помощью элементарных логических функций И, ИЛИ, НЕ. Поэтому эта система функций называется функционально полной или логическим базисом. Следует заметить, что базис И, ИЛИ, НЕ является не единственным. Например, кроме нее можно предложить еще следующие системы логического базиса:

- И, НЕ;

- ИЛИ, НЕ;

- И-НЕ (штрих Шеффера);

-ИЛИ-НЕ (стрелка Пирса).

Недостающие в системах логические функции получаются применением Булевых уравнений. При практической реализации логических функций, при выборе логического базиса руководствуются простотой реализации. Наиболее часто используется базис И-НЕ.

4. Логические элементы цифровых устройств

Элементы цифровых устройств – наименьшие функциональные части, на которое разбивается устройство при его проектировании и технической реализации. Они выполняют логические и вспомогательные функции. Компонентами элементов являются интегральные микросхемы, транзисторы, диоды, резисторы, конденсаторы, индуктивности и пр.

4.1 Общие характеристики элементов цифровых устройств

Основой построения цифровых устройств являются электронные ключи, обладающие тем свойством, что могут находиться в одном из двух состояний и их действие заключается в переходе из одного состояния в другое под воздействием входных сигналов. При этом существуют взаимно однозначные соответствия входных и выходных сигналов, например, высокий или низкий уровень напряжений или тока, отсутствие или присутствие импульса. Большинство ключей относятся к потенциальным, т. к. сигналы на их входах и выходах представляют собой высокий и низкий уровни напряжений. При положительной логике высокому уровню напряжения ставится в соответствие лог. «1», а низкому лог. «0». При отрицательной логике – наоборот.

Параметры цифровых устройств подразделяются на статические и динамические:

К статическим параметрам относятся:

- входное U![]() и

выходное U

и

выходное U![]() напряжения логического 0;

напряжения логического 0;

- входное U![]() и

выходное U

и

выходное U![]() напряжения

логической 1;

напряжения

логической 1;

- входной

![]() I

и выходной I

токи логического 0;

I

и выходной I

токи логического 0;

- входной I и выходной I токи логического 1;

- коэффициент

разветвления по выходу К![]() ,

определяющий число входов логических

элементов, которые одновременно можно

подключить к данному выходу;

,

определяющий число входов логических

элементов, которые одновременно можно

подключить к данному выходу;

- коэффициент

объединения по входу К![]() ,

определяющий число входов логического

элемента, по которым реализуется данная

логическая функция;

,

определяющий число входов логического

элемента, по которым реализуется данная

логическая функция;

- допустимое

напряжение статической помехи U![]() ,

характеризующее статическую

помехоустойчивость элемента, т. е.

Способность противостоять воздействию

мешающего сигнала, длительность которого

превышает длительность переключения

микросхемы;

,

характеризующее статическую

помехоустойчивость элемента, т. е.

Способность противостоять воздействию

мешающего сигнала, длительность которого

превышает длительность переключения

микросхемы;

- средняя потребляемая мощность, определяемая выражением:

P=0,5(P![]() +P

+P![]() ),

(19)

),

(19)

где P и P - мощности, потребляемые элементом в состоянии логического 0 и логической 1.

Статические

параметры определяются с помощью

статических характеристик, которые

снимаются при медленных изменениях

токов и напряжений. К статическим

характеристикам относятся: передаточная

U![]() =f(U

=f(U![]() )

при I

=0,

обратной

связи U

=f(U

),

при I

=0,

входная

I

=f(U

),

при I

=0

и выходная

I

=f(U

),

при I

=0.

Характеристика

обратной связи практически не используется,

т. к. у логических элементов выходной

сигнал, поступающий на вход, очень мал

и не оказывает заметного влияния на

работу устройства.

)

при I

=0,

обратной

связи U

=f(U

),

при I

=0,

входная

I

=f(U

),

при I

=0

и выходная

I

=f(U

),

при I

=0.

Характеристика

обратной связи практически не используется,

т. к. у логических элементов выходной

сигнал, поступающий на вход, очень мал

и не оказывает заметного влияния на

работу устройства.

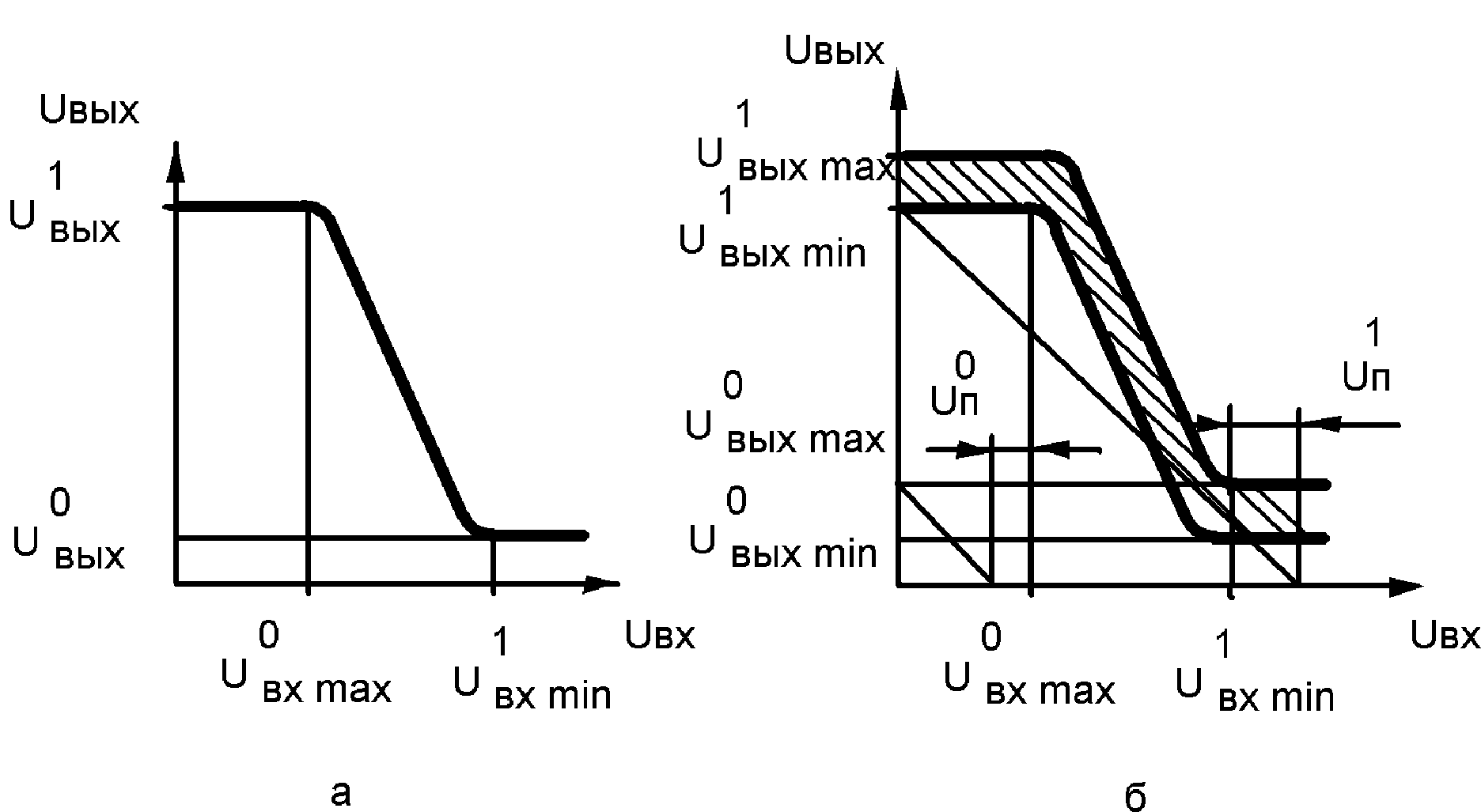

На рис. 4.1, а показана передаточная характеристика инвертирующих логических элементов, например И-НЕ, ИЛИ-НЕ, в предположении, что их характеристики идентичны. Поскольку реальные элементы имеют разброс за счет различия в параметрах элементов, входящих в состав устройства, реальные передаточные характеристики могут отличаться и представляют не одну кривую, а их совокупность. Это на графике представляется некоторой областью, ограниченной двумя кривыми (рис. 4.1, б).

Рис. 4.1 Передаточная характеристика инвертирующего элемента.

При этом U![]() и

U

и

U![]() -

максимальный и минимальный уровни

выходного сигнала, которые имеются хотя

бы у одного элемента данного типа.

Аналогично рассматриваются U

-

максимальный и минимальный уровни

выходного сигнала, которые имеются хотя

бы у одного элемента данного типа.

Аналогично рассматриваются U![]() и

U

и

U![]() .

.

На этих же графиках отмечены уровни входных сигналов:

- U![]() такой уровень,

при котором ни один элемент данного

типа не переключается из «1» в «0»;

такой уровень,

при котором ни один элемент данного

типа не переключается из «1» в «0»;

- U уровень входного сигнала, при котором на выходе любого элемента данного типа сохраняется «0».

По передаточной характеристике можно определить запасы помехоустойчивости. Достаточно провести прямые под углом 45º от точек пересечения уровней U и U с осью ординат до пересечения с осью абсцисс.

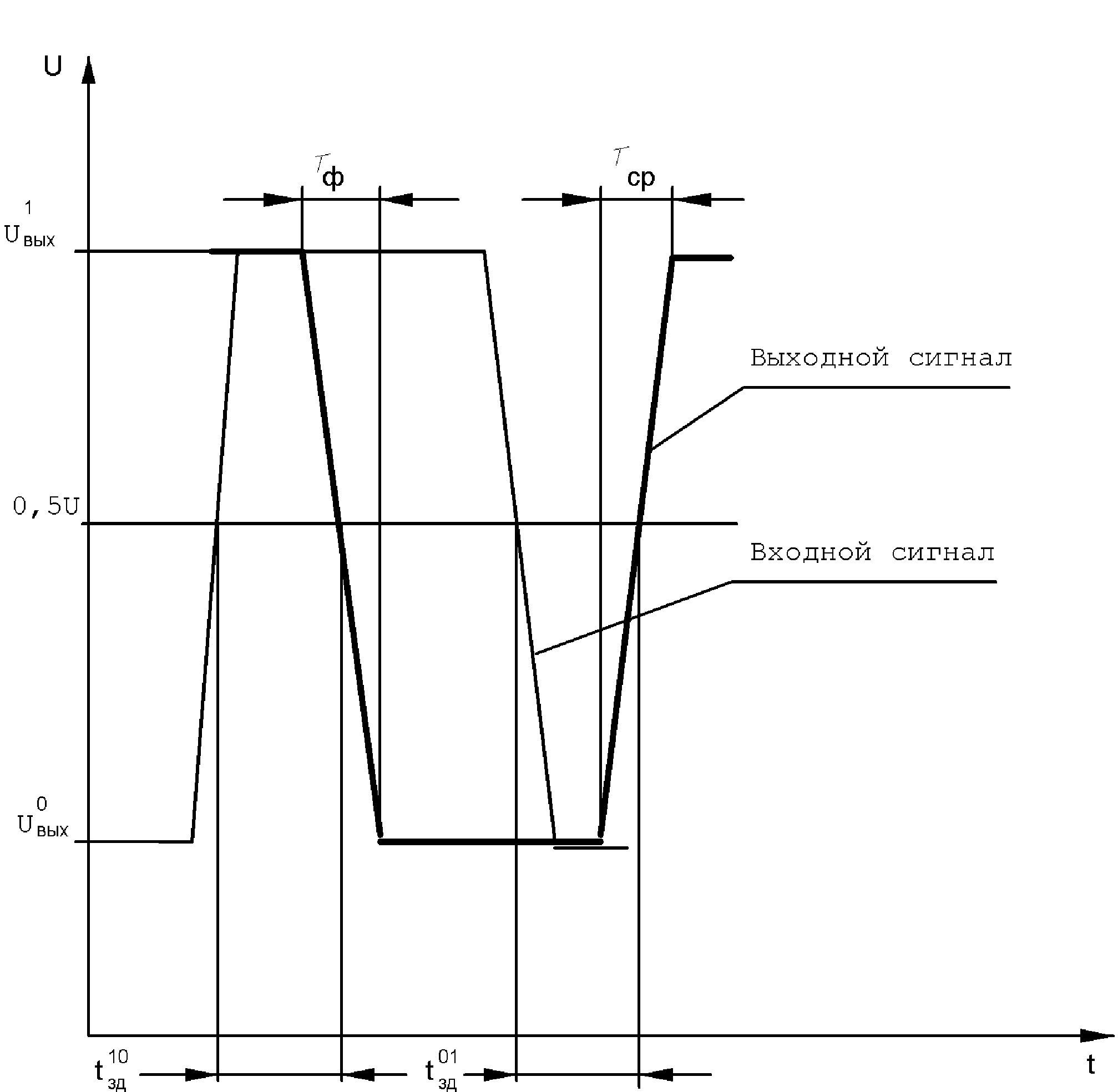

Кроме статических существуют динамические параметры логических элементов.

Процесс изменения напряжения от низкого уровня к высокому называют положительным фронтом сигнала, а обратный процесс – отрицательным фронтом сигнала. Если необходимо учитывать их взаимное временное расположение, ранее следующий процесс называют передним фронтом или просто фронтом, а последующий – задним фронтом или срезом.

К динамическим параметрам, характеризующим свойства логического элемента относятся:

- время задержки

сигнала t![]() - интервал

времени между входным и выходным

сигналами, при переходе U

- интервал

времени между входным и выходным

сигналами, при переходе U![]() элемента от

U

до

U

,

измеренный

на уровне 0,5 размаха напряжения;

элемента от

U

до

U

,

измеренный

на уровне 0,5 размаха напряжения;

- время задержки

сигнала t![]() - интервал

времени между входным и выходным

сигналами, при переходе U

элемента от

U

до

U

,

измеренный

на уровне 0,5 размаха напряжения;

- интервал

времени между входным и выходным

сигналами, при переходе U

элемента от

U

до

U

,

измеренный

на уровне 0,5 размаха напряжения;

- среднее время задержки:

t![]() =0,5(t

+

t

).

(20)

=0,5(t

+

t

).

(20)

Рис. 4.2 Динамические параметры логического элемента.

- длительность

фронта и среза выходного напряжения

логического элемента, при подаче на его

вход прямоугольного импульса из «0» в

«1» и обратно - τ![]() и

τ

и

τ![]() .

.

Приведенные параметры иллюстрируются рис. 4.2.