- •Введение

- •Часть 1. Основы теории автоматического управления

- •Глава 1. Принципы построения автоматизированных производств

- •1.1. Автоматизация производства

- •1.2. Основные термины и определения автоматизированных производств

- •1.3. Конструкторская документация - схемы систем автоматики

- •Глава 2. Принципы построения сау и режимы ее работы

- •2.1. Фундаментальные принципы управления

- •2.2. Основные виды сау

- •Глава 3. Режимы работы сау

- •3.1. Статические режимы работы сау

- •3.1.1. Статические характеристики

- •3.1.2. Статическое и астатическое регулирование

- •3.2. Динамический режим сау

- •3.2.1. Уравнение динамики сау

- •3.2.2. Передаточная функция

- •3.2.3. Элементарные динамические звенья

- •3.3. Структурные схемы в сау

- •Глава 4. Временные характеристики сау

- •4.1. Понятие временных характеристик

- •4.2. Переходные характеристики элементарных звеньев

- •4.2.1. Безынерционное (пропорциональное, усилительное) звено

- •4.2.2. Интегрирующее (астатическое) звено

- •4.2.3. Инерционное звено первого порядка (апериодическое)

- •4.2.4. Инерционные звенья второго порядка

- •4.2.5. Дифференцирующее звено

- •4.2.6. Запаздывающее (чистого или транспортного запаздывания) звено

- •Глава 5. Частотные характеристики сау

- •5.1. Понятие частотных характеристик

- •5.2. Частотные характеристики типовых звеньев

- •5.2.1. Безынерционное звено

- •5.2.2. Интегрирующее звено

- •5.2.3. Апериодическое звено

- •5.2.4. Правила построения чх элементарных звеньев

- •5.3. Частотные характеристики разомкнутых одноконтурных сау

- •Глава 6. Законы регулирования и качество сар

- •6.1. Характеристики объекта управления

- •6.2. Законы регулирования

- •6.3. Понятие устойчивости системы

- •6.4. Основные условия устойчивости

- •6.5 Частотные критерии устойчивости сау

- •6.6 Качество регулирования сау

- •6.7 Синтез и коррекция сар

- •Часть 2. Технические средства автоматики

- •Глава 7. Элементная база устройств автоматики

- •7.1. Элементная база автоматики

- •7.2. Аналоговые схемы устройств автоматики

- •Глава 8. Цифровые схемы автоматики

- •8.1. Комбинационная логика

- •8.2. Элементы комбинационных логических устройств

- •8.3. Цифровые автоматы

- •Глава 9. Датчики параметров технологического процесса

- •9.1. Характеристики датчиков

- •9.2. Чувствительные элементы датчиков

- •9.2.1. Механические чувствительные элементы датчиков

- •9.2.2. Потенциометрические чувствительные элементы

- •9.2.3. Тензочувствительные элементы

- •9.2.4. Индуктивные чувствительные элементы

- •9.2.5. Индукционные чувствительные элементы

- •9.2.6. Емкостные чувствительные элементы

- •9.2.7. Пьезоэлектрические чувствительные элементы

- •9.2.7. Фотоэлектрические чувствительные элементы

- •9.2.8. Элементы, чувствительные к температуре

- •Глава 10. Принципиальные схемы датчиков

- •10.1. Датчики температуры

- •10.2. Датчики перемещений

- •10.3. Термоанемометр постоянной температуры

- •10.4. Датчик давления с ёмкостным преобразователем

- •10.5. Датчик влажности газов

- •10.6. Датчики, использующие фотоэлектрические элементы

- •Глава 11. Задающие, сравнивающие и усилительные устройства сар

- •11.1. Задающие устройства

- •11.2. Сравнивающие устройства

- •11.3. Усилители

- •Глава 12. Исполнительные устройства автоматики

- •Глава 13. Микропроцессорные средства и их использование в автоматике

- •13.1. Базовые средства микропроцессорной техники

- •13.2. Системы сбора информации с датчиков на базе микроЭвм

- •Глава 14. Программируемые регуляторы

- •Список терминов

- •- Преобразования

- •Список используемой литературы

- •Мичуринский государственный аграрный университет

- •393760, Тамбовская обл., г.Мичуринск, ул. Интернациональная, 101,

- •Лабораторный Практикум

- •«Автоматика»

- •110302 « Электрификация и автоматизация сельского хозяйства»,

- •110303 – «Механизация переработки сельскохозяйственной продукции»,

- •110304 – «Технология обслуживания и ремонта машин в апк»

- •Рецензент:

- •Содержание

- •Общие сведения

- •Выпрямительный диод

- •Стабилитрон

- •Полупроводниковые выпрямители

- •3. Описание лабораторного стенда

- •4. Рабочее задание

- •5. Контрольные вопросы

- •Рабочая точка транзисторного каскада

- •Работа транзисторного каскада в режиме малого сигнала

- •3. Описание лабораторного стенда

- •4. Рабочее задание

- •5. Контрольные вопросы

- •Схемы с оу, охваченные обратной связью

- •Инвертирующий усилитель

- •Неинвертирующий усилитель

- •Дифференциальный усилитель

- •Суммирующая схема

- •Интегрирующая схема

- •Дифференцирующая схема

- •3. Описание лабораторного стенда

- •4. Рабочее задание

- •5. Контрольные вопросы

- •Однопороговый компаратор

- •Гистерезисный компаратор

- •3. Описание лабораторного стенда

- •4. Рабочее задание

- •5. Контрольные вопросы

- •Лабораторная работа №5 Исследование цифровых систем

- •1. Цель работы

- •Сведения необходимые для выполнения работы

- •Логические элементы

- •Дешифраторы

- •Мультиплексоры

- •Триггеры

- •Счетчики

- •3. Рабочее задание

- •4. Контрольные вопросы

- •Литература

- •Методические указания по выполнению лабораторных работ

- •Цель работы

- •Общие сведения

- •Описание лабораторного стенда

- •Указания по выполнению работы

- •Содержание отчета

- •Цель работы

- •Оборудование и приборы лабораторного стенда

- •Общие сведения

- •Указания по выполнении работы

- •Содержание отчета

- •Рекомендуемая литература

- •Контрольные вопросы

- •Цель работы

- •Общие понятия

- •Оборудование и приборы лабораторного стенда

- •Указания по выполнению работы

- •Содержание отчета

- •Рекомендуемая литература

- •Контрольные вопросы

- •Цель работы

- •Общие сведения

- •Оборудование и приборы лабораторного стенда

- •Указания по выполнению работы

- •Рекомендуемая литература

- •Контрольные вопросы

- •Цель работы

- •Общие сведения

- •Описание лабораторного стенда

- •Указания и порядок выполнения работы

- •Содержание отчета

- •Рекомендуемая литература

- •Контрольные вопросы

- •Практикум по основам автоматики

- •110302 « Электрификация и автоматизация сельского хозяйства»,

- •110303 – «Механизация переработки сельскохозяйственной продукции»,

- •110304 – «Технология обслуживания и ремонта машин в апк»

- •Рецензент:

- •Содержание

- •Выбор варианта задания

- •1. Преобразователи и усилители электрических сигналов

- •2. Исполнительные устройства и электропривод

- •Автоматика

- •Рецензент:

- •1. Цели и задачи курса

- •2. Объем и содержание курса

- •3. Вопросы контрольного задания

- •Номера вопросов контрольного задания.

- •4. Выполнение контрольного задания

- •5. Литература

Глава 8. Цифровые схемы автоматики

8.1. Комбинационная логика

В устройствах автоматики с логическими входными сигналами часто необходимо вырабатывать определенные выходные сигналы для их передачи на последующие узлы. При этом различают два класса задач.

В задачах первого класса состояние выхода зависит от комбинации входных сигналов. Эти задачи называются комбинационными и решаются с помощью логических устройств, которые выполняют операции булевой алгебры в сисГлавах с двумя состояниями.

Другой класс задач требует не только формирования комбинации входных сигналов, но также знания их прежнего значения. Для решения таких задач применяют последовательные схемы (цифровые автоматы), имеющие в той или иной форме цифровую память.

Комбинационными устройствами называют логические устройства, не имеющие в своём составе запоминающих ячеек, при этом выходные сигналы зависят от входных, имеющих место только в данный момент времени.

Все цифровые устройства оперируют двоичными кодами, т.е. наборами нулей и единиц. Для описания цифровых устройств используется алгебра логики, в которой так же, как и в двоичном кодировании, переменные могут принимать только два значения: 0 или 1. В алгебре логики имеется три элементарных действия: дизъюнкция (ИЛИ), конъюнкция (И) и инверсия (НЕ).

Дизъюнкция, или логическое сложение, осуществляется по следующим правилам:

0 V 0 = 0,

0 V 1 = 1,

1 V 0 = 1,

1 V 1 = 1,

где V - знак операции дизъюнкции.

Можно также пользоваться знаком “+”, но в логических выражениях этот знак читается как ИЛИ. В дизъюнкции в отличие от двоичного кодирования при суммировании двух логических единиц переносов не осуществляется.

Конъюнкция, или логическое умножение, осуществляется по следующим правилам:

0 0 = 0,

0 1 = 0,

1 0 = 0,

1 1 = 1,

где - знак операции конъюнкции. В логических выражениях допустимо также условное изображение операции конъюнкции отсутствием какого либо знака между переменными, записанными без пробела, однако читается это как И.

Инверсия представляет собой отрицание истины. Например, инверсия единицы есть нуль, а инверсия нуля есть единица. Операция инверсии обозначается прямой чертой над переменной:

![]()

(читается: не-икс, не-нуль, не-единица).

Законы алгебры логики представляют собой комбинации из дизъюнкций, конъюнкций и инверсий над логическими переменными. Возможные соотношения между ними приведены в таблице 8.1.

Законы отрицания в виде функций Пирса и Шеффера являются полными, т.е. посредством этих функций можно описать работу любого, сколь угодно сложного, логического устройства. Число различных логических функций от n переменных определяется соотношением: N =22n.

8.2. Элементы комбинационных логических устройств

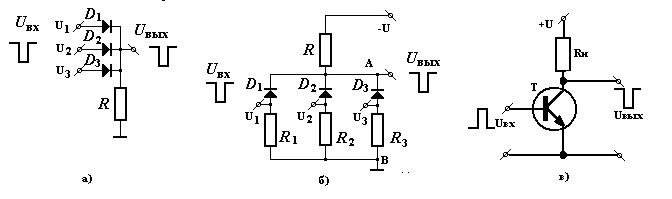

На рис.11.1а представлена схема ИЛИ, выполненная на диодах. Управляющий сигнал на выходе появляется при поступлении сигнала ИЛИ на один, ИЛИ на два других входа, одновременно или вместе.

Таблица 8.1 – Основные законы алгебры логики

№ |

Название |

Выражение |

1. |

Закон универсального множества |

1VX1VX2VX3… VXn=1 |

2. |

Закон нулевого множества |

0X1X2X3… Xn=0 |

3. |

Законы повторения |

XVXVXVX… VX=X XXXX… X=X |

4. |

Закон многократной инверсии |

|

5. |

Переместительный закон |

X1VX2=X2VX1, X1X2=X2X1 |

6. |

Сочетательный закон |

X1(X2X3)= (X1X2)X3= X2(X1X3) |

7. |

Законы дополнительности |

|

8. |

Распределительный закон |

X1X2VX3= (X1VX2)(X2 VX3) X1VX2 X3= (X1X2)V(X2 X3) |

9. |

Законы поглощения |

X1X1VX2= X1, X1X1X2= X1 |

10. |

Законы склеивания |

X1X2VX1

(X1X2)V( |

11. |

Законы отрицания: Пирса Шеффера |

|

Сигнал той же полярности появляется на выходе схемы ИЛИ в том случае, когда хотя бы на одном из входов: - ИЛИ на U1 ИЛИ на U2 ИЛИ на U3 будут логические сигналы (единицы).

На рис.8.1б приведена схема И, собранная на диодах. При поступлении сигнала только на один вход запирается соответствующий диод, а другие диоды остаются открытыми, в силу чего сопротивление между точками А и В остается малым и сигнал на выходе отсутствует. Таким образом, на выходе схемы И сигнал появится только тогда, когда на всех входах: И на U1 И на U2 И на U3 будут логические сигналы (единицы).

Логическая схема НЕ выполняется на транзисторе (рис.8.1в), или инвертирующем операционном усилителе. На выходе этой схемы сигнал инверсный тому, который присутствует на входе. Если на входе присутствует логическая единица (высокий сигнал), то на выходе - логический нуль (низкий сигнал) и наоборот.

Р ассмотренные

схемы на диодах имеют существенный

недостаток, связанный с ослаблением

сигнала при работе, что затрудняет

осуществление каскадных соединений

различных логических цепочек. От этого

недостатка свободны схемы, дополненные

транзисторами, выполняемыми по

интегральным технологиям. Современная

промышленность выпускает интегральные

логические микросхемы с широкой гаммой

логики.

ассмотренные

схемы на диодах имеют существенный

недостаток, связанный с ослаблением

сигнала при работе, что затрудняет

осуществление каскадных соединений

различных логических цепочек. От этого

недостатка свободны схемы, дополненные

транзисторами, выполняемыми по

интегральным технологиям. Современная

промышленность выпускает интегральные

логические микросхемы с широкой гаммой

логики.

Рисунок 8.1 – Исполнение логических элементов.

Для двух переменных имеют место 16 логических функций, математические соотношения и графические обозначения которых приведены в таблице 8.2.

Графическое изображение логических элементов осуществляется в виде прямоугольников, внутри которых ставятся условные символы: - элементы с выполнением операции конъюнкции, 1 - элементы с выполнением операции дизъюнкции, =1 - исключающее ИЛИ.

С левой стороны прямоугольников изображают входы, а с правой - выходы (таблица 8.2). Входы или выходы, помеченные кружочками, соответствуют инвертированию сигнала. Входы или выходы, не несущие логической информации, например, входы расширения или питания, помечают крестиком х. На основе логических элементов может быть построена электронная схема любой сложности.

Таблица 8.2 – Некоторые функции двух переменных

Логическое выражение |

Условное обозначение |

Конъюнкция Z=XY |

|

Исключающее ИЛИ Z=XY |

|

Дизъюнкция Z=XVY |

|

Функция Пирса

|

|

Логическая равнозначность

|

|

Инверсия

|

|

Функция Шеффера

|

|

Переключательной функцией в алгебре логики называют функцию, представляющую собой зависимость выходного сигнала от входных, имеющих место в данный момент времени. Для составления переключательных функций вначале составляют таблицы истинности (таблица 8.3). Столбцы в таблице истинности обозначают наименованиями входных и выходных переменных, а в строках записывают всевозможные сочетания входных и выходных сигналов в соответствии со словесным описанием алгоритма работы синтезируемых устройств.

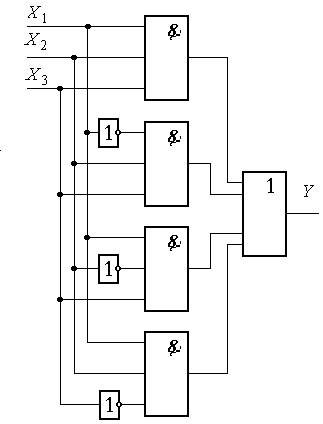

Покажем это на примере мажоритарного элемента (рис.8.2), имеющего три входа X1, X2, X3 и один выход Y. Единичный сигнал на выходе у такого элемента должен появится в том случае, если на двух или на трёх входах имеют место единичные сигналы. В противном случае на выходе должен быть нуль. Ниже представлена таблица истинности для мажоритарного элемента. На основании таблицы истинности переключательная функция может быть записана в следующем виде:

![]() .

(8.1)

.

(8.1)

Для

построения мажоритарного элемента

требуется: три инвертора для получения

инверсных сигналов

![]() четыре трёхвходовых элемента 3И и один

четырёхвходовый элемент 4ИЛИ (рис.8.2).

четыре трёхвходовых элемента 3И и один

четырёхвходовый элемент 4ИЛИ (рис.8.2).

В большинстве случаев, применяя основные законы булевой алгебры, переключательные функции удаётся минимизировать, что в свою очередь снижает аппаратные затраты на построение устройств. Так, например, применяя закон дополнительности, формулу (8.1) можно привести к следующему, более простому, виду:

![]() .

(8.2)

.

(8.2)

Для построения того же мажоритарного элемента по формуле (8.2) требуется всего три двухвходовых элемента 2И и один трёхвходовый элемент 3ИЛИ.

Минимизация логических функций осуществляется с целью снижения аппаратных затрат при построении комбинационных устройств. Основными критериями при минимизации являются: сокращение числа членов в переключательной функции, числа входов у используемых логических элементов, числа межсхемных соединений, а также числа логических операций, необходимых для выполнения функции. При минимизации результирующее действие переключательных функций сохраняется постоянным. Для целей минимизации переключательных функций, имеющих до трёх переменных, используют аналитические методы с применением основных законов алгебры логики.

Таблица 8.3 – Таблица истинности

для мажоритарного элемента

-

X1

X2

X3

Y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

Рисунок 8.2 – Мажиротарный элемент