- •1. Осн.Параметры и характеристики ис

- •11.Классификация триггеров. АсинхронныеRs-триггеры с прямыми и инверсными входами.

- •3. Структура потенциальных элементов цэвм.

- •8.И2л:осн.Хар-ки.Баз.Лог.Элемент

- •6.Кмдп: осн хар-ки. Базовый лог элем-т

- •10. Преобразователи уровней

- •18. Классификация регистров. Параллельно-последовательные регистры.

- •17.Классификация триггеров. Специализированные характеристики триггеров.

- •38.Запоминающие устр-ва(зу):классификация,прим-ие, осн.Хар-ки.

- •2. Цифр.И анал.Эвм. Классификацияэл-вЦвм

- •9. Типы выходов цифровых элементов.

- •4. Ттл: осн хар-ки. Базовый лог элем-т.

- •7. Эсл: осн хар-ки. Базовый лог элем-т

- •36.Мультиплексоры:назнач-е,осн.Схемы,применение

- •19. Классификация регистров. Параллельные

- •20. Классификация регистров. Последоват.Регистры.

- •21. Классификация счетчиков.Вычит.Асинхр.Счетчики.

- •22. Классификация счетчиков.Сумм.Асинхр.Счетчики.

- •23. Классификация счетчиков.Реверсивн.Счет-ки

- •24. Класс-ция счет-в.Недвоич.Сч-ки.Синтез недв.Сч-ков

- •25.Классификация счет-ков.Синхр.Счетчики

- •26. Классификация счетчиков. Специализированные характеристики счетчиков.

- •27.Классификация сумматоров.Одноразр.Сумматоры.

- •29)Классификация сумматоров.Парал.Сумматор с параллельным переносом.

- •28)Классификация сумматоров.Последовательный многоразрядный сумматор.

- •32.Дешифраторы:наращ-е размерности дешифраторов:

- •34. Преобразователи кодов: назначение, основные типы.

- •35.Демультиплексоры(д):назнач-е,осн.Схемы,прим-ие

- •33.Шифраторы: назначение,осн.Схемы,применение.

- •31.Дешифраторы:назначение,осн.Схемы, применение:

- •41.Запоминающие устр-ва(зу):Блочная структура

- •42.Классификация пзу.Зэ неперепрограммируемых пзу:

- •43. Классификация пзу.Зэ программируемых пзу

- •45. Классификация озу.Зэ статических озу.

- •46. Структурная схема кмоп озу

- •48.Спец.Элементы эвм:элементы задержки

- •47. Классификация озу. Зэ динамических озу.

- •49.Спец.Элементы эвм: формирователи импульсов

- •50.Спец.Элементы эвм: генераторы

1. Осн.Параметры и характеристики ис

ИС – микроэлектронное изделие, выполняющее опред. ф-цию преобразования и обработкисигнала и имеющее высокую плотность упаковки компонентов и кристаллов.

Виды:аналоговые;цифровые.

Аналоговая – ИС, предназначенная для обра-ботки и преобр. инфы, изменяющейся по закону дискретной ф-ции.Серия ИС – совокупность типов ИС, имеющих единое исполнение и предназначенных для совместного использования.Степень интеграции – кол-во эл-тов на кристалле.K=lgU – коэффициент

Основные параметры:1) мощность потребления (получается

усреднением Pмгнов за большой промежуток времени):

Pпотр = Pст + Pст + РдинРдин – мощность при перекл. из 1 в 0 (из 0 в 1).

2)уровень выходных напряжений Мвых, Мвых

3)входные токи (определяют нагрузку со стороны данной микросхемы на ист. сигнала. Наименьшее потребление тока на ИС с МДП, а наибольшее в ЭСЛ;

4)время задержки распр. сигнала (время от подачи входного

воздействия до соотв. изменения выхода микросхемы.

5. МДП: осн хар-ки. Базовый лог элем-т.

Наряду с эл-ми на БТ шир.исп.эл-ты на ПТ,кот.явл.одними из лучших для построения БИС.Наиб.распростр-е пол. МДП-тр-ры с индуц.каналом.Они бывают с каналами Р- и N-типов.В зав-cти от исп-ых тр-ров есть логика с 1 типом проводимости (МДП) и с разными типами (комплемент.логика).Лог.эл-ты на МДП тр-рах:

Тр-р VT1 вып.роль нагр. сопр-я (резистора), VT2 и

VT3 – роль «и»,т.к. соед.посл-но.Схемы на Р-канал.тр-рах

отлич. поляр-ностью напр-я Uпит,Uвх,Uвых и типами исп тр-ров.

+ выс.вх сопр-е 10^14 Ом,меньшая потребл. мощн-ть

и большая пл-ть размещ-я на крист-ле в сравнении с

ТТЛ-логикой, выс.помехоуст-сть(от 2 до 6 В). –более

выс.Uп,низк.быстр-ие,потребл-е тока.Быстрод-е на тр-рах

с N-канал. проводим-ю в 8-10 раз выше,чем с P-канал.проводим-ю. Осн серии:К580,К581,К1801(N-кан),К536(P-канал)

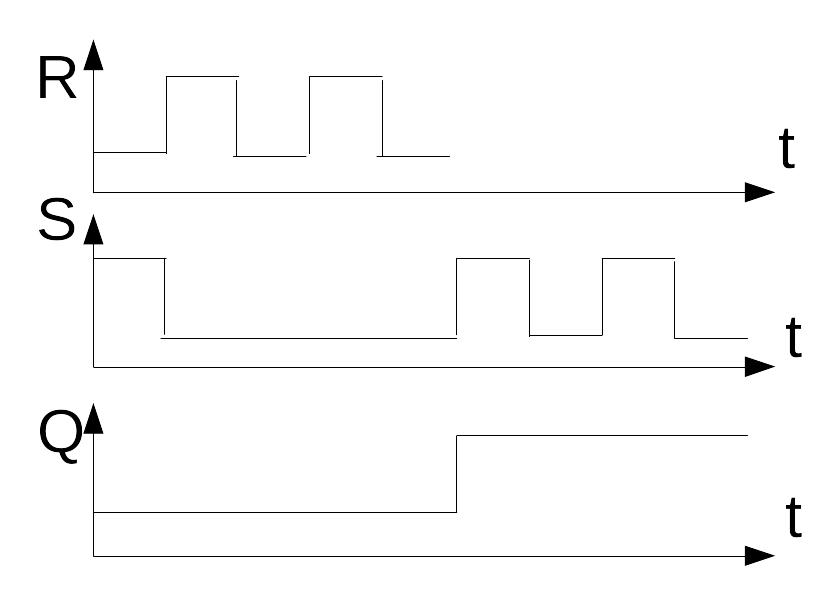

11.Классификация триггеров. АсинхронныеRs-триггеры с прямыми и инверсными входами.

Классификация триггеров см.в отд.пункте

Асинхр.триггер–простейш.тип тригг,редко исп.в кач-ве самост.эл-та.Служ.основой для постр-я слож.тригг.схем.

Асинхр.RS-триггер им.2 входа:сброс R и устновка S:

Асинхронный RS-триггер с прямыми входами:

R![]()

![]() | S

| Q

| Q

| S

| Q

| Q

1 | 0 | 0 | 1 –cброс

0 | 1 | 1 | 0 –установка

0 | 0 | Q | Q –хранение

1 | 1 | – | – –запрещ.

П осле

установки триггера в одно из сост-й

повтор.подача этой команды триггером

игнорируется,т.е.изм-ний на выходе нет.

осле

установки триггера в одно из сост-й

повтор.подача этой команды триггером

игнорируется,т.е.изм-ний на выходе нет.

для асинхр.триггера с инверс.входами все наоборот

3. Структура потенциальных элементов цэвм.

Виды пассивных связей

Отличит. особ-ть потенц.схем–наличие связи по пост.току между вых и вх цепями элем-ов,возм-тьработы в асинхр режиме(изм-е сост-я одного элем-та ведет к изм-ю сост-я связ.с ним эл-тов и т.д.по цепочке до выхода сх).Основа ИС потенц типа–схема, реализ.ф-ии Шеффера,Пирса,и-не,или-не,и-или-не,или-и-не.Внутри кажд.лог.эл-та есть каскады(участки, выполняющие

логич преобр-е сигнала) и цепи(схемы передачи сигналов

от одного каскада др.).При этом нужно усиление сигналов

во врем. согласовании и др.доп.преобр-ий.Это достиг-ся

при исп-нии транзист. схем.Такой тип схемотехники–транзист.логика.Её типы: НСТЛ–непоср.связь(пассивная связь–гальваническая связь),РСТЛ–резистивная связь (связь между точками имеет опр.сопр-ние),РКТЛ–RC связь (тут больше быстр-ие),ДТЛ (вводятся доп.диоды в схему), ТТЛ (транзист.-

транзист.логика),ТТЛШ-подвидТТЛ(со стр-рами Шоттки).