- •Полезность или бесполезность (ценность) информации.

- •Кодирование текстовой информации

- •Кодирование графической информации

- •Кодирование звуковой информации

- •1. Передача информации. Информационные каналы

- •2. Характеристики информационного канала

- •3. Абстрактный алфавит

- •4. Кодирование и декодирование

- •5. Понятие о теоремах Шеннона

- •6. Международные системы байтового кодирования

- •7. Кодирование информации

- •7.1. Двоичное кодирование текстовой информации

- •7.2. Кодирование графической информации

- •7.2.1. Кодирование растровых изображений

- •7.2.2. Кодирование векторных изображений.

- •7.3. Двоичное кодирование звука

- •4.1. Информационно-логические основы построения

- •Сумматоры: определения, классификация, уравнения, структуры и применение

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Арифметические устройства Сумматоры

- •Элементы алгебры логики

- •Элементарные логические операции. Таблицы истинности

- •Логические схемы. Булевы выражения

- •Построение таблицы истинности по булеву выражению

- •Получение булевых выражений по таблицам истинности

- •Понятие модели. Сущность метода моделирования. Основные типы моделей.

- •1. Классификация по области использования

- •2. Классификация с учетом фактора времени: статическая и динамическая модели.

- •3. Классификация по способу представления

- •4. Классификации информационных знаковых моделей: по способу реализации:

- •Тема: Общая характеристика процессов сбора, передачи и обработки информации

- •Понятие ис и ит.

- •2. Восприятие информации

- •3. Сбор информации

- •4. Передача информации

- •5. Обработка информации

- •Лекция 7 Тема: Техническая база информационной технологии

- •История развития вычислительной техники

- •Классификация эвм

- •Классификация пк

- •Архитектура эвм

- •Базовая аппаратная конфигурация пк

- •5.1 Системный блок

- •5.2 Монитор

- •5.3 Клавиатура

- •5.4 Мышь

- •Внутренняя организация микропроцессора

- •Основной цикл работы эвм

- •Система команд

- •Обработка прерываний

- •Основная память пк

- •Регистровая кэш-память

- •Периферийные устройства персонального компьютера

- •Лекция 8

- •История возникновения математической логики

- •Логические высказывания, логические операции.

- •Применение логических элементов для построения узлов эвм

- •Сумматор

- •Электронная реализация логического элемента и-не (схема на npn-транзисторах).

- •5.2. Большие эвм

- •5.3. Малые эвм

- •5.4. Персональные компьютеры

- •5.5. Суперэвм

- •5.6. Серверы

- •5.7. Переносные компьютеры

- •5.8. Тенденции развития вычислительных систем

- •6.2. Архитектура компьютерных сетей

- •6.3. Локальные вычислительные сети

- •6.4. Глобальная сеть internet

- •6.5. Локальная вычислительная сеть novell netware

- •8.1. Программные продукты и их основные характеристики

- •8.2. Классификация программных продуктов

Арифметические устройства Сумматоры

Сумматор по модулю 2 — цифровой узел с m входами и одним выходом, работающий в соответствии со следующим правилом:

сигнал 1 появляется на его выходе всякий раз, когда в наборе входных сигналов содержится нечетное число 1. Поэтому этот узел еще называют схемой проверки на четность

Условное обозначение сумматора по модулю 2 представлено на рис.1

В частном случае при числе входов, равном 2, сумматор по модулю 2 выполняет функцию логического элемента “Исключающее ИЛИ”: на выходе 1 будет только при 1 на одном из входов. Условное обозначениеэлемента “Исключающее ИЛИ” и его реализация на элементах И-НЕ представлены на

Суммирование по модулю 2, как логическая операция, очень часто встречается на практике, поэтому ей присвоено специальное обозначение +

Например, y=x1 + x2 + x3

Полусумматор — это узел, имеющий два входа и два выхода и выполняющий операцию арифметического сложения двух одноразрядных чисел А и В в соответствии со следующим правилом:

при любых наборах сигналов А и В на выходе сигнала суммы S формируется результат сложения по модулю 2, на выходе сигнала переноса Р во всех случаях будет 0, кроме А=В=1, когда Р'=1.

Таблица истинности представлена в табл. 1

А |

В |

S |

P |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

табл.1

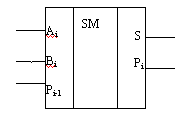

Полный одноразрядный сумматор выполняет операцию арифметического сложения двух одноразрядных чисел Ai и Bi с учетом переноса из предыдущего младшего разряда Pi-1. Он имеет три входа и два выхода для сигнала суммы Si, и сигнала переноса Рi.

и пример реализации полного сумматора представлены на рисунке

Таблица истинности для сложения двух 2-х разрядных чисел, используемая модуль с полными одноразрядными сумматорами

Входное число А |

Входное число В |

Перенос |

Сумма по разрядам |

||||

A1 |

А0 |

В1 |

B0 |

P1 |

P2 |

S1 |

S0 |

Одноразрядный субтрактор ( от английского subtract - вычитать) - это схема, выполняющая арифметическое вычитание двух бит А и В и “занимающая” бит Bii

Вычитание сводится к сложению дополнительного кода вычитаемого, т.е. отрицательного числа.

А - В = А + (-В)

Дополнительным кодом двоичного числа X в N-разрядной ячейке является число, дополняющее его до значения 2N/

Получить дополнительный код можно следующим путем

а) записать внутренне представление положительного числа X

б) инвертируется двоичный код числа (заменяем 0 на 1 и 1 на 0)

в) к полученному числу добавляем единицу

пример.

45-39

00101101 - 00100111 00000110 |

б) Инвертируем вычитаемое 11011000 в)Находим сумму вычитаемое + 1 11011000 + 1 11011001 Результат: 00101101 11011001 1 00000110 |

1 выходит за пределы 8-разрядной сетки и исчезает

"0" в старшем (8)разряде свидетельствует о знаке "+" числа:

"1" - соответствует знаку "минус"

Когда на управляющую шину подается логический 0 (Add/Ssub=0), схема производит сложение

Когда на управляющую шину подается логическая 1 (Add/Ssub=1), схема производит вычитание