- •Ответы по мпс (по Вовану – 2008-2009 уч.Г.)

- •1. Классификация микропроцессоров. Архитектуры микропроцессоров. Микропроцессорные комплекты, системы на кристалле.

- •2. Ацп. Основные характеристики, структурные схемы.

- •3. Цап. Основные характеристики, структурные схемы.

- •4. Микроконтроллеры семейства mcs51. Структура, параметры.

- •5. Микроконтроллеры семейства mcs51. Организация памяти.

- •6. Микроконтроллеры семейства mcs51. Система команд.

- •7. Микроконтроллеры avr. Структуры, параметры.

- •8. Микроконтроллеры avr. Организация памяти, внешняя память.

- •9. Микроконтроллеры avr. Система тактирования.

- •10. Микроконтроллеры avr. Организация портов ввода/вывода.

- •11. Микроконтроллеры avr. Сторожевой таймер, логика сброса.

- •12. Микроконтроллеры avr. Подсистема прерываний.

- •13. Микроконтроллеры avr. Таймеры.

- •14. Микроконтроллеры avr. Модуль захвата и сравнения, режимы шим.

- •15. Микроконтроллеры avr. Интерфейс spi.

- •16. Микроконтроллеры avr. Интерфейс usart.

- •17. Микроконтроллеры avr. Интерфейс twi.

- •18. Микроконтроллеры avr. Модуль ацп.

- •19. Микроконтроллеры avr. Система команд.

- •20. Микроконтроллеры avr. Методы адресации.

- •21. Микроконтроллеры avr. Организация интерфейса с семисегментным индикатором и матричной клавиатурой.

- •22. Ассемблер микроконтроллеров avr. Приемы программирования.

- •23. Программные и аппаратные средства разработки и отладки микропроцессорных систем.

- •24. Цифровые сигнальные процессоры, структуры, характеристики, области применения.

- •25. Цсп семейства tms320c2000. Структура, основные характеристики.

- •39. Организация интерфейса usb.

- •40. Шина isa. Организация, протокол обмена.

- •41. Шина pci. Организация, протокол обмена.

- •42. Проектирование микропроцессорных систем. Цикл проектирования.

- •43. Организация питания микропроцессорных систем. Импульсные источники питания.

3. Цап. Основные характеристики, структурные схемы.

Современные АЦП и ЦАП, как правило, представляют собой БИС, выполненные по КМОП - технологии, и требующие минимальное число дополнительных внешних элементов для выполнения своих функций.

Рассмотрим основные варианты построения ЦАП.

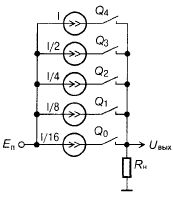

Чаще

всего используется принцип цифро-аналогового

преобразования, основанный на суммировании

токов. На рис. ниже показана структурная

схема ЦАП, содержащего b генераторов

тока, питающихся от источника напряжения

![]() ,

и Ь ключей, где b - число двоичных разрядов,

равное в данном примере 5. Величины

токов пропорциональны степеням 2. Ключ

замыкается, если соответствующий бит

Q в очередном такте

цифрового сигнала равен лог.1, и

размыкается в противоположном случае.

Суммарный ток течет через сопротивление

нагрузки

,

и Ь ключей, где b - число двоичных разрядов,

равное в данном примере 5. Величины

токов пропорциональны степеням 2. Ключ

замыкается, если соответствующий бит

Q в очередном такте

цифрового сигнала равен лог.1, и

размыкается в противоположном случае.

Суммарный ток течет через сопротивление

нагрузки

![]() и

создает выходное напряжение

и

создает выходное напряжение

![]() .

Для преобразования суммы токов в

напряжение на выходе ЦАП может быть

использован операционный усилитель.

Широко известна схема ЦАП с резистивными

цепями R-2R.

.

Для преобразования суммы токов в

напряжение на выходе ЦАП может быть

использован операционный усилитель.

Широко известна схема ЦАП с резистивными

цепями R-2R.

Достоинством ЦАП с суммированием двоично-взвешенных токов является минимальное число генераторов тока и ключей. Однако при большом числе разрядов и высокой частоте дискретизации начинает сильно сказываться недостаток таких ЦАП, который заключается в том, что одновременное переключение ключей в нескольких двоичных разрядах создает значительные помехи в выходном напряжении. Эти помехи зависят от того, какие именно ключи замыкаются или размыкаются, что создает дополнительные погрешности преобразования. Другой недостаток этого пути построения ЦАП - необходимость получения высокоточных резисторов разных номиналов, что требует сложной и дорогостоящей технологии.

Значительно

меньше указанные недостатки сказываются,

если число генераторов тока и ключей

увеличить до

![]() ,

и токи всех генераторов сделать равными

,

и токи всех генераторов сделать равными

![]() .

При подаче на вход такого ЦАП двоичного

числа К, где

.

При подаче на вход такого ЦАП двоичного

числа К, где

![]() ,

замкнется К ключей, и выходной ток будет

равен

,

замкнется К ключей, и выходной ток будет

равен

![]() .

При увеличении входного числа ключи

будут только замыкаться, а при уменьшении

- только размыкаться.

.

При увеличении входного числа ключи

будут только замыкаться, а при уменьшении

- только размыкаться.

ЦАП с суммированием двоично-взвешенных токов

ЦАП с интерполяцией (а) и с сигма-дельта модулятором (б)

Этот вариант называется ЦАП с полным декодированием или «термометр» по аналогии с термометром, содержащим столбик жидкости, который может подниматься и опускаться. Очевидно, что ЦАП с полным декодированием содержит значительно больше элементов, чем ЦАП с двоично-взвешенными токами.

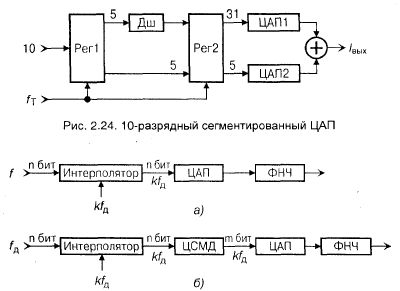

Для построения быстродействующих ЦАП с большим числом разрядов квантования используются структурные схемы с разделением на сегменты. Пример 10-разрядного ЦАП такого типа показан на рис. 2.24. На этом рисунке жирными стрелками показаны цифровые шины, рядом с которыми написано число разрядов в них.

Входной

10-разрядный код фиксируется в регистре

Рег1 по импульсам тактовой частоты![]() .

Затем 5 старших разрядов преобразуются

дешифратором Дш в 31-разрядный код.

Используется закон преобразования

«термометр»: если на входе дешифратора

число N (в двоичной записи), то на выходах

N младших разрядов Дш единицы, а на

остальных выходах - нули. Коды с выхода

Дш вместе с 5 младшими разрядами входного

кода запоминается в 36-разрядном регистре

Рег2. Полученный 31-разрядный код далее

поступает на ЦАП1, содержащий 31 генератор

тока одинаковой величины и 31 ключ.

Младшие 5 разрядов поступают на ЦАП2,

построенный по принципу суммирования

двоично-взвешенных токов. Помехи,

возникающие в ЦАП1 и ЦАП2 при переключениях,

оказываются незначительными, так как

коммутируются небольшие токи. Токи

ЦАП1 и ЦАП2 суммируются и образуют

выходной ток.

.

Затем 5 старших разрядов преобразуются

дешифратором Дш в 31-разрядный код.

Используется закон преобразования

«термометр»: если на входе дешифратора

число N (в двоичной записи), то на выходах

N младших разрядов Дш единицы, а на

остальных выходах - нули. Коды с выхода

Дш вместе с 5 младшими разрядами входного

кода запоминается в 36-разрядном регистре

Рег2. Полученный 31-разрядный код далее

поступает на ЦАП1, содержащий 31 генератор

тока одинаковой величины и 31 ключ.

Младшие 5 разрядов поступают на ЦАП2,

построенный по принципу суммирования

двоично-взвешенных токов. Помехи,

возникающие в ЦАП1 и ЦАП2 при переключениях,

оказываются незначительными, так как

коммутируются небольшие токи. Токи

ЦАП1 и ЦАП2 суммируются и образуют

выходной ток.

При цифро-аналоговом преобразовании звуковых сигналов, как пояснялось в предыдущем параграфе, используют повышение частоты дискретизации и интерполяцию. Для этого имеются специальные ЦАП (рис. 2.25,а). Интерполятор представляет собой цифровое устройство, в котором в промежутке между каждыми двумя отсчетами входного цифрового сигнала вставляется к-1 новых отсчетов, рассчитываемых по определенным правилам. В результате частота дискретизации увеличивается в к раз. Затем сигнал преобразуется n-разрядным ЦАП в аналоговую форму и фильтруется ФНЧ.

Наибольшее число разрядов квантования обеспечивается в ЦАП с сигма-дельта модулятором (рис. 2.25,б). Интерполятор повышает частоту дискретизации в к раз. Цифровой сигма-дельта модулятор преобразует n-разрядные двоичные слова в m-разрядные (т<n) слова, которые преобразуются m-разрядным ЦАП в аналоговый сигнал, сглаживаемый ФНЧ. Сигма-дельта модулятор формирует m-разрядные слова так, чтобы в результате усреднения нескольких отсчетов, идущих с увеличенной частотой дискретизации, получалось требуемое значение выходного аналогового сигнала. Чем меньше т по сравнению с л, тем больше должно быть число к, показывающее во сколько раз увеличивается частота дискретизации. В предельном случае может быть т = 1. При этом выходное напряжение получается сглаживанием последовательности импульсов, как в устройствах с широтно-импульсной или частотно-импульсной модуляцией.