- •1. Определение элементов, узлов и устройств эвм.

- •2. Классификация элементов эвм.

- •3. Соглашение Положительной и Отрицательной Логики.

- •4. Требования к Системе Элементов.

- •5.Основные параметры элементов эвм.

- •6.Основные характеристики элементов эвм

- •7.Логические элементы эвм

- •8.Логические Элементы эвм с ок. Достоинства. Недостатки. Применение.

- •9.Логические Элементы эвм с тремя состояниями. Достоинства. Недостатки. Применение.

- •10.Приемопередатчики.

- •11.Базовые элементы кмоп. Двунаправленный ключ. Стоковая и передат. Хр-ки. Соглос. Кмоп и ттл.

- •12.Триггеры. Структурная схема. Классификация.

- •13.Асинхронные и синхронные rs триггеры.

- •14.Синхронные d-триггеры со статическим управлением записи. Синтез.

- •15. Асинхронные и синхронные jk-Триггеры. Синтез.

- •16. Синхронный rs Триггер с 2-х ступенчатым запоминанием информации.

- •17. Синхронные jk Триггеры с 2-х ступенчатым запоминанием информации.

- •18. Синхронные dv Триггеры с 2-х ступенчатым запоминанием информации.

- •20. Синхронный d-триггер с динамическим управлением записью.

- •21. Синхронный jk-триггер с динамическим управлением записью.

- •22. Регистры. Классификация. Основные параметры.

- •23.Регистры памяти (параллельные регистры на d и rs триггерах).

- •24.Регистры Сдвига на d-триггерах.

- •25. Синтез универсального регистра. Анализ функционирования.

- •26. Синтез реверсивного регистра сдвига с параллельной синхронной загрузкой.

- •27. Реверсивный регистр сдвига с асинхронной загрузкой и установкой в «0».

- •28. Счётчики. Классификация. Основные параметры. Оценка быстродействия.

- •29. Асинхронные двоичные счётчики. С параллельным переносом. Со сквозным переносом.

- •32.Реверсивные двоичные асинхронные счетчики. Синтез.

- •33. Асинхронные десятичный счетчики. Синтез.

- •34. Методика синтеза синхронных счетчиков. Суммирующий двоичный синхр счетчик.

- •36. Вычитающие двоичные синхронные счетчики.

- •37. Реверсивные двоичные синхронные счетчики.

- •38. Синхронный десятичный счётчик.Вычитающий десятичный счетик

- •40. Синхронный реверсивный десятичный счётчик. Синтез

- •47.Наращивание разрядности регистров и счетчиков.

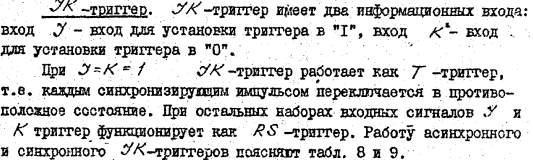

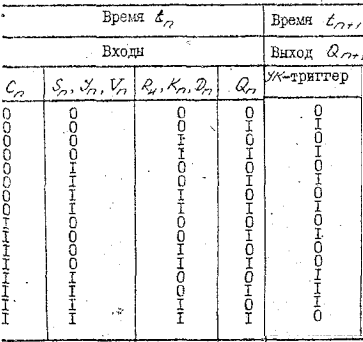

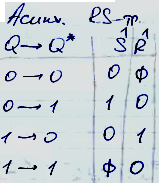

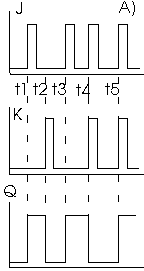

15. Асинхронные и синхронные jk-Триггеры. Синтез.

Триггер – устройство с двумя устойчивыми состояниями выхода, содержащее запоминающую ячейку (ЗЯ) и схему управления (СУ), преобразующую поступающую информацию в комбинацию сигналов, действующих непосредственно на входы ЗЯ.

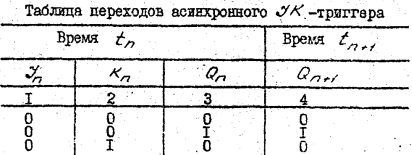

-Асинхронный JK-триггер.

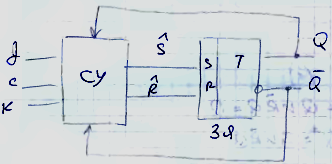

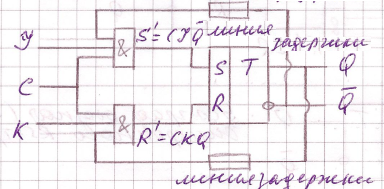

Синхронный JK-триггер.

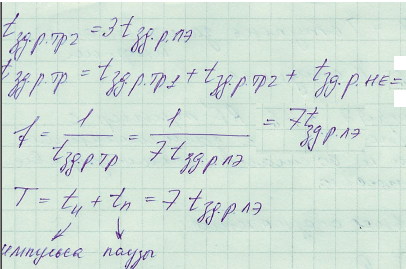

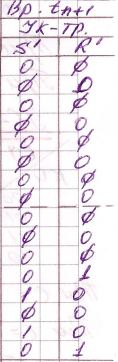

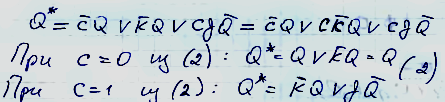

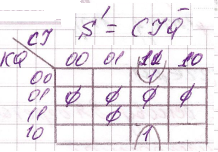

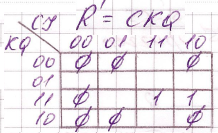

Структурный синтез синхронного JK-триггера:

М

атрица

перехода для асинхронного RS

триггера

атрица

перехода для асинхронного RS

триггера

-![]() схема

может работать только при этом условии

схема

может работать только при этом условии

Решение проблемы с линией задержки и tи:

- применять их

для асинхронного----------------

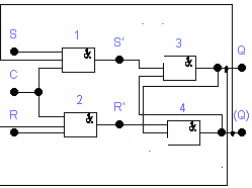

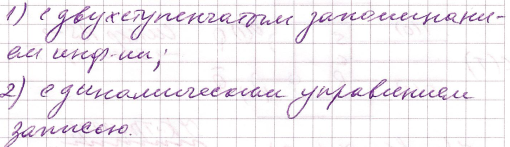

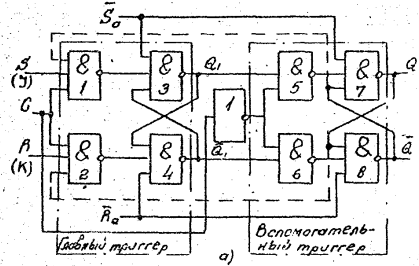

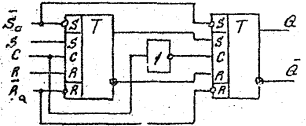

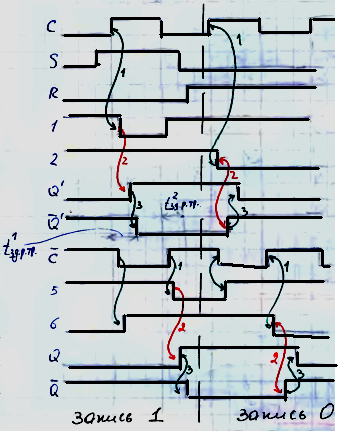

16. Синхронный rs Триггер с 2-х ступенчатым запоминанием информации.

Триггер – устройство с двумя устойчивыми состояниями выхода, содержащее запоминающую ячейку (ЗЯ) и схему управления (СУ), преобразующую поступающую информацию в комбинацию сигналов, действующих непосредственно на входы ЗЯ.

В двухступенчатых триггерах входная и выходная ступени тактируются «антисинхронно», прием информации разрешается в них поочередно. Вследствие этого отсутствует режим прозрачности триггера при любом уровне синхросигнала, что позволяет реализовать любые типы триггеров, свободные от режимов генерации, и дает возможность построения си7хронных автоматов без опасных временных состязаний. Однако, их схемы более сложные, чем с динамическим входом, а быстродействие несколько ниже.

Триггер имеет две ступени запоминания информации: главная и вспомогательная (Master and Slave)

При С=1 разрешается запись информации с инфо. входов триггера в 1-ю ступень и запрещает копирование с 1й ступени на 2ю. При C=0 наоборот, при этом первая ступень в режиме хранения..

2я ступень- выходная и м.б. выполнена RS, либо D-триггером (D-тр д.б. со статич управлением записью).

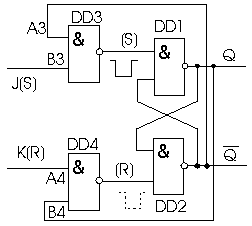

В JK-триггере 1я ступень имеет входы, на которые подаются сигналы ОС (с выхода 2й ступени),и в качестве 2й ступени используется RS-триггер, имеющий два входа R и два входа S.

Двухступенчатые триггеры строятся несколькими способами: с инвертором, с разнополярным управлением ступенями, с запрещающими связями. В данном случае обе ступени – синхронные RS-триггеры.

MS-триггера (триггер типа Flip-Flop)

M – Master, S- Slave.

При С=0 перепись информации из первой ступени во вторую и перевод первой ступени в режим хранения. При С=1 разрешена запись в первую ступень и запрещена перепись из первой ступени во вторую.

С У-

схемы управления

У-

схемы управления

Л Э

1-4 – синхронный RS

триггер (M-ступень)

1-2-СУ. 3-4- ЗЯ

Э

1-4 – синхронный RS

триггер (M-ступень)

1-2-СУ. 3-4- ЗЯ

Л Э

5-8 – синхронный RS

триггер (S-ступень)

5-6 -СУ. 7-8 - ЗЯ

Э

5-8 – синхронный RS

триггер (S-ступень)

5-6 -СУ. 7-8 - ЗЯ

ч то

пунктиром – то не надо рисовать!

то

пунктиром – то не надо рисовать!