- •1. Определение элементов, узлов и устройств эвм.

- •2. Классификация элементов эвм.

- •3. Соглашение Положительной и Отрицательной Логики.

- •4. Требования к Системе Элементов.

- •5.Основные параметры элементов эвм.

- •6.Основные характеристики элементов эвм

- •7.Логические элементы эвм

- •8.Логические Элементы эвм с ок. Достоинства. Недостатки. Применение.

- •9.Логические Элементы эвм с тремя состояниями. Достоинства. Недостатки. Применение.

- •10.Приемопередатчики.

- •11.Базовые элементы кмоп. Двунаправленный ключ. Стоковая и передат. Хр-ки. Соглос. Кмоп и ттл.

- •12.Триггеры. Структурная схема. Классификация.

- •13.Асинхронные и синхронные rs триггеры.

- •14.Синхронные d-триггеры со статическим управлением записи. Синтез.

- •15. Асинхронные и синхронные jk-Триггеры. Синтез.

- •16. Синхронный rs Триггер с 2-х ступенчатым запоминанием информации.

- •17. Синхронные jk Триггеры с 2-х ступенчатым запоминанием информации.

- •18. Синхронные dv Триггеры с 2-х ступенчатым запоминанием информации.

- •20. Синхронный d-триггер с динамическим управлением записью.

- •21. Синхронный jk-триггер с динамическим управлением записью.

- •22. Регистры. Классификация. Основные параметры.

- •23.Регистры памяти (параллельные регистры на d и rs триггерах).

- •24.Регистры Сдвига на d-триггерах.

- •25. Синтез универсального регистра. Анализ функционирования.

- •26. Синтез реверсивного регистра сдвига с параллельной синхронной загрузкой.

- •27. Реверсивный регистр сдвига с асинхронной загрузкой и установкой в «0».

- •28. Счётчики. Классификация. Основные параметры. Оценка быстродействия.

- •29. Асинхронные двоичные счётчики. С параллельным переносом. Со сквозным переносом.

- •32.Реверсивные двоичные асинхронные счетчики. Синтез.

- •33. Асинхронные десятичный счетчики. Синтез.

- •34. Методика синтеза синхронных счетчиков. Суммирующий двоичный синхр счетчик.

- •36. Вычитающие двоичные синхронные счетчики.

- •37. Реверсивные двоичные синхронные счетчики.

- •38. Синхронный десятичный счётчик.Вычитающий десятичный счетик

- •40. Синхронный реверсивный десятичный счётчик. Синтез

- •47.Наращивание разрядности регистров и счетчиков.

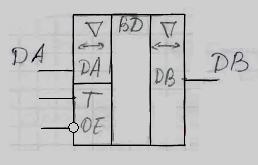

10.Приемопередатчики.

Приёмопередатчик служит для двунаправленной передачи информации.Приемопередатчик – двунаправленный эл-т

Для реализации используются элементы с откр. коллектр. и состоянием Z.

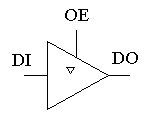

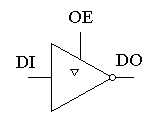

ЛЭ с ОК и 3 СВ. Любой ЛЭ с повышенной способностью называется буфером или драйвером. ЛЭ, имеющий вход разрешения и реализацию с ОК и 3 СВ и облад-ие повышенной напр способностью способны работать на шину данных и называется шинным формир-ем или шинным драйвером. BD-(Bus Driver – шинный драйвер. Передча инф-ии через двунапр-ую шину используется ЛЭ с ОК и 3 СВ .используется режим разделения времени. Двунаправленные драйверы ЛЭ способны передавать сигнал в двух направлениях . Драйверы работают на длинную линию ,нест. нагрузку.

Западное

обозначение драйверов. Если

информация передается справа налево,

снизу вверх, то надо рисовать стрелки.

Западное

обозначение драйверов. Если

информация передается справа налево,

снизу вверх, то надо рисовать стрелки.

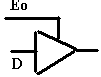

На открытый окрытый коллектор

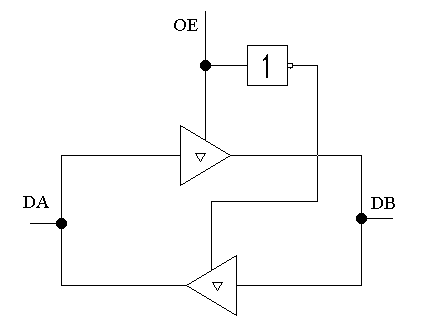

Если двунаправленный:

Противофазное управление:

OE=1: A->B

OE=0: B->A (рисунок слева)

(только на рисунке – EO дб)

Схема, имеющая вход разрешения передачи и изменения. направл. передачи:

Пример: АП6 – управляющие сигналы T (направление передачи), OE.

Передача при EO=0

если T=1 -> y1=1,y2=0 открыт 1 DB=DA

если T=0 -> y1=0,y2=1 открыт 2 DB=DA

EO=1

y1=y2=0; 1,2-закрыты->линия разомкнута.

y1 и y2 – это выходы 3 и 4 соответсвенно

T |

OE |

Напр-ие пер-чи |

Примеч. |

|

0 |

0 |

DA->DB |

DA - вход |

|

1 |

0 |

DB->DA |

DB – вход |

|

x |

1 |

DA=DB=Z |

|

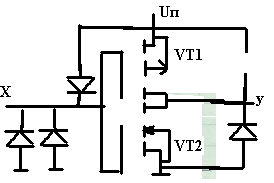

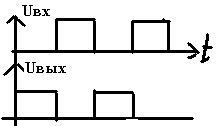

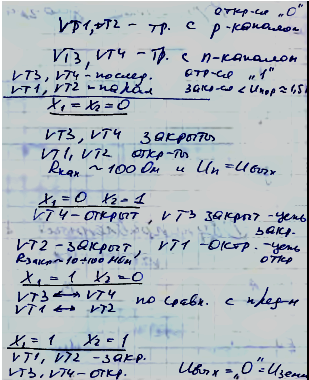

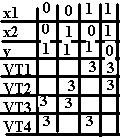

11.Базовые элементы кмоп. Двунаправленный ключ. Стоковая и передат. Хр-ки. Соглос. Кмоп и ттл.

1)Особенность К-МОП ИМС в том, что триг-ры управляются напряжением => Rвх->беск,Iвх->0.

В связи с этим нагрузочная способность 20-50, быстродей-ие определ. допустимым tзад.расп. 2) В стат. режиме потребляемая мощность ->0. 3) быстродействие зависит от Uп.

Недостатки:

1)чувст. к стат. эл-ву. 2)=>обеспеч режима работы 3)эффект зацикливания.(из-за наличия паразитных биполярных транзисторов, образ тиристоры.

Сток может выполнять функцию истока и наоборот.

1. НЕ

V T1

–c

каналом p-типа.

VT2

– c каналом

n

типа

T1

–c

каналом p-типа.

VT2

– c каналом

n

типа

2

.

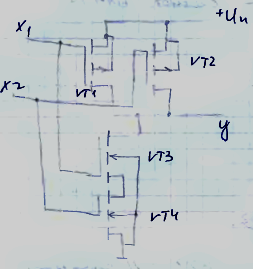

И-НЕ

.

И-НЕ

Ч тобы

открыть оба нижних транзистора надо,

чтобы на входе A и входе B была логическая

единица, при этом оба верхних транзистора

закроются и на выходе Q будет логический

ноль. Если хотя бы на одном или на обоих

входах будет логический ноль, то хотя

бы один из нижних транзисторов закроется,

один из верхних откроется, при этом на

выходе будет логическая единица.

тобы

открыть оба нижних транзистора надо,

чтобы на входе A и входе B была логическая

единица, при этом оба верхних транзистора

закроются и на выходе Q будет логический

ноль. Если хотя бы на одном или на обоих

входах будет логический ноль, то хотя

бы один из нижних транзисторов закроется,

один из верхних откроется, при этом на

выходе будет логическая единица.

3 .

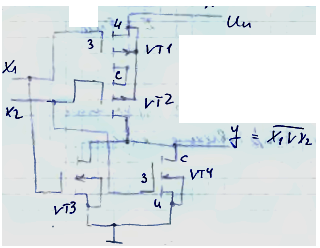

ИЛИ-НЕ

.

ИЛИ-НЕ

V T1

и VT2

– последовательно. VT3||VT4

T1

и VT2

– последовательно. VT3||VT4

Если на входах A или B (или на обоих) логическая единица, то откроется один или оба из нижних транзисторов, при этом закроется один или оба верхних транзистора, тогда на выходе логический ноль. Если на обоих входах логический ноль, то закроются оба нижних и откроются оба верхних транзистора, при этом на выходе логическая единица.

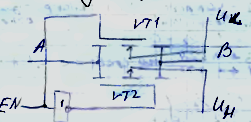

Двунаправленный ключ.

V T1

– n

канальный. VT2

– p

канальный.

T1

– n

канальный. VT2

– p

канальный.

Диапазон переключений сигналов от – Uп до +Uп. Управление сигналом EN. Схема открыта, если EN=1.Сигнал может подаваться и сниматься с любого входа (A,B) Может получать как аналогов. так и цифровые сигналы

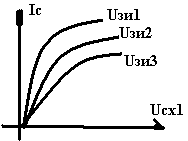

Стоковая хар-ка:

S-

крутизна.

S-

крутизна.

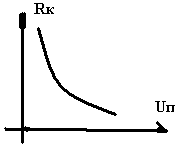

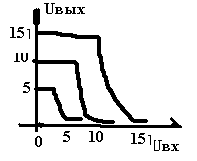

Передаточные характеристики:

Совмещение КМОП и ТТЛ:

1)Преобразователь уровня

2)инверторы

3)спец. серии

Обозначение

Обозначение